SPI Registers

www.ti.com

572

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

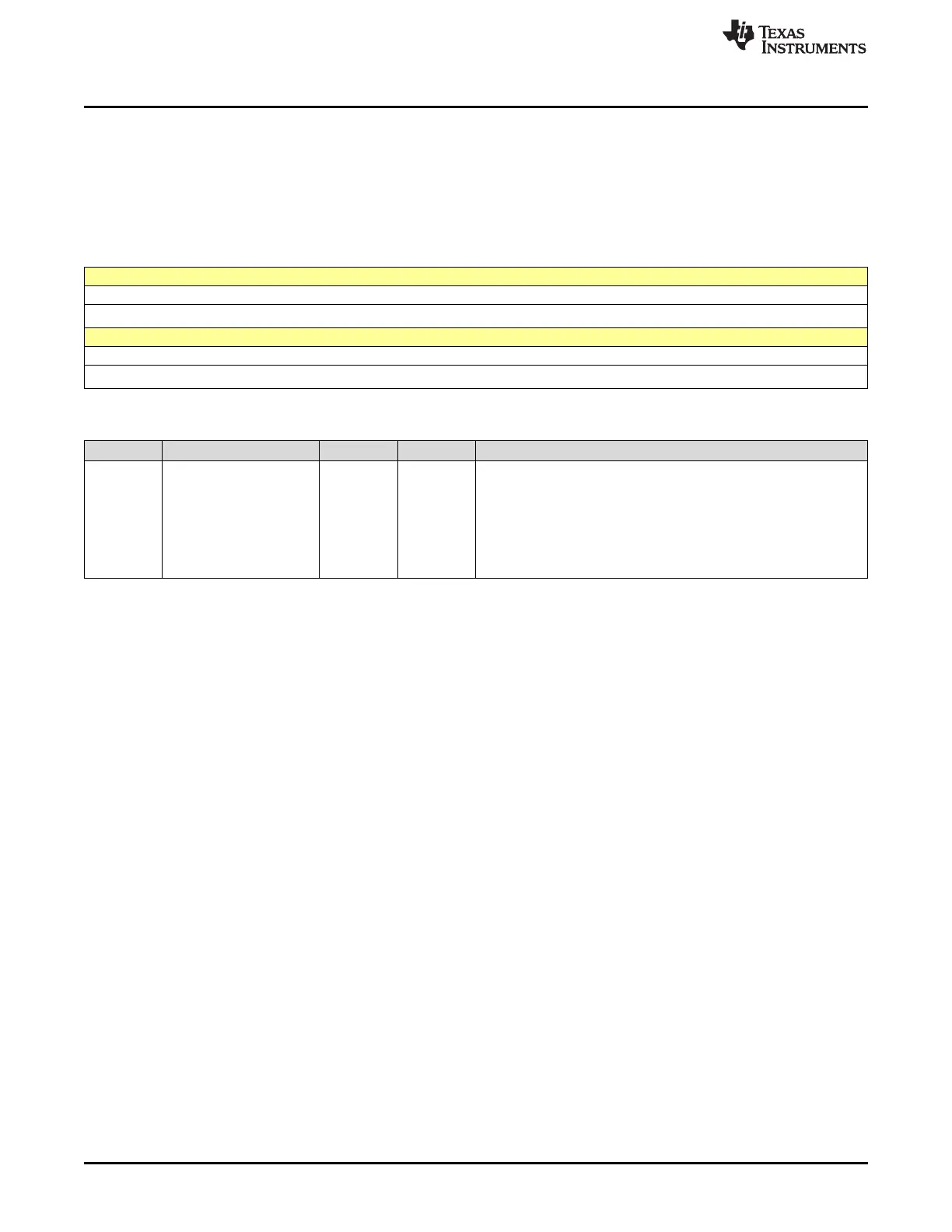

9.5.2.6 SPIRXBUF Register (Offset = 7h) [reset = 0h]

SPIRXBUF is shown in Figure 9-13 and described in Table 9-12.

Return to the Summary Table.

SPIRXBUF contains the received data. Reading SPIRXBUF clears the SPI INT FLAG bit in SPISTS. If

FIFO mode is enabled, reading this register will also decrement the RXFFST counter in SPIFFRX.

Figure 9-13. SPIRXBUF Register

15 14 13 12 11 10 9 8

RXBn

R-0h

7 6 5 4 3 2 1 0

RXBn

R-0h

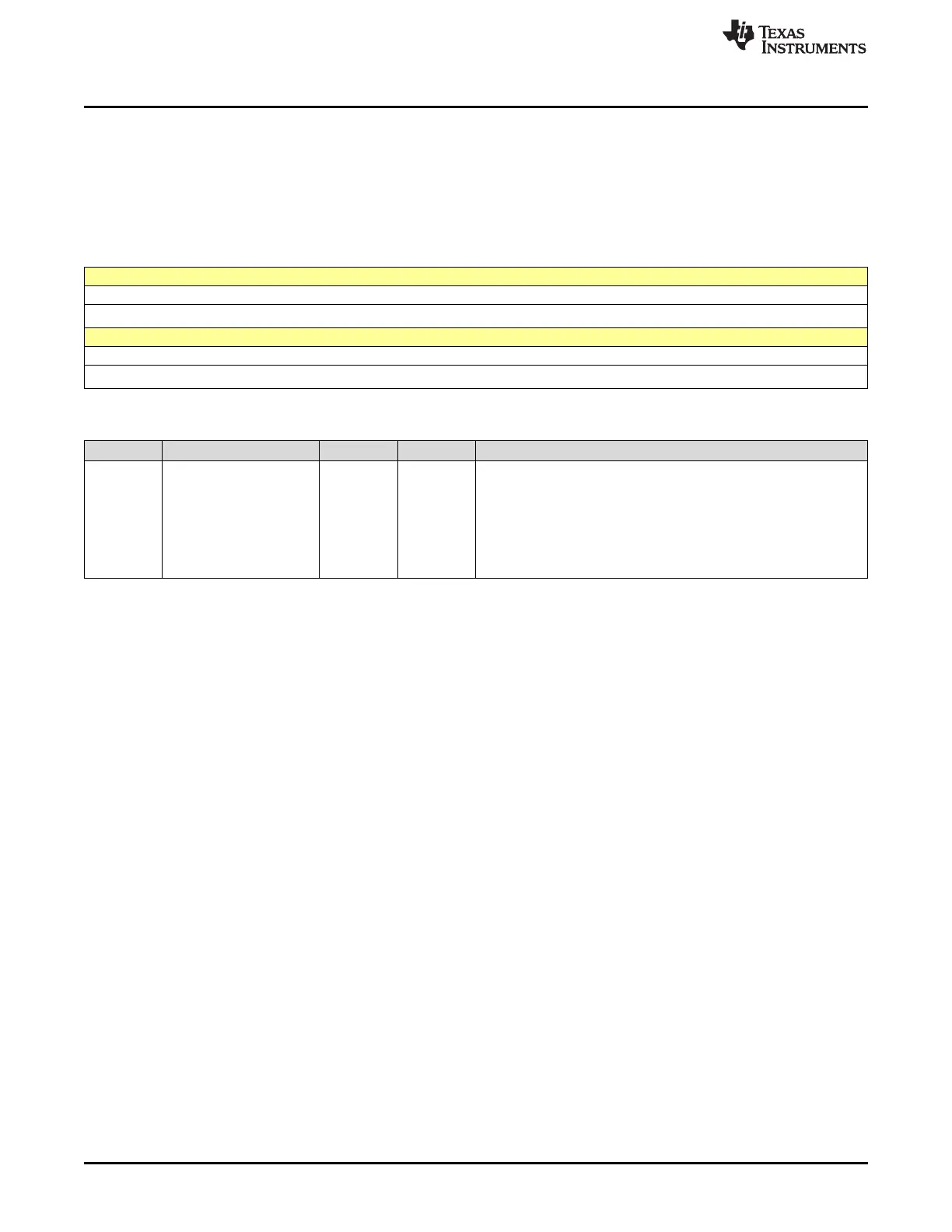

Table 9-12. SPIRXBUF Register Field Descriptions

Bit Field Type Reset Description

15-0 RXBn R 0h

Received Data

Once SPIDAT has received the complete character, the character is

transferred to SPIRXBUF, where it can be read. At the same time,

the SPI INT FLAG bit (SPISTS.6) is set. Since data is shifted into the

SPI's most significant bit first, it is stored right-justified in this

register.

Reset type: SYSRSn

Loading...

Loading...