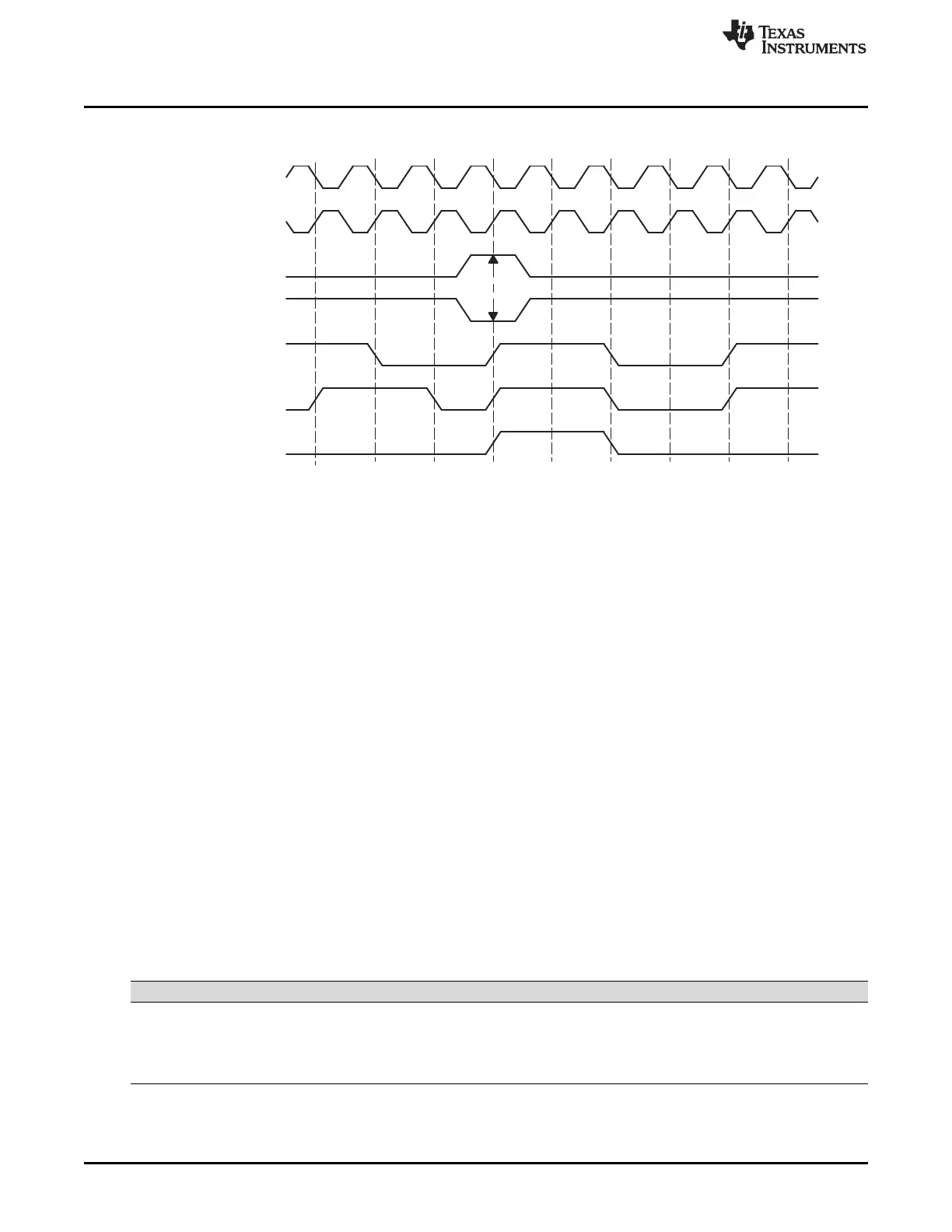

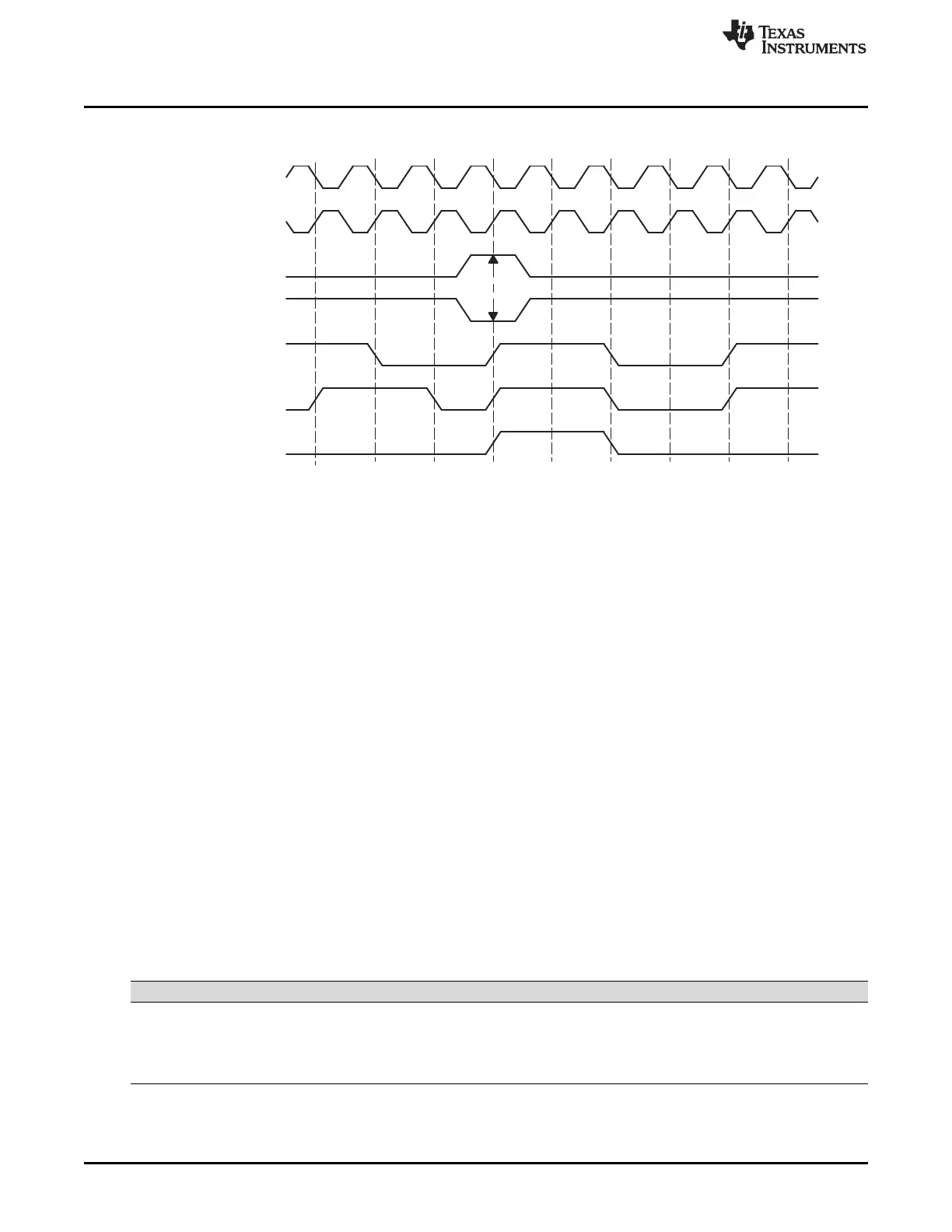

FSG

(Needs resynchronization)

CLKG

resynchronize)

(No need to

CLKG

(FSRP=1)

FSR external

(FSRP=0)

FSR external

CLKR

CLKR

McBSP Sample Rate Generator

www.ti.com

676

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

Figure 12-20. CLKG Synchronization and FSG Generation When GSYNC = 1 and CLKGDV = 3

12.4.4 Reset and Initialization Procedure for the Sample Rate Generator

To reset and initialize the sample rate generator:

Step 1. Place the McBSP/sample rate generator in reset.

During a DSP reset, the sample rate generator, the receiver, and the transmitter reset bits (GRST,

RRST, and XRST) are automatically forced to 0. Otherwise, during normal operation, the sample rate

generator can be reset by seting GRST = 0 in SPCR2, provided that CLKG and/or FSG is not used by

any portion of the McBSP. Depending on your system you may also want to reset the receiver (RRST

= 0 in SPCR1) and reset the transmitter (XRST = 0 in SPCR2).

If GRST = 0 due to a device reset, CLKG is driven by the CPU clock divided by 2, and FSG is driven

inactive-low. If GRST = 0 due to program code, CLKG and FSG are driven low (inactive).

Step 2. Program the registers that affect the sample rate generator.

Program the sample rate generator registers (SRGR1 and SRGR2) as required for your application. If

necessary, other control registers can be loaded with desired values, provided the respective portion of

the McBSP (the receiver or transmitter) is in reset.

After the sample rate generator registers are programmed, wait 2 CLKSRG cycles. This ensures

proper synchronization internally.

Step 3. Enable the sample rate generator (take it out of reset).

In SPCR2, make GRST = 1 to enable the sample rate generator.

After the sample rate generator is enabled, wait two CLKG cycles for the sample rate generator logic to

stabilize.

On the next rising edge of CLKSRG, CLKG transitions to 1 and starts clocking with a frequency equal

to the CLKG Frequency equation below.

Table 12-7. Input Clock Selection for Sample Rate Generator

SCLKME CLKSM Input Clock for Sample Rate Generator

0 0 Reserved

0 1 LSPCLK

1 0 Signal on MCLKR pin

1 1 Signal on MCLKX pin

Loading...

Loading...