www.ti.com

Clocking and System Control

79

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

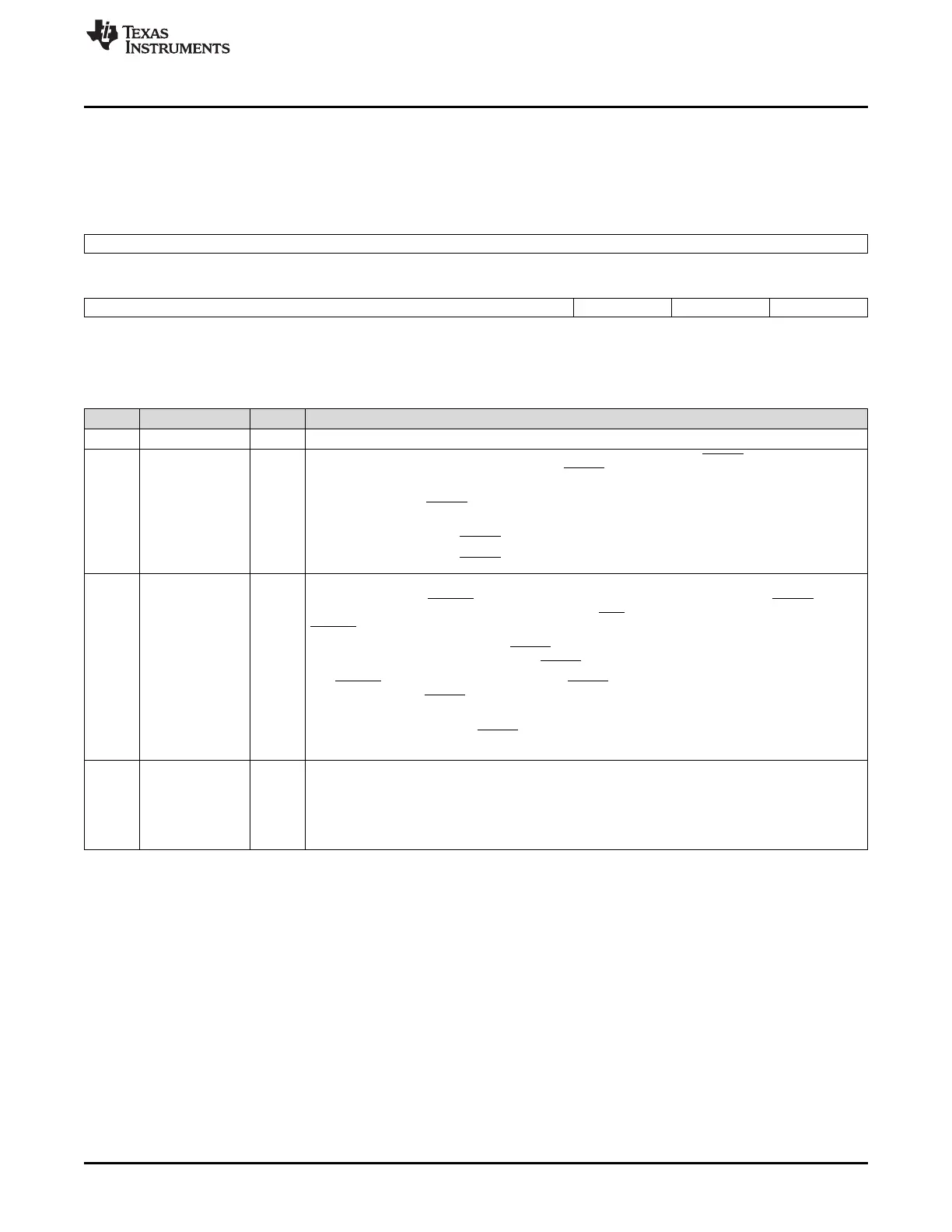

1.3.4.5 Watchdog Registers

The system control and status register (SCSR) contains the watchdog override bit and the watchdog

interrupt enable/disable bit. Figure 1-27 describes the bit functions of the SCSR register.

Figure 1-27. System Control and Status Register (SCSR)

15 8

Reserved

R-0

7 3 2 1 0

Reserved WDINTS WDENINT WDOVERRIDE

R-0 R-1 R/W-0 R/W1C-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

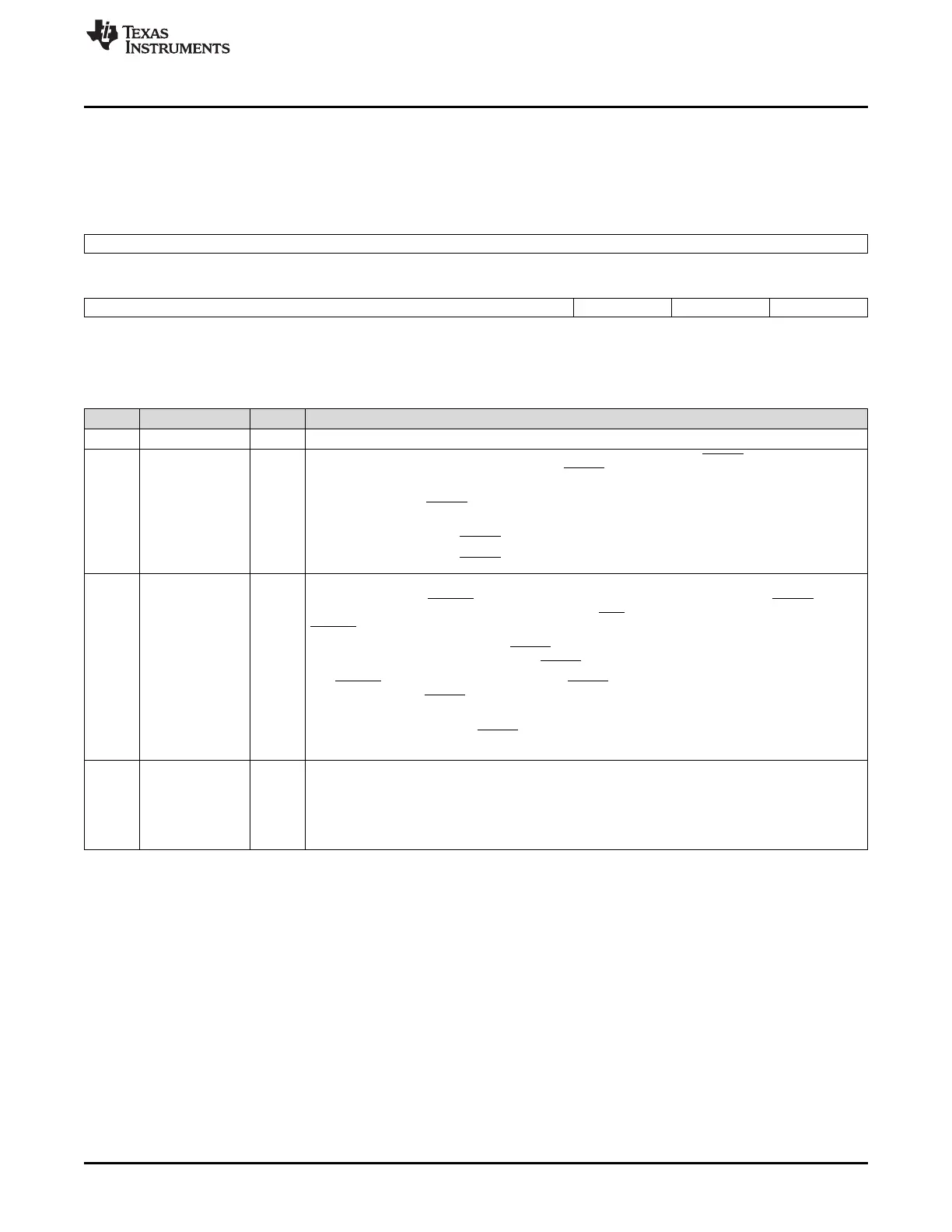

Table 1-27. System Control and Status Register (SCSR) Field Descriptions

Bit Field Value Description

(1)

15-3 Reserved

2 WDINTS Watchdog interrupt status bit. WDINTS reflects the current state of the WDINT signal from the

watchdog block. WDINTS follows the state of WDINT by two SYSCLKOUT cycles.

If the watchdog interrupt is used to wake the device from IDLE or STANDBY low power mode, use

this bit to make sure WDINT is not active before attempting to go back into IDLE or STANDBY

mode.

0 Watchdog interrupt signal (WDINT) is active.

1 Watchdog interrupt signal (WDINT) is not active.

1 WDENINT Watchdog interrupt enable.

0 The watchdog reset (WDRST) output signal is enabled and the watchdog interrupt (WDINT) output

signal is disabled. This is the default state on reset (XRS). When the watchdog interrupt occurs the

WDRST signal will stay low for 512 OSCCLK cycles.

If the WDENINT bit is cleared while WDINT is low, a reset will immediately occur. The WDINTS bit

can be read to determine the state of the WDINT signal.

1 The WDRST output signal is disabled and the WDINT output signal is enabled. When the watchdog

interrupt occurs, the WDINTsignal will stay low for 512 OSCCLK cycles.

If the watchdog interrupt is used to wake the device from IDLE or STANDBY low power mode, use

the WDINTS bit to make sure WDINT is not active before attempting to go back into IDLE or

STANDBY mode.

0 WDOVERRIDE Watchdog override

0 Writing a 0 has no effect. If this bit is cleared, it remains in this state until a reset occurs. The

current state of this bit is readable by the user.

1 You can change the state of the watchdog disable (WDDIS) bit in the watchdog control (WDCR)

register. If the WDOVERRIDE bit is cleared by writing a 1, you cannot modify the WDDIS bit.

Loading...

Loading...