www.ti.com

Flash and OTP Memory Blocks

45

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

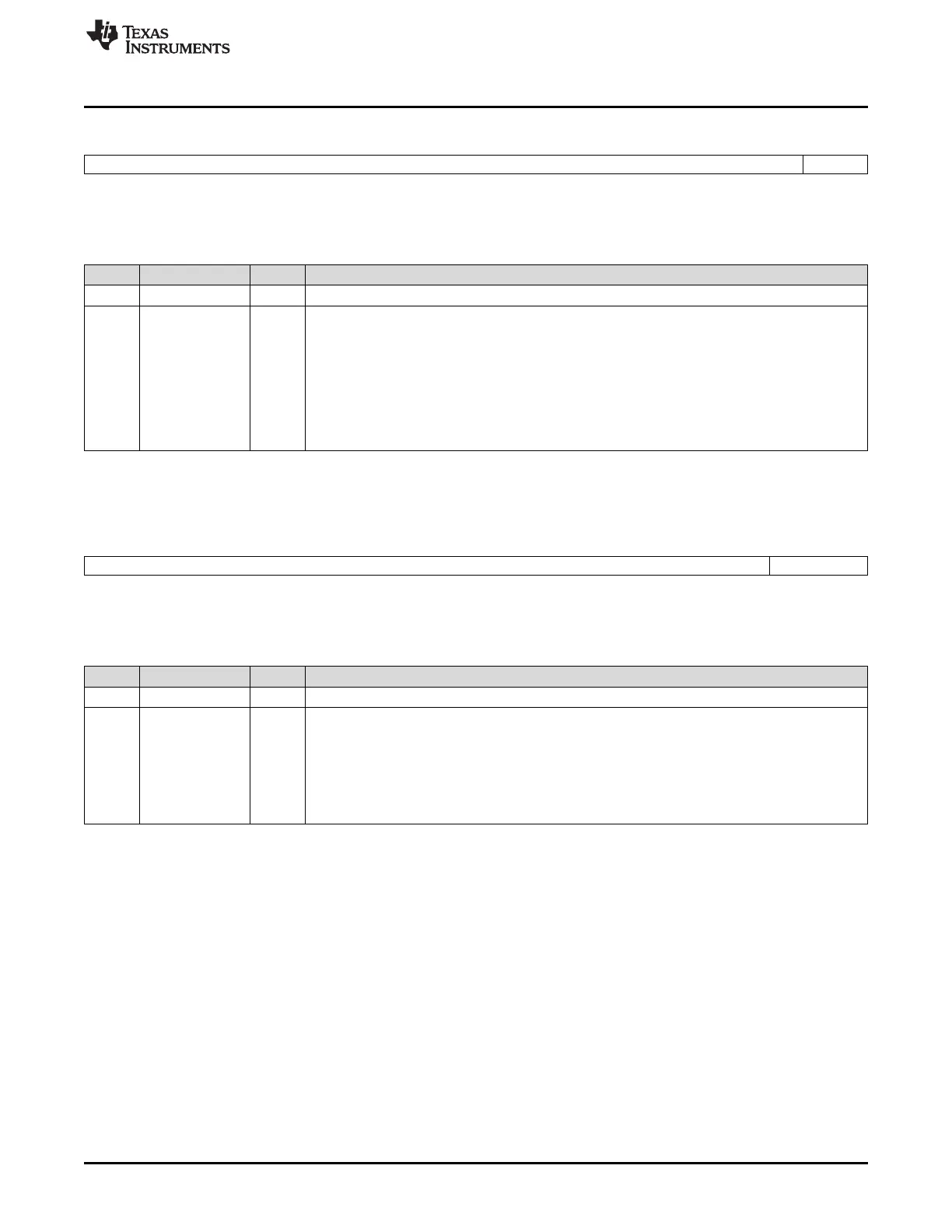

Figure 1-4. Flash Options Register (FOPT)

15 1 0

Reserved ENPIPE

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

(2)

This register is protected by the Code Security Module (CSM). See Section 1.2 for more information.

(3)

When writing to this register, follow the procedure described in Section 1.1.3.4.

Table 1-2. Flash Options Register (FOPT) Field Descriptions

Bit Field Value Description

(1) (2) (3)

15-1 Reserved

0 ENPIPE Enable Flash Pipeline Mode Bit. Flash pipeline mode is active when this bit is set. The pipeline

mode improves performance of instruction fetches by pre-fetching instructions. See Section 1.1.3.2

for more information.

When pipeline mode is enabled, the flash wait states (paged and random) must be greater than

zero.

On flash devices, ENPIPE affects fetches from flash and OTP.

0 Flash Pipeline mode is not active. (default)

1 Flash Pipeline mode is active.

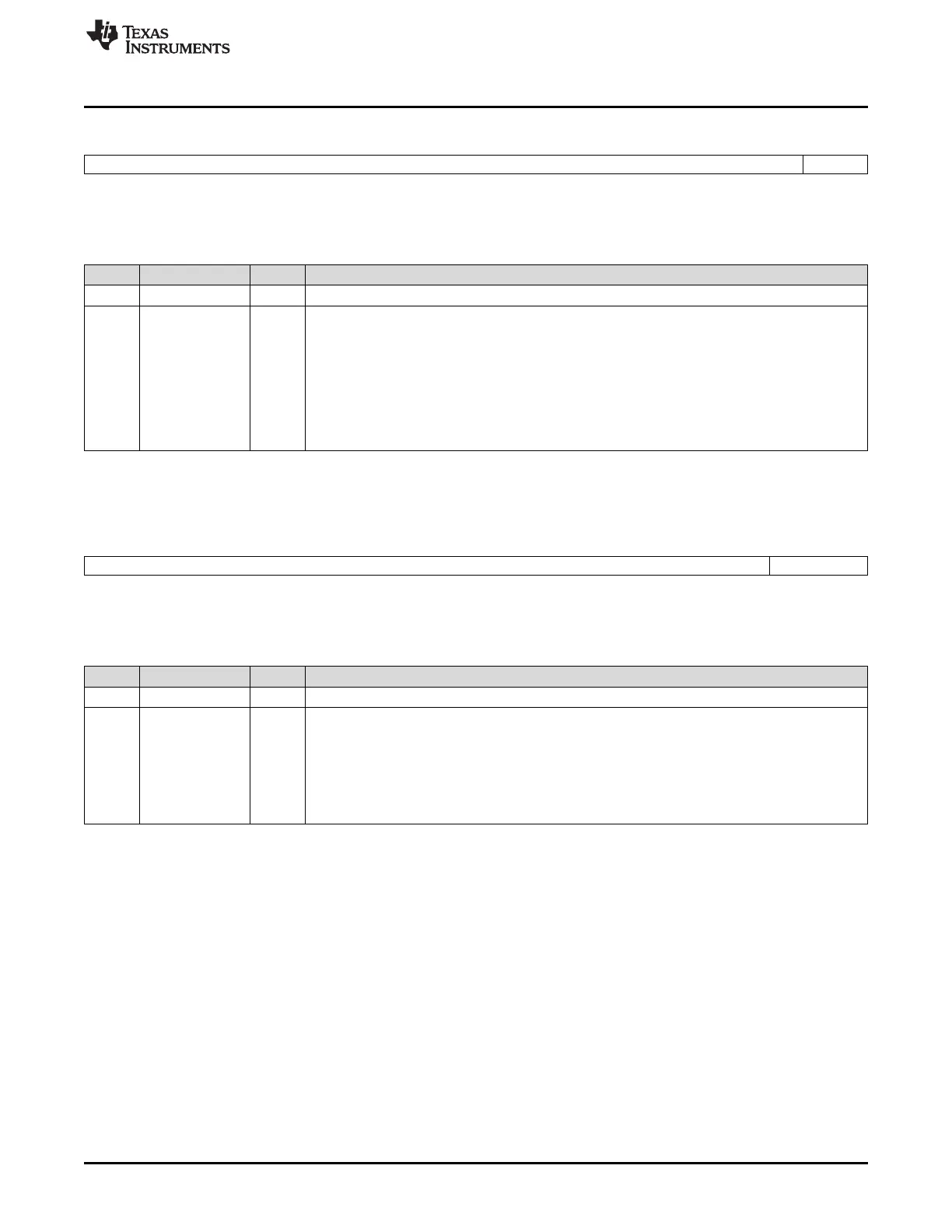

Figure 1-5. Flash Power Register (FPWR)

15 2 1 0

Reserved PWR

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

(2)

This register is protected by the Code Security Module (CSM). See Section 1.2 for more information.

Table 1-3. Flash Power Register (FPWR) Field Descriptions

Bit Field Value Description

(1) (2)

15-2 Reserved

1-0 PWR Flash Power Mode Bits. Writing to these bits changes the current power mode of the flash bank

and pump. See section Section 1.1.3 for more information on changing the flash bank power mode.

00 Pump and bank sleep (lowest power)

01 Pump and bank standby

10 Reserved (no effect)

11 Pump and bank active (highest power)

Loading...

Loading...