eCAN Registers

www.ti.com

804

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Controller Area Network (CAN)

13.8.4 Transmission-Request-Reset Register (CANTRR)

These bits can only be set by the CPU and reset by the internal logic. These bits are reset when a

transmission is successful or is aborted. If the CPU tries to set a bit while the CAN tries to clear it, the bit

is set.

Setting the TRR[n] bit of the message object n cancels a transmission request if it was initiated by the

corresponding bit (TRS[n]) and is not currently being processed. If the corresponding message is currently

being processed, the bit is reset when a transmission is successful (normal operation) or when an aborted

transmission due to a lost arbitration or an error condition is detected on the CAN bus line. When a

transmission is aborted, the corresponding status bit (AA.31-0) is set. When a transmission is successful,

the status bit (TA.31-0) is set. The status of the transmission request reset can be read from the TRS.31-0

bit.

The bits in CANTRR are set by writing a 1 from the CPU.

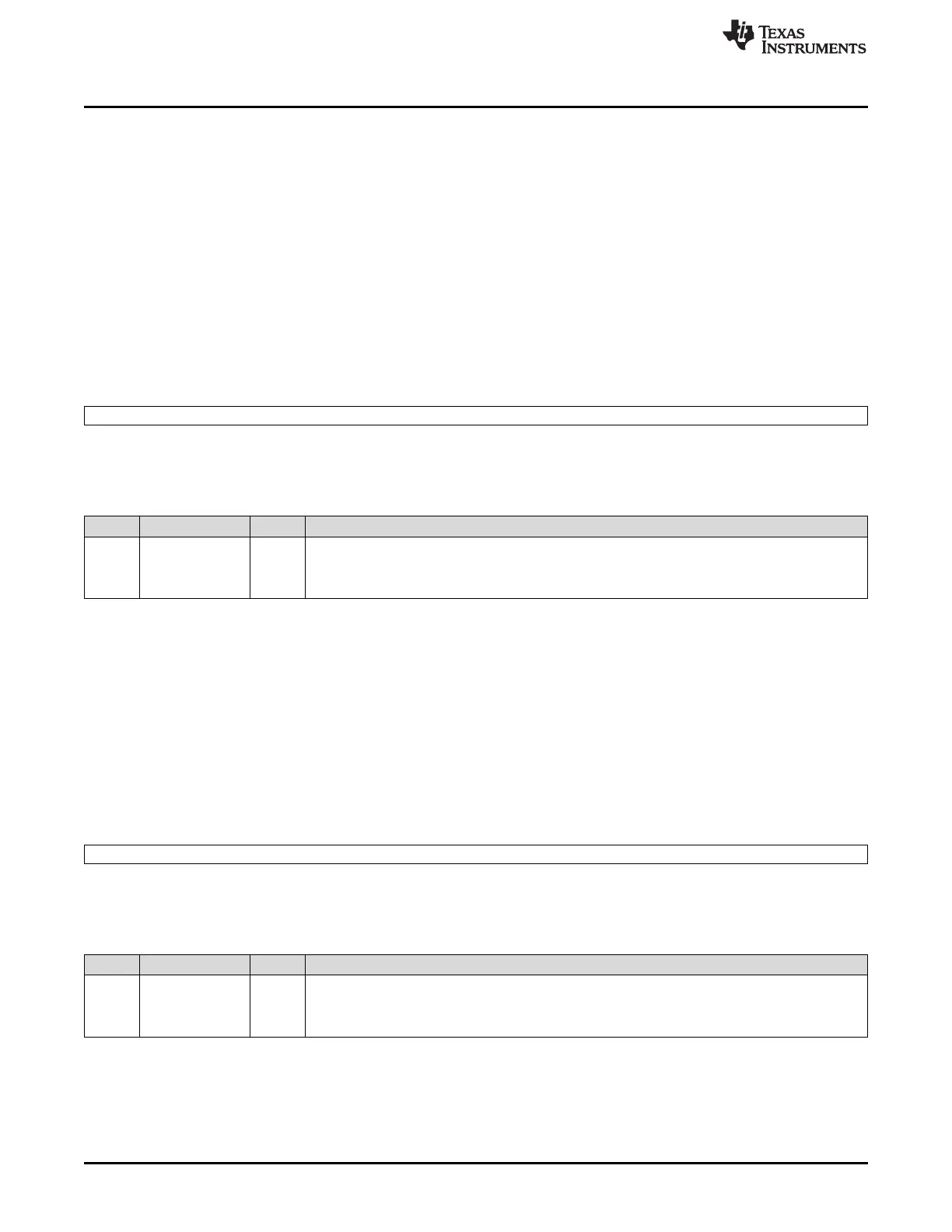

Figure 13-13. Transmission-Request-Reset Register (CANTRR)

31 0

TRR[31:0]

RS-0

LEGEND: RS = Read/Set; -n = value after reset

Table 13-12. Transmission-Request-Reset Register (CANTRR) Field Descriptions

Bit Field Value Description

31:0 TRR[31:0] Transmit-request-reset bits

1 Setting TRRn cancels a transmission request

0 No operation

13.8.5 Transmission-Acknowledge Register (CANTA)

If the message of mailbox n was sent successfully, the bit TA[n] is set. This also sets the GMIF0/GMIF1

(CANGIF0.15/CANGIF1.15) bit if the corresponding interrupt mask bit in the CANMIM register is set. The

GMIF0/GMIF1 bit initiates an interrupt.

The CPU resets the bits in CANTA by writing a 1. This also clears the interrupt if an interrupt has been

generated. Writing a 0 has no effect. If the CPU tries to reset the bit while the CAN tries to set it, the bit is

set. After power-up, all bits are cleared.

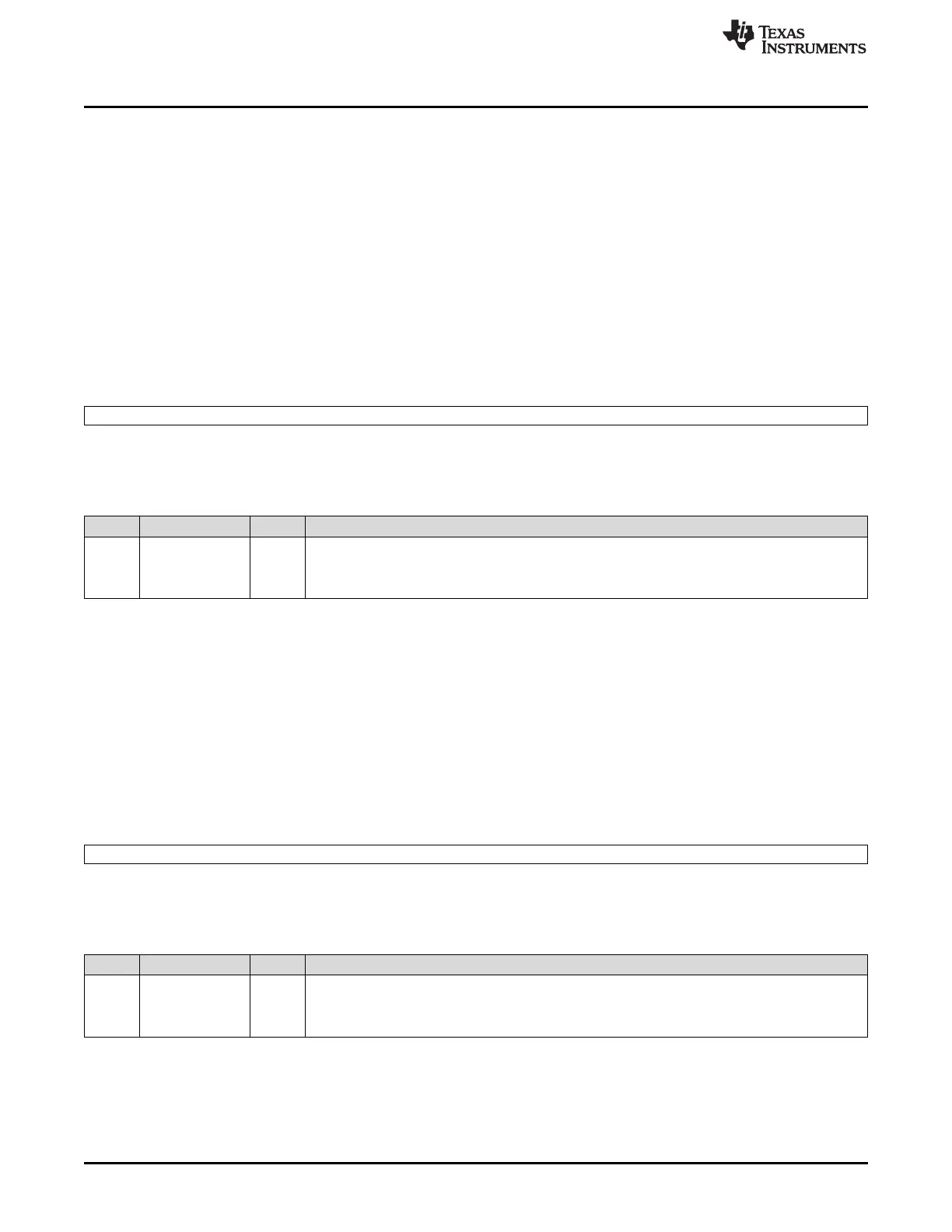

Figure 13-14. Transmission-Acknowledge Register (CANTA)

31 0

TA[31:0]

RC-0

LEGEND: RC = Read/Clear; -n = value after reset

Table 13-13. Transmission-Acknowledge Register (CANTA) Field Descriptions

Bit Field Value Description

31:0 TA[31:0] Transmit-acknowledge bits

1 If the message of mailbox n is sent successfully, the bit n of this register is set.

0 The message is not sent.

Loading...

Loading...