www.ti.com

eQEP Registers

431

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Quadrature Encoder Pulse (eQEP)

6.10.2.16 QEINT Register (Offset = 18h) [reset = 0h]

QEINT is shown in Figure 6-36 and described in Table 6-21.

Return to the Summary Table.

QEP Interrupt Control

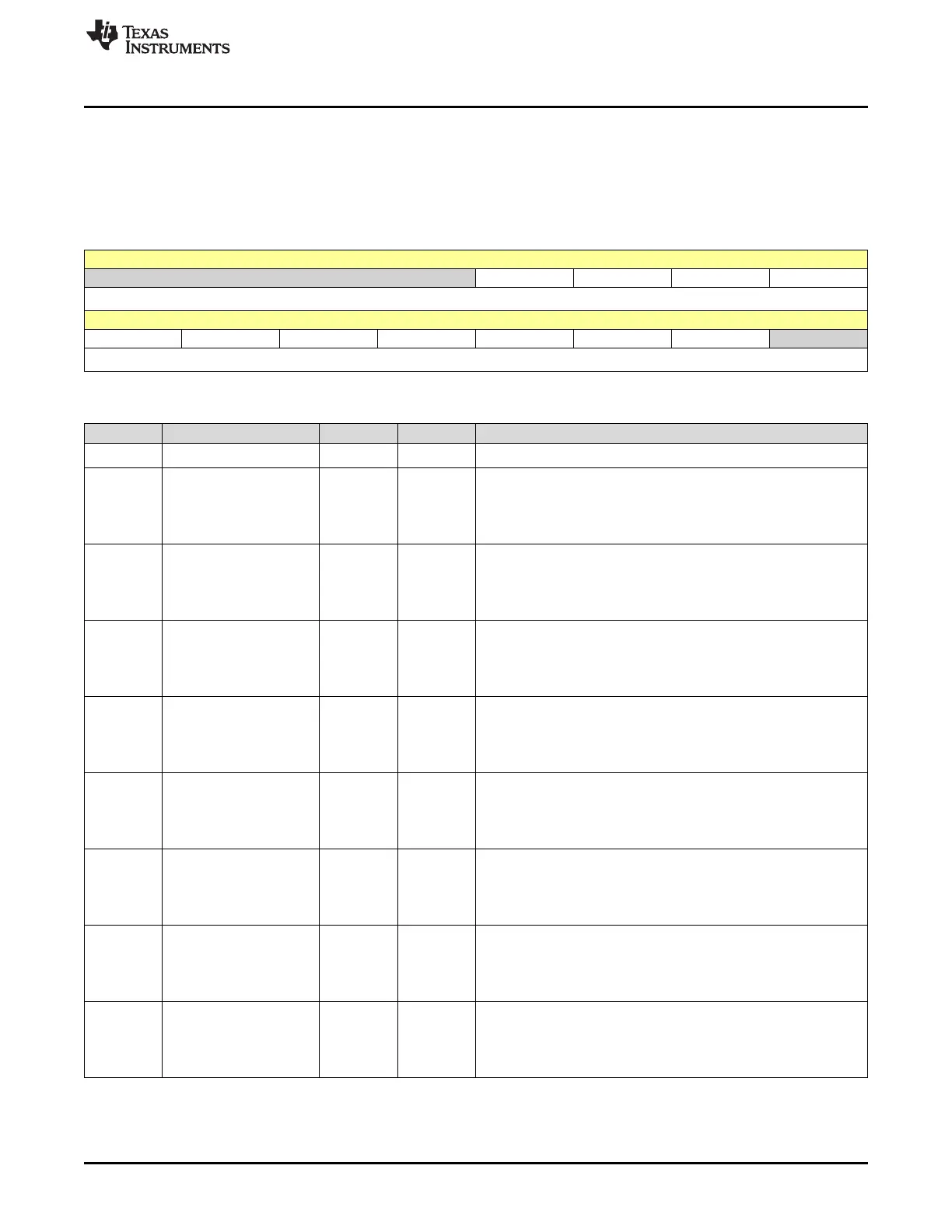

Figure 6-36. QEINT Register

15 14 13 12 11 10 9 8

RESERVED UTO IEL SEL PCM

R-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

PCR PCO PCU WTO QDC QPE PCE RESERVED

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R-0h

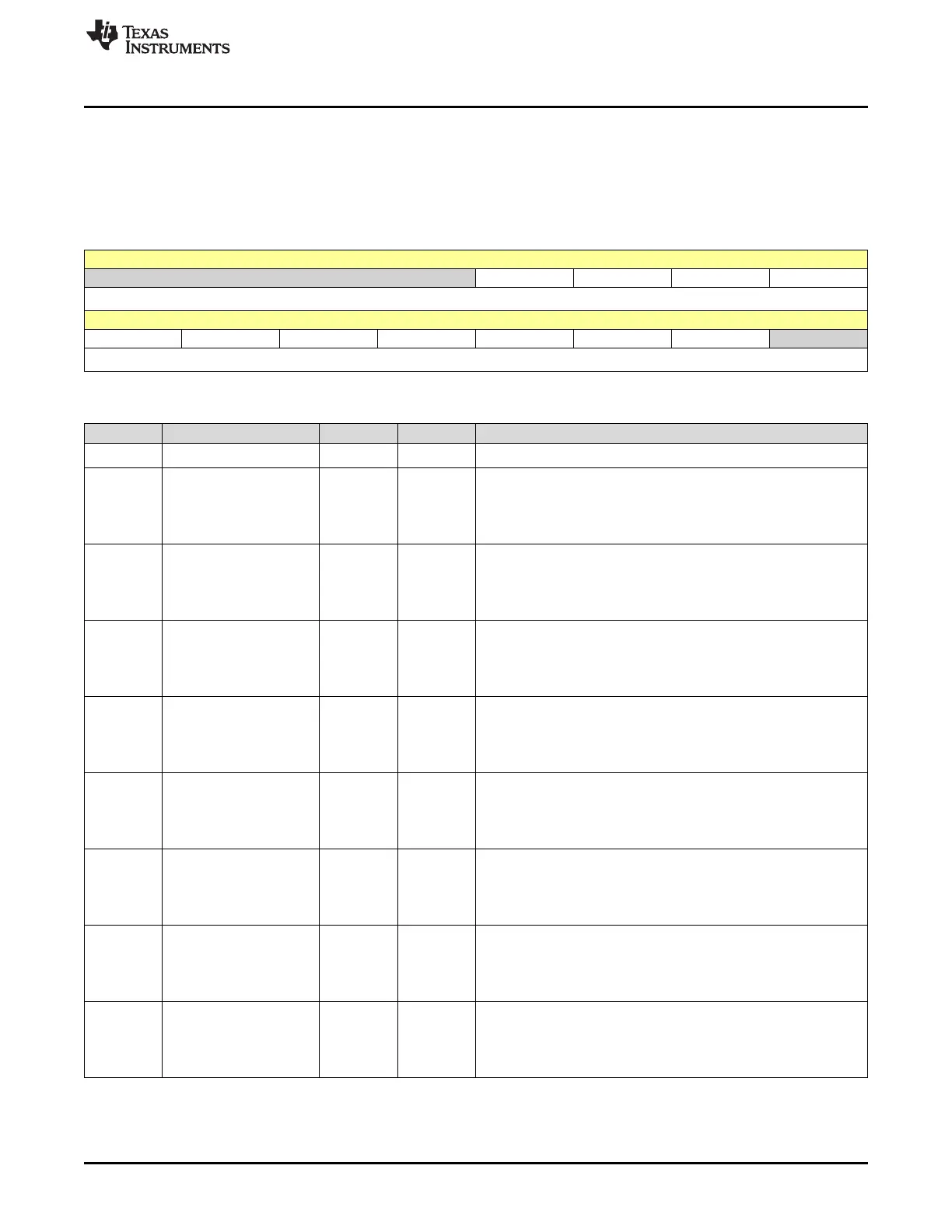

Table 6-21. QEINT Register Field Descriptions

Bit Field Type Reset Description

15-12 RESERVED R 0h

Reserved

11 UTO R/W 0h

Unit time out interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

10 IEL R/W 0h

Index event latch interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

9 SEL R/W 0h

Strobe event latch interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

8 PCM R/W 0h

Position-compare match interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

7 PCR R/W 0h

Position-compare ready interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

6 PCO R/W 0h

Position counter overflow interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

5 PCU R/W 0h

Position counter underflow interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

4 WTO R/W 0h

Watchdog time out interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt is disabled

1h (R/W) = Interrupt is enabled

Loading...

Loading...