Clocking and System Control

www.ti.com

72

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

1.3.2.5 PLL Control, Status and XCLKOUT Register Descriptions

The DIV field in the PLLCR register controls whether the PLL is bypassed or not and sets the PLL

clocking ratio when it is not bypassed. PLL bypass is the default mode after reset. Do not write to the DIV

field if the PLLSTS[DIVSEL] bit is 10 or 01, or if the PLL is operating in limp mode as indicated by the

PLLSTS[MCLKSTS] bit being set . See the procedure for changing the PLLCR described in Figure 1-22.

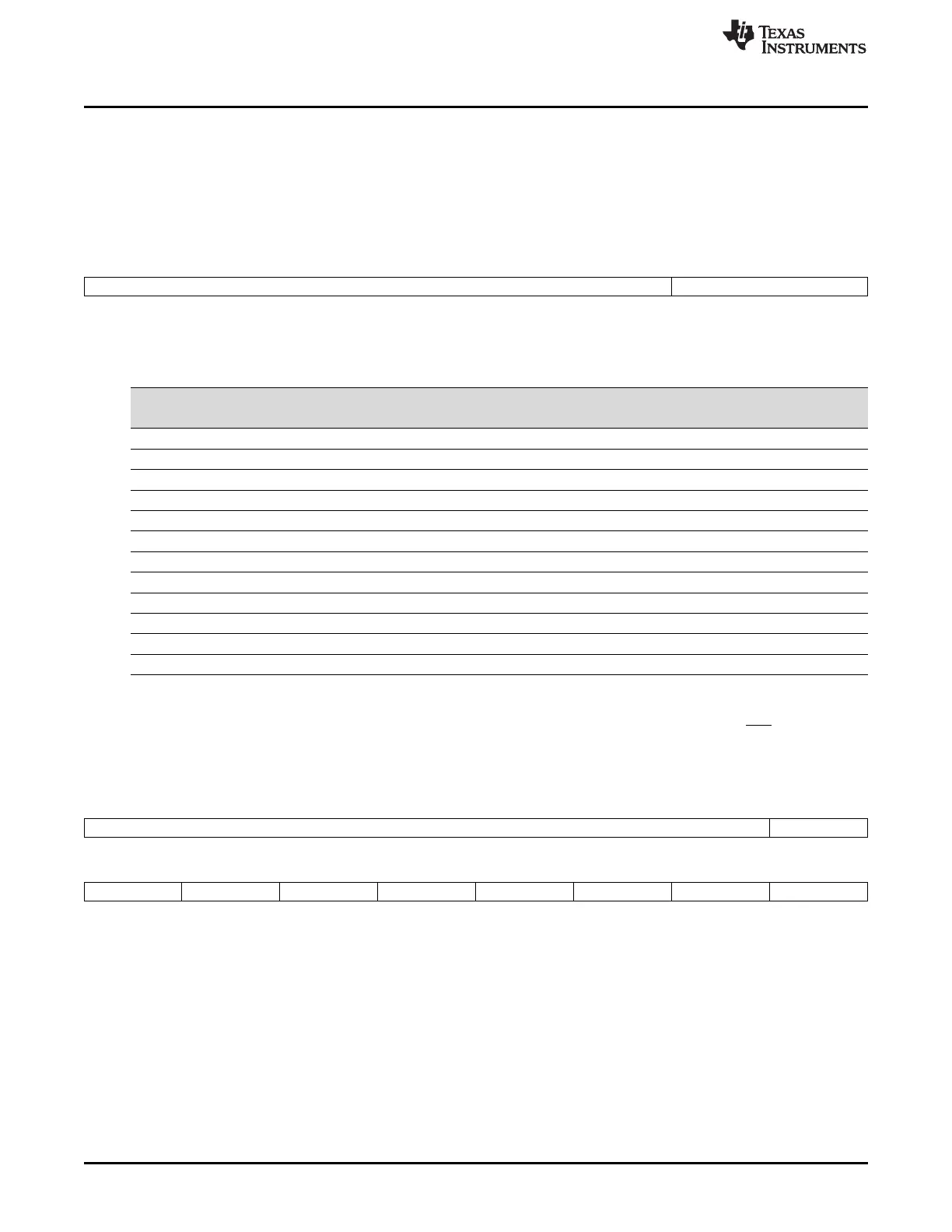

Figure 1-23. PLLCR Register Layout

15 4 3 0

Reserved DIV

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

(2)

PLLSTS[DIVSEL] must be 0 before writing to the PLLCR and should be changed only after PLLSTS[PLLLOCKS] = 1. See

Figure 1-22.

(3)

The PLL control register (PLLCR) and PLL Status Register (PLLSTS) are reset to their default state by the XRS signal or a

watchdog reset only. A reset issued by the debugger or the missing clock detect logic have no effect.

Table 1-21. PLLCR Bit Descriptions

(1)

SYSCLKOUT (CLKIN)

(2)

PLLCR[DIV] Value

(3)

PLLSTS[DIVSEL] = 0 or 1 PLLSTS[DIVSEL] = 2 PLLSTS[DIVSEL] = 3

0000 (PLL bypass) OSCCLK/4 (Default) OSCCLK/2 OSCCLK

0001 (OSCCLK * 1)/4 (OSCCLK*1)/2 –

0010 (OSCCLK * 2)/4 (OSCCLK*2)/2 –

0011 (OSCCLK * 3)/4 (OSCCLK*3)/2 –

0100 (OSCCLK * 4)/4 (OSCCLK*4)/2 –

0101 (OSCCLK * 5)/4 (OSCCLK*5)/2 –

0110 (OSCCLK * 6)/4 (OSCCLK*6)/2 –

0111 (OSCCLK * 7)/4 (OSCCLK*7)/2 –

1000 (OSCCLK * 8)/4 (OSCCLK*8)/2 –

1001 (OSCCLK * 9)/4 (OSCCLK*9)/2 –

1010 (OSCCLK * 10)/4 (OSCCLK*10)/2 –

1011 - 1111 Reserved Reserved Reserved

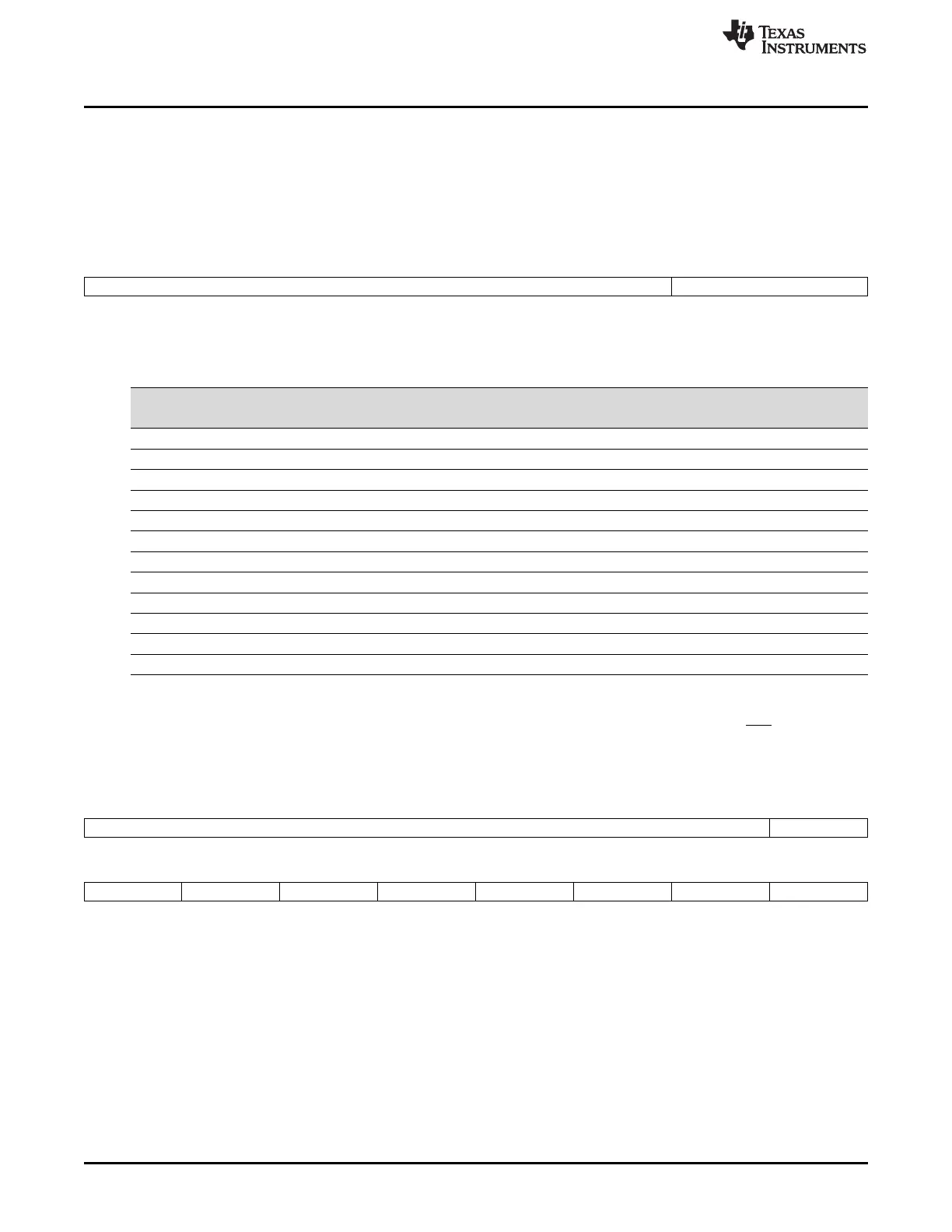

Figure 1-24. PLL Status Register (PLLSTS)

15 9 8

Reserved DIVSEL

R-0 R/W-0

7 6 5 4 3 2 1 0

DIVSEL MCLKOFF OSCOFF MCLKCLR MCLKSTS PLLOFF Reserved PLLLOCKS

R/W-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0 R-0 R-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Loading...

Loading...