Registers

www.ti.com

322

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Pulse Width Modulator (ePWM) Module

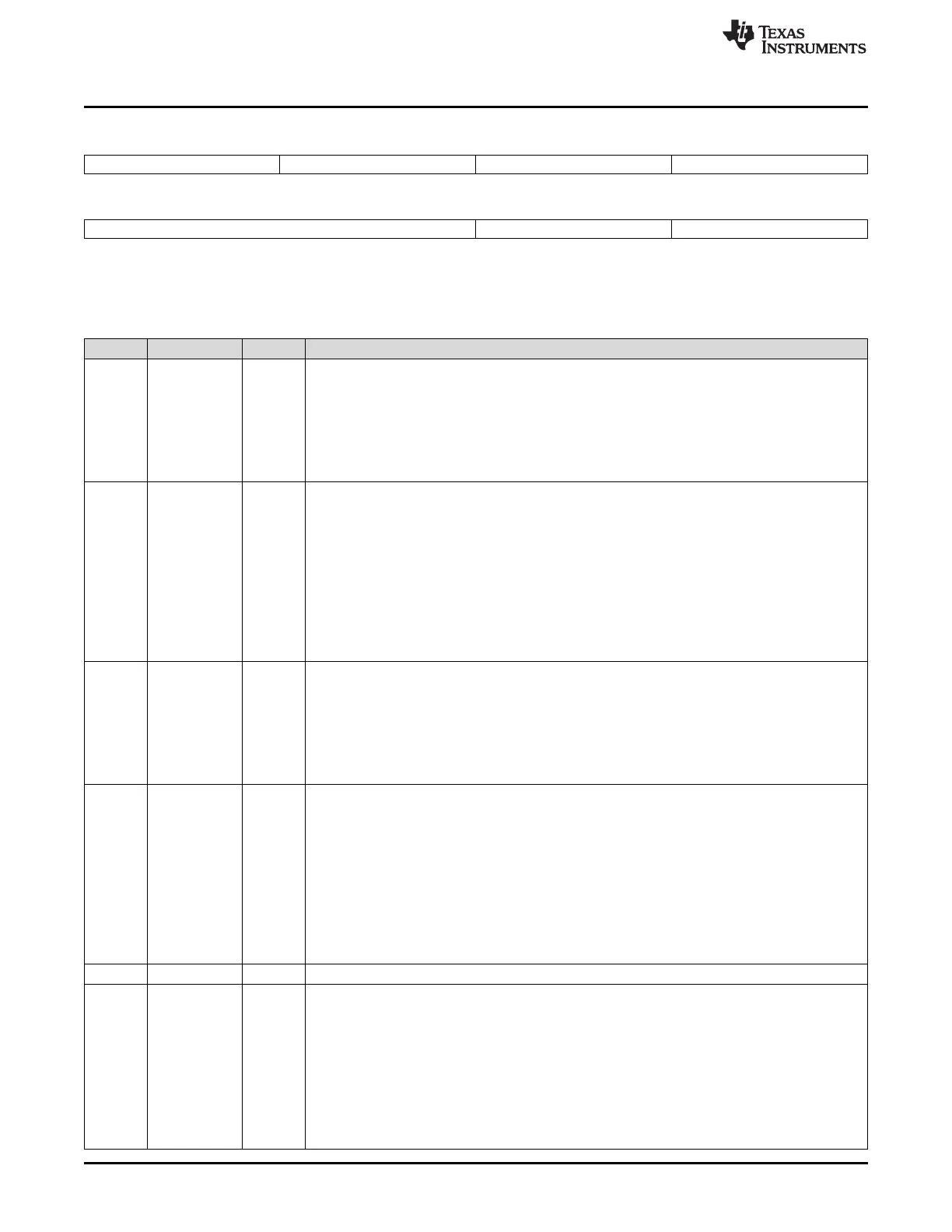

Figure 3-85. Event-Trigger Prescale Register (ETPS)

15 14 13 12 11 10 9 8

SOCBCNT SOCBPRD SOCACNT SOCAPRD

R-0 R/W-0 R-0 R/W-0

7 4 3 2 1 0

Reserved INTCNT INTPRD

R-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

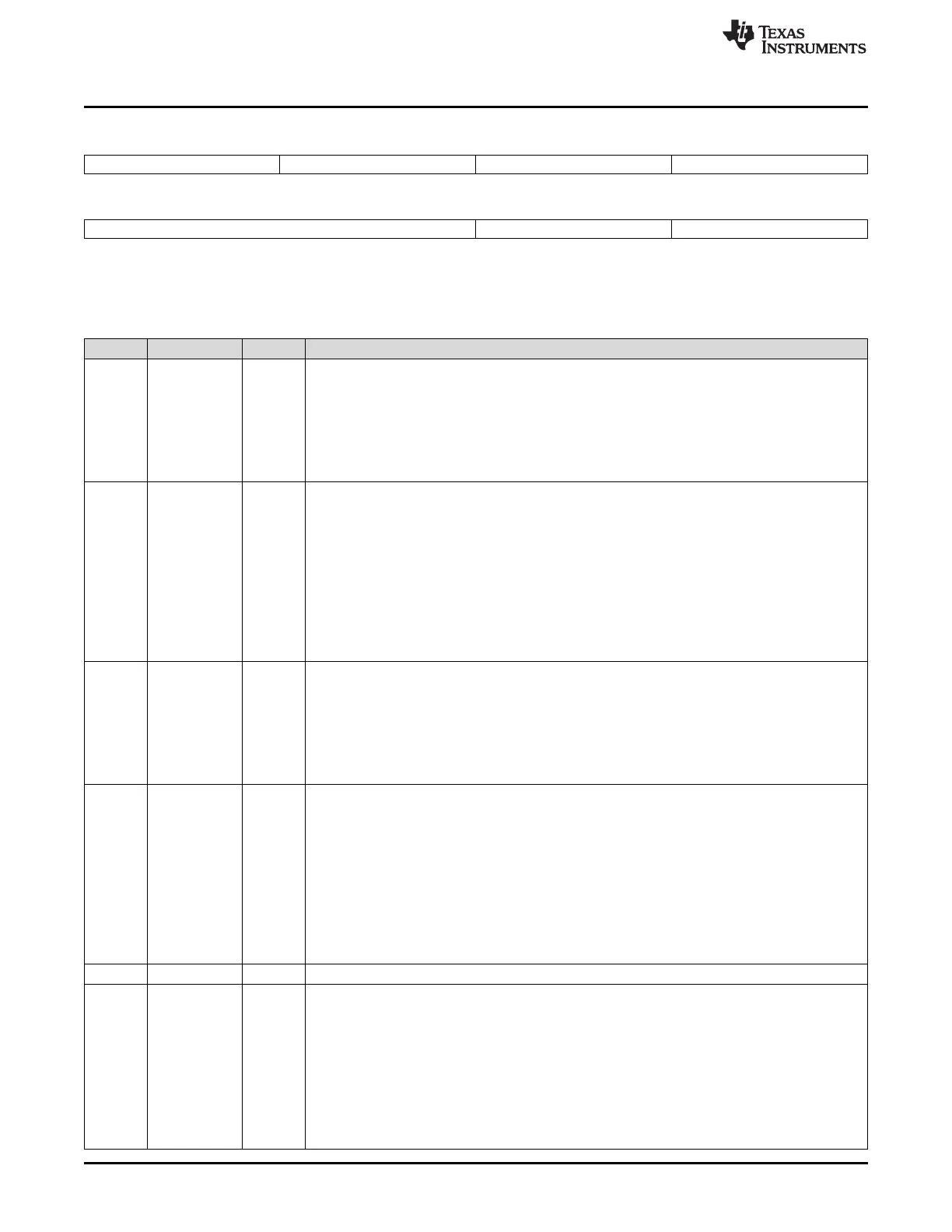

Table 3-45. Event-Trigger Prescale Register (ETPS) Field Descriptions

Bits Name Description

15-14 SOCBCNT ePWM ADC Start-of-Conversion B Event (EPWMxSOCB) Counter Register

These bits indicate how many selected ETSEL[SOCBSEL] events have occurred:

00 No events have occurred.

01 1 event has occurred.

10 2 events have occurred.

11 3 events have occurred.

13-12 SOCBPRD ePWM ADC Start-of-Conversion B Event (EPWMxSOCB) Period Select

These bits determine how many selected ETSEL[SOCBSEL] events need to occur before an

EPWMxSOCB pulse is generated. To be generated, the pulse must be enabled (ETSEL[SOCBEN]

= 1). The SOCB pulse will be generated even if the status flag is set from a previous start of

conversion (ETFLG[SOCB] = 1). Once the SOCB pulse is generated, the ETPS[SOCBCNT] bits will

automatically be cleared.

00 Disable the SOCB event counter. No EPWMxSOCB pulse will be generated

01 Generate the EPWMxSOCB pulse on the first event: ETPS[SOCBCNT] = 0,1

10 Generate the EPWMxSOCB pulse on the second event: ETPS[SOCBCNT] = 1,0

11 Generate the EPWMxSOCB pulse on the third event: ETPS[SOCBCNT] = 1,1

11-10 SOCACNT ePWM ADC Start-of-Conversion A Event (EPWMxSOCA) Counter Register

These bits indicate how many selected ETSEL[SOCASEL] events have occurred:

00 No events have occurred.

01 1 event has occurred.

10 2 events have occurred.

11 3 events have occurred.

9-8 SOCAPRD ePWM ADC Start-of-Conversion A Event (EPWMxSOCA) Period Select

These bits determine how many selected ETSEL[SOCASEL] events need to occur before an

EPWMxSOCA pulse is generated. To be generated, the pulse must be enabled (ETSEL[SOCAEN]

= 1). The SOCA pulse will be generated even if the status flag is set from a previous start of

conversion (ETFLG[SOCA] = 1). Once the SOCA pulse is generated, the ETPS[SOCACNT] bits will

automatically be cleared.

00 Disable the SOCA event counter. No EPWMxSOCA pulse will be generated

01 Generate the EPWMxSOCA pulse on the first event: ETPS[SOCACNT] = 0,1

10 Generate the EPWMxSOCA pulse on the second event: ETPS[SOCACNT] = 1,0

11 Generate the EPWMxSOCA pulse on the third event: ETPS[SOCACNT] = 1,1

7-4 Reserved Reserved

3-2 INTCNT ePWM Interrupt Event (EPWMx_INT) Counter Register

These bits indicate how many selected ETSEL[INTSEL] events have occurred. These bits are

automatically cleared when an interrupt pulse is generated. If interrupts are disabled, ETSEL[INT] =

0 or the interrupt flag is set, ETFLG[INT] = 1, the counter will stop counting events when it reaches

the period value ETPS[INTCNT] = ETPS[INTPRD].

00 No events have occurred.

01 1 event has occurred.

10 2 events have occurred.

11 3 events have occurred.

Loading...

Loading...