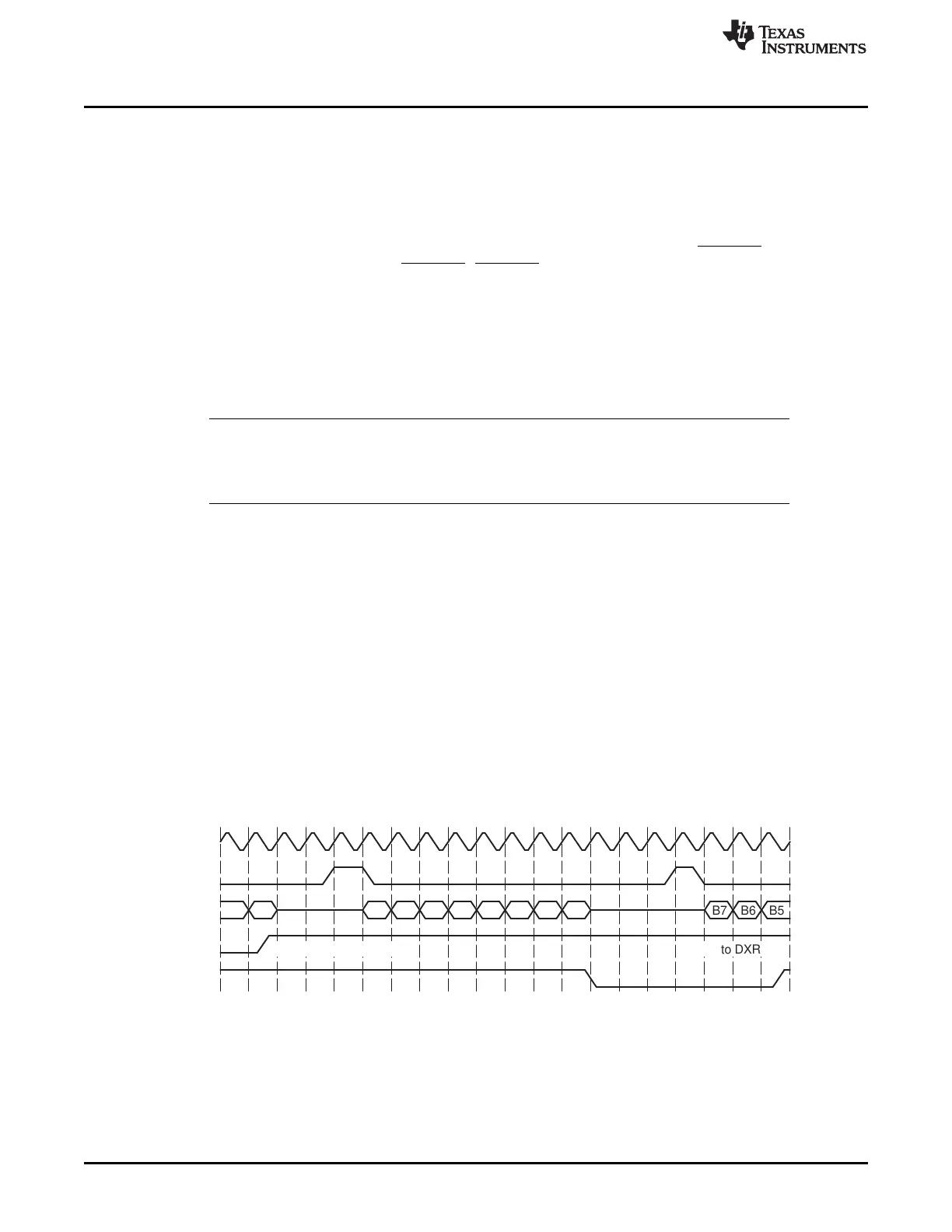

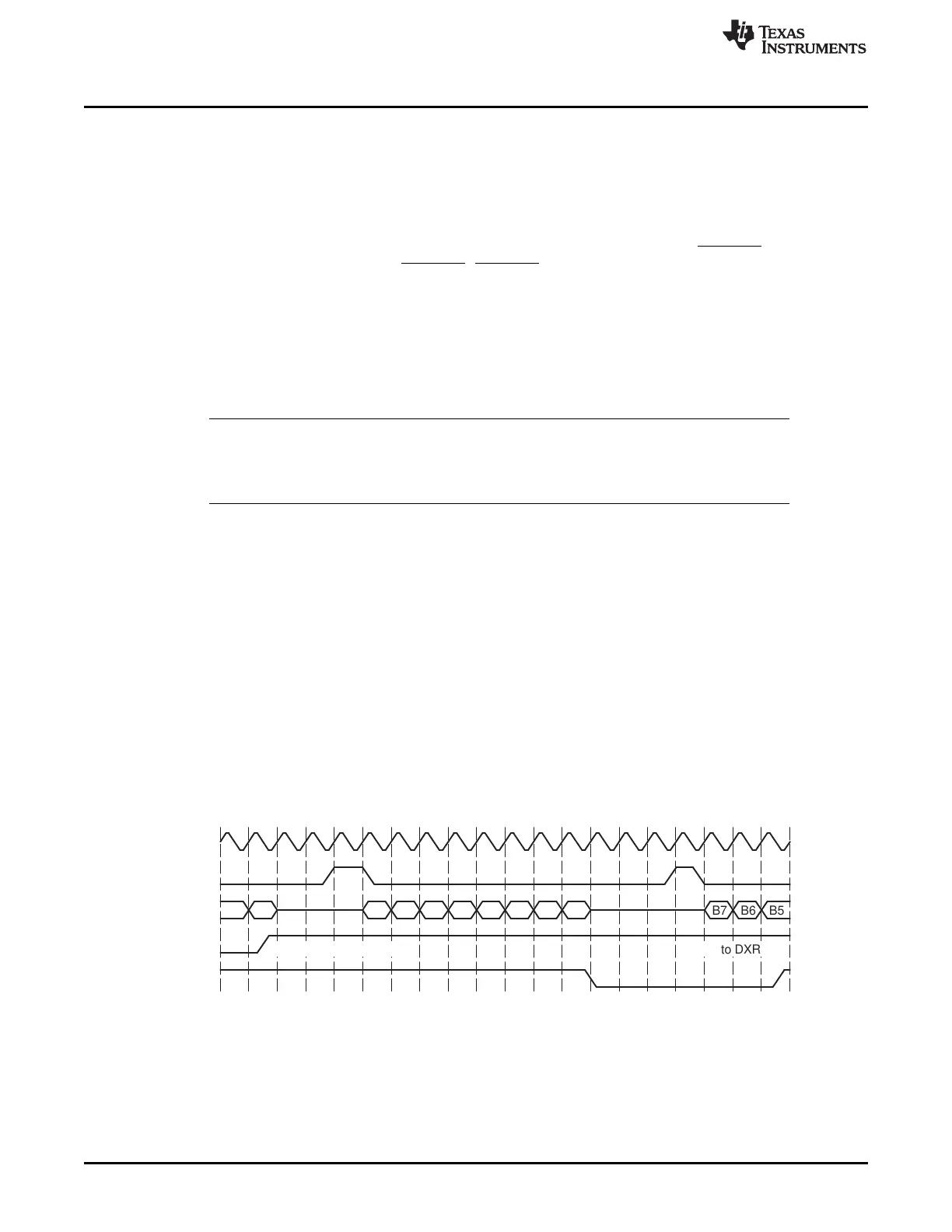

B5B6B7B0B1B2B3B4B5B6B7A0A1

XRDY

DX

FSX

CLKX

Write to DXR1(C)DXR1 to XSR1 copy(B)

McBSP Exception/Error Conditions

www.ti.com

682

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

• Wait for a transmit interrupt (XINT) before writing to the DXR(s). When XINTM = 00b in SPCR2, the

transmitter sends XINT to the CPU each time XRDY is set.

You can prevent DMA overwrites by synchronizing DMA transfers to the transmit synchronization event

XEVT. The transmitter sends an XEVT signal each time XRDY is set.

12.5.5 Underflow in the Transmitter

The McBSP indicates a transmitter empty (or underflow) condition by clearing the XEMPTY bit in SPCR2.

Either of the following events activates XEMPTY (XEMPTY = 0):

• DXR1 has not been loaded since the last DXR-to-XSR copy, and all bits of the data word in the XSR(s)

have been shifted out on the DX pin.

• The transmitter is reset (by forcing XRST = 0 in SPCR2, or by a device reset) and is then restarted.

In the underflow condition, the transmitter continues to transmit the old data that is in the DXR(s) for every

new transmit frame-synchronization signal, until a new value is loaded into DXR1 by the CPU or the DMA

controller.

NOTE: If both DXRs are needed (word length larger than 16 bits), the CPU or the DMA controller

must load DXR2 first and then load DXR1. As soon as DXR1 is loaded, the contents of both

DXRs are copied to the transmit shift registers (XSRs). If DXR2 is not loaded first, the

previous content of DXR2 is passed to the XSR2.

XEMPTY is deactivated (XEMPTY = 1) when a new word in DXR1 is transferred to XSR1. If FSXM = 1 in

PCR and FSGM = 0 in SRGR2, the transmitter generates a single internal FSX pulse in response to a

DXR-to-XSR copy. Otherwise, the transmitter waits for the next frame-synchronization pulse before

sending out the next frame on DX.

When the transmitter is taken out of reset (XRST = 1), it is in a transmitter ready (XRDY = 1 in SPCR2)

and transmitter empty (XEMPTY = 0) state. If DXR1 is loaded by the CPU or the DMA controller before

internal FSX goes active high, a valid DXR-to-XSR transfer occurs. This allows for the first word of the first

frame to be valid even before the transmit frame-synchronization pulse is generated or detected.

Alternatively, if a transmit frame-synchronization pulse is detected before DXR1 is loaded, zeros are

output on DX.

12.5.5.1 Example of the Underflow Condition

Figure 12-27 shows an underflow condition. After B is transmitted, DXR1 is not reloaded before the

subsequent frame-synchronization pulse. Thus, B is again transmitted on DX.

Figure 12-27. Underflow During McBSP Transmission

12.5.5.2 Example of Preventing Underflow Condition

Figure 12-28 shows the case of writing to DXR1 just before an underflow condition would otherwise occur.

After B is transmitted, C is written to DXR1 before the next frame-synchronization pulse. As a result, there

is no underflow; B is not transmitted twice.

Loading...

Loading...