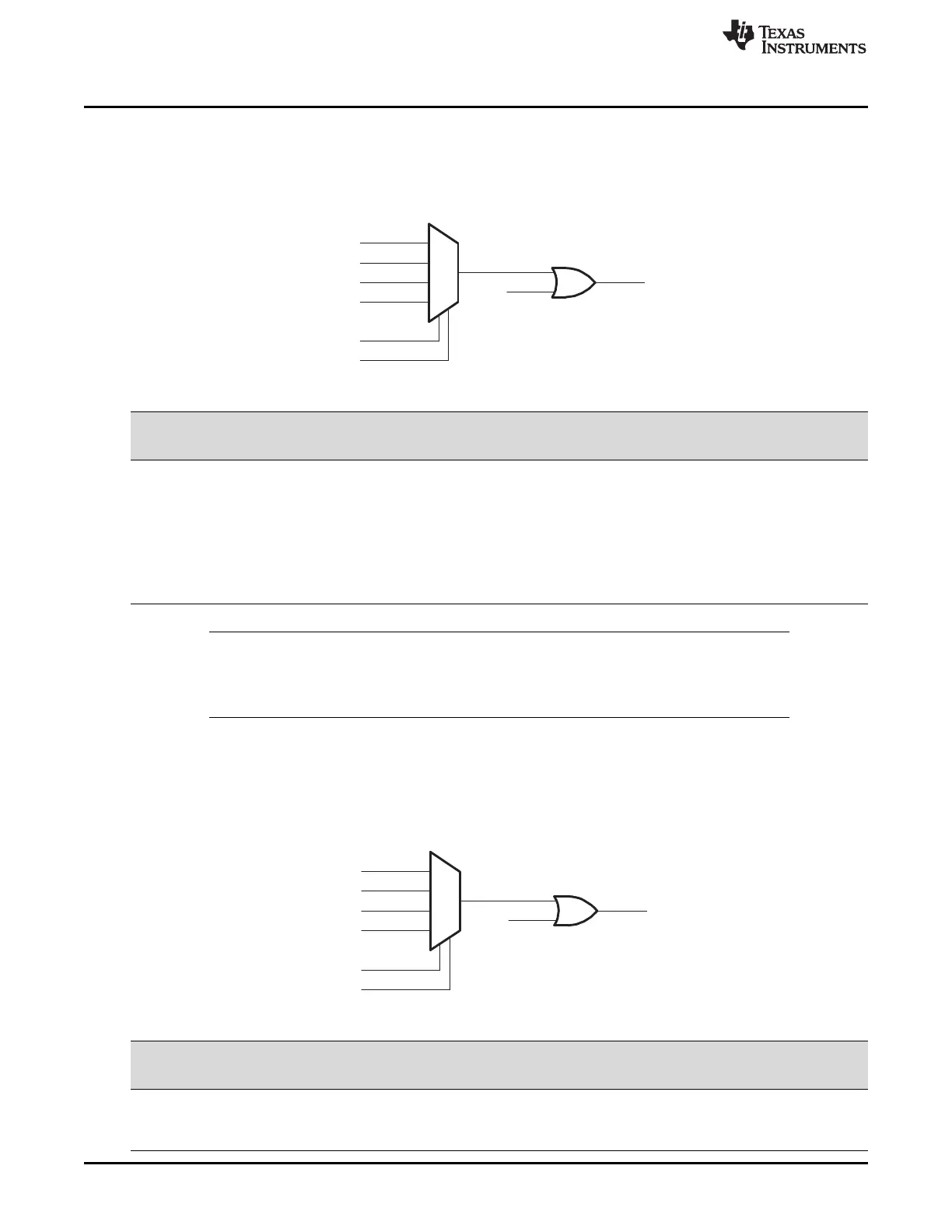

XRDY

00

EOBXcondition

01

FSXdetected

10

XSYNCERR

11

XINTMbits

XINT

XINTENA

MXINT

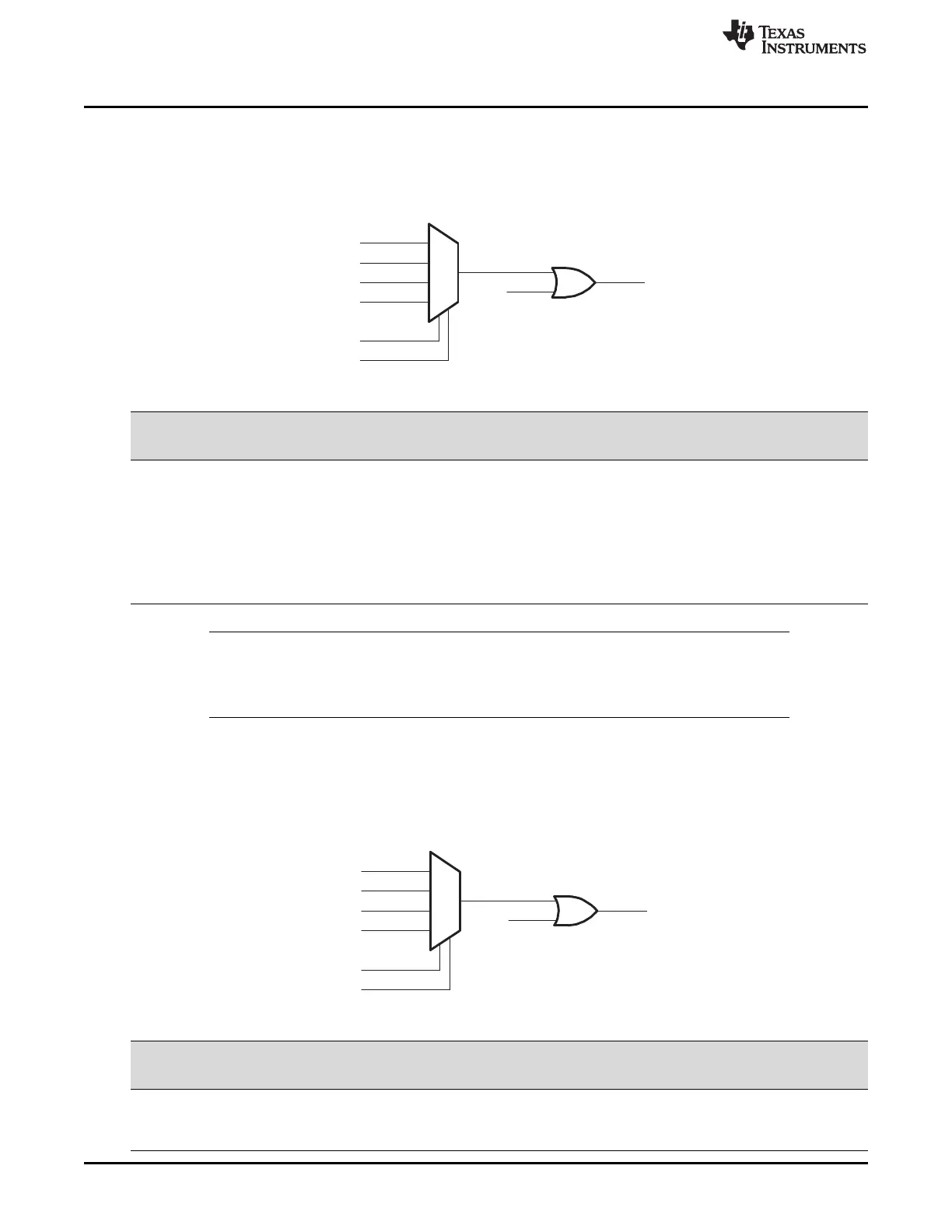

RRDY

00

EOBRcondition

01

FSRdetected

10

RSYNCERR

11

RINTMbits

RINT

RINTENA

MRINT

Interrupt Generation

www.ti.com

742

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

12.12.1 McBSP Receive Interrupt Generation

In the McBSP module, data receive and error conditions generate two sets of interrupt signals. One set is

used for the CPU and the other set is for DMA.

Figure 12-65. Receive Interrupt Generation

Table 12-72. Receive Interrupt Sources and Signals

McBSP

Interrupt

Signal

Interrupt Flags Interrupt Enables

in SPCR1

Interrupt Enables Type of Interrupt Interrupt Line

RINTM

Bits

RINT RRDY 0 RINTENA Every word receive MRINT

EOBR 1 RINTENA Every 16 channel

block boundary

FSR 10 RINTENA On every FSR

RSYNCERR 11 RINTENA Frame sync error

NOTE: Since X/RINT, X/REVTA, and X/RXFFINT share the same CPU interrupt, it is recommended

that all applications use one of the above selections for interrupt generation. If multiple

interrupt enables are selected at the same time, there is a likelihood of interrupts being

masked or not recognized.

12.12.2 McBSP Transmit Interrupt Generation

McBSP module data transmit and error conditions generate two sets of interrupt signals. One set is used

for the CPU and the other set is for DMA.

Figure 12-66. Transmit Interrupt Generation

Table 12-73. Transmit Interrupt Sources and Signals

McBSP

Interrupt

Signal

Interrupt

Flags

Interrupt

Enables in

SPCR2

Interrupt

Enables

Type of Interrupt Interrupt

Line

XINTM Bits

XINT XRDY 0 XINTENA Every word transmit MXINT

EOBX 1 XINTENA Every 16-channel block boundary

Loading...

Loading...