www.ti.com

I2C Registers

635

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

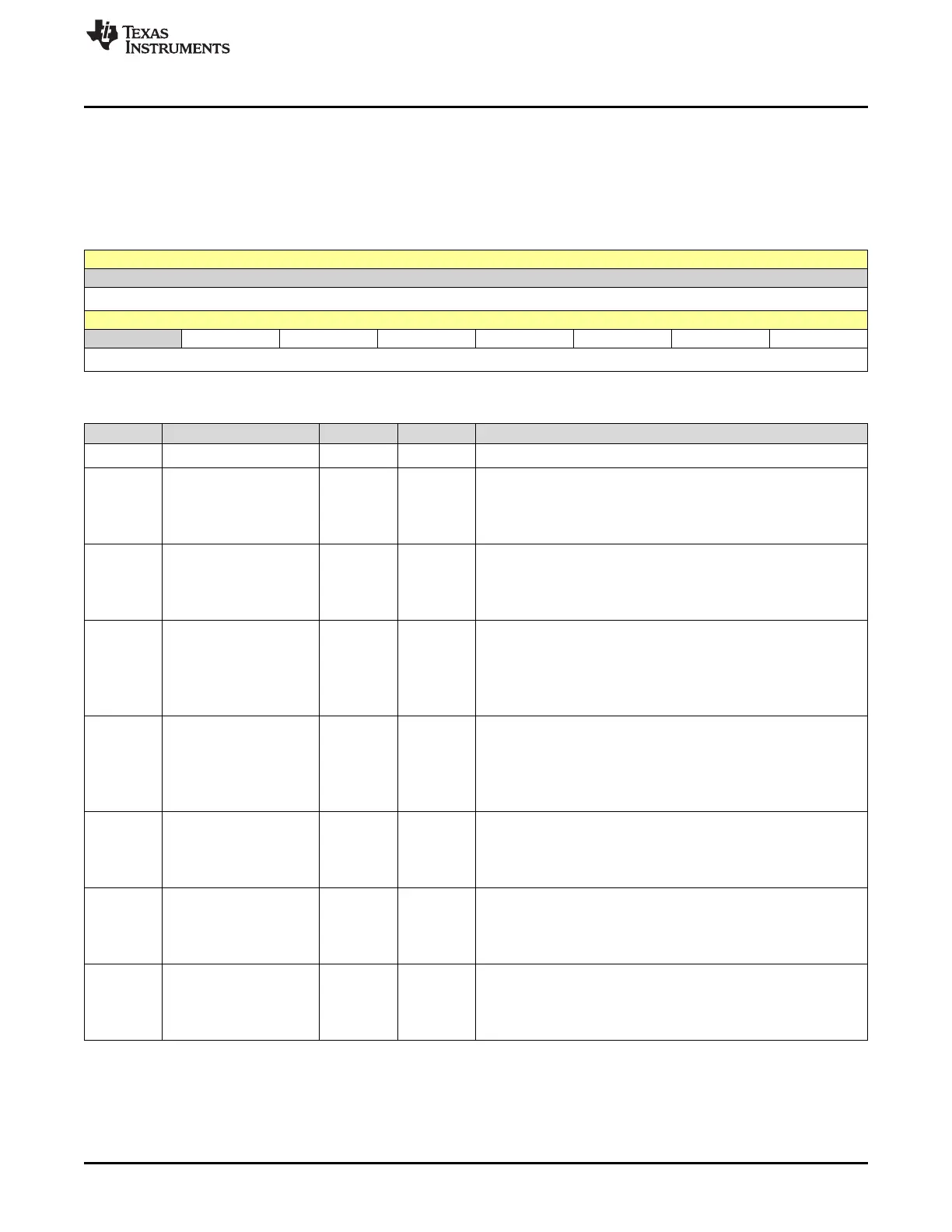

11.6.2.2 I2CIER Register (Offset = 1h) [reset = 0h]

I2CIER is shown in Figure 11-19 and described in Table 11-11.

Return to the Summary Table.

I2CIER is used by the CPU to individually enable or disable I2C interrupt requests.

Figure 11-19. I2CIER Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED AAS SCD XRDY RRDY ARDY NACK ARBL

R-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

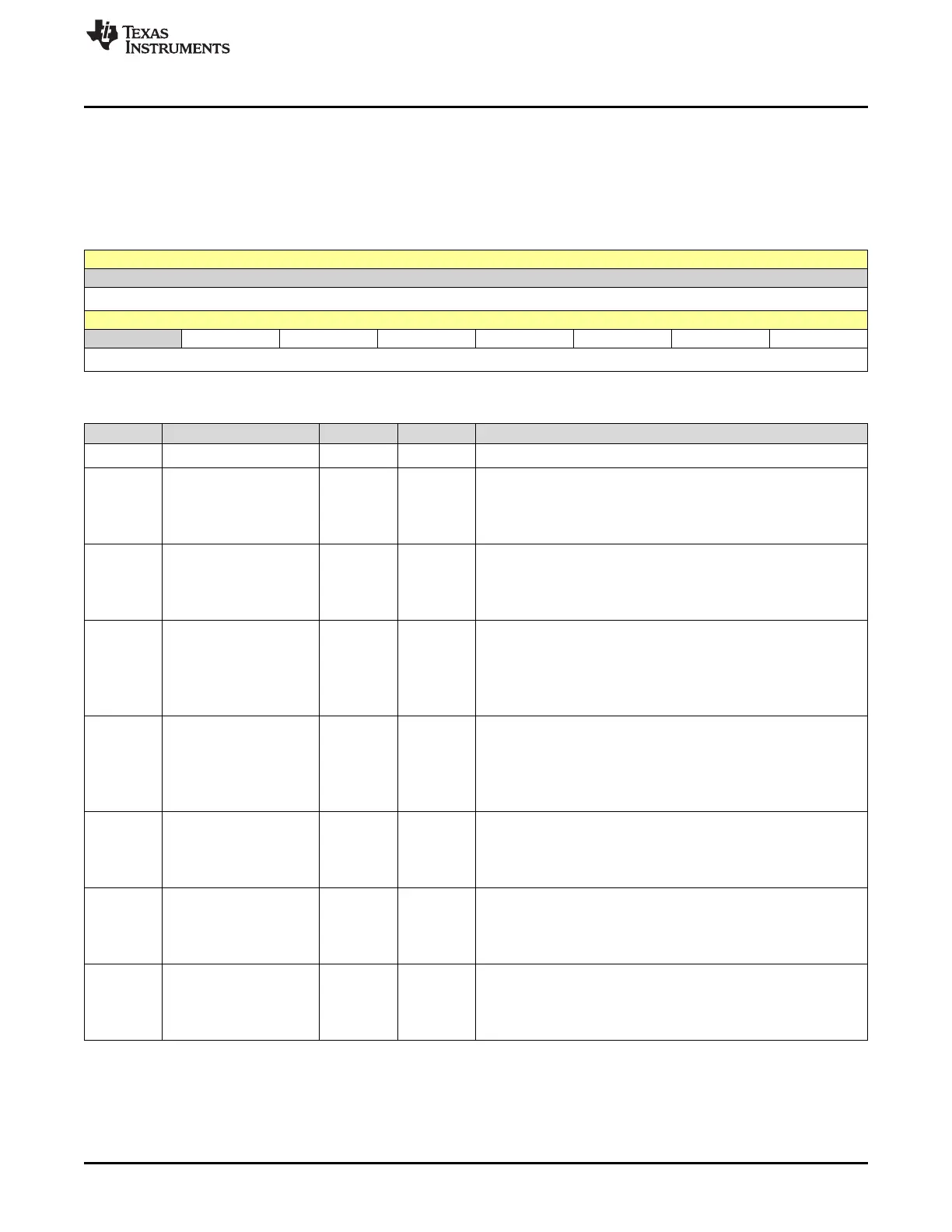

Table 11-11. I2CIER Register Field Descriptions

Bit Field Type Reset Description

15-7 RESERVED R 0h

Reserved

6 AAS R/W 0h

Addressed as slave interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt request disabled

1h (R/W) = Interrupt request enabled

5 SCD R/W 0h

Stop condition detected interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt request disabled

1h (R/W) = Interrupt request enabled

4 XRDY R/W 0h

Transmit-data-ready interrupt enable bit.

This bit should not be set when using FIFO mode.

Reset type: SYSRSn

0h (R/W) = Interrupt request disabled

1h (R/W) = Interrupt request enabled

3 RRDY R/W 0h

Receive-data-ready interrupt enable bit.

This bit should not be set when using FIFO mode.

Reset type: SYSRSn

0h (R/W) = Interrupt request disabled

1h (R/W) = Interrupt request enabled

2 ARDY R/W 0h

Register-access-ready interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt request disabled

1h (R/W) = Interrupt request enabled

1 NACK R/W 0h

No-acknowledgment interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt request disabled

1h (R/W) = Interrupt request enabled

0 ARBL R/W 0h

Arbitration-lost interrupt enable

Reset type: SYSRSn

0h (R/W) = Interrupt request disabled

1h (R/W) = Interrupt request enabled

Loading...

Loading...