www.ti.com

eCAP Registers

379

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Capture (eCAP)

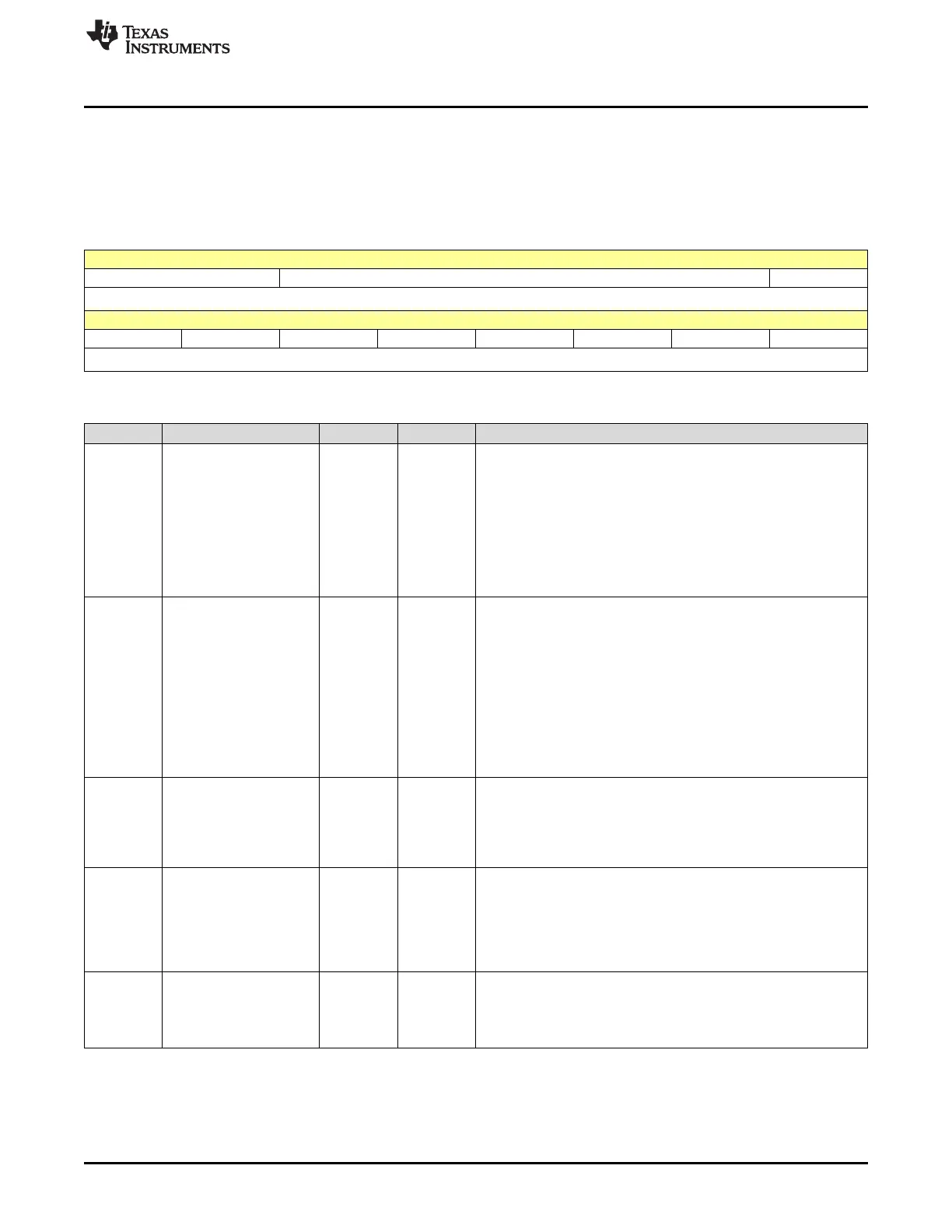

5.8.2.7 ECCTL1 Register (Offset = 14h) [reset = 0h]

ECCTL1 is shown in Figure 5-24 and described in Table 5-10.

Return to the Summary Table.

Capture Control Register 1

Figure 5-24. ECCTL1 Register

15 14 13 12 11 10 9 8

FREE_SOFT PRESCALE CAPLDEN

R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

CTRRST4 CAP4POL CTRRST3 CAP3POL CTRRST2 CAP2POL CTRRST1 CAP1POL

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

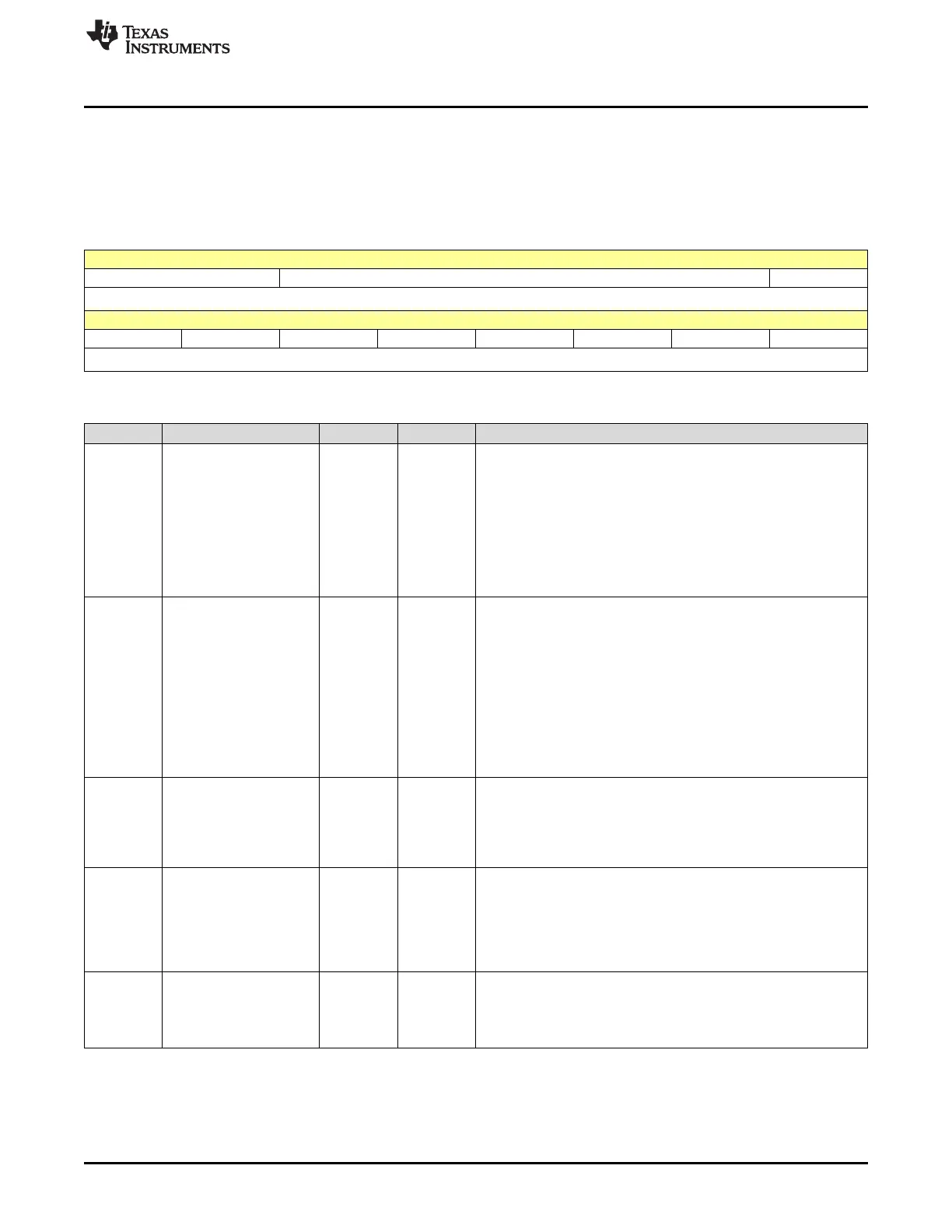

Table 5-10. ECCTL1 Register Field Descriptions

Bit Field Type Reset Description

15-14 FREE_SOFT R/W 0h

Emulation Control

Reset type: SYSRSn

0h (R/W) = TSCTR counter stops immediately on emulation

suspend

1h (R/W) = TSCTR counter runs until = 0

2h (R/W) = TSCTR counter is unaffected by emulation suspend

(Run Free)

3h (R/W) = TSCTR counter is unaffected by emulation suspend

(Run Free)

13-9 PRESCALE R/W 0h

Event Filter prescale select

Reset type: SYSRSn

0h (R/W) = Divide by 1 (i.e,. no prescale, by-pass the prescaler)

1h (R/W) = Divide by 2

2h (R/W) = Divide by 4

3h (R/W) = Divide by 6

4h (R/W) = Divide by 8

5h (R/W) = Divide by 10

1Eh (R/W) = Divide by 60

1Fh (R/W) = Divide by 62

8 CAPLDEN R/W 0h

Enable Loading of CAP1-4 registers on a capture event. Note that

this bit does not disable CEVTn events from being generated.

Reset type: SYSRSn

0h (R/W) = Disable CAP1-4 register loads at capture event time.

1h (R/W) = Enable CAP1-4 register loads at capture event time.

7 CTRRST4 R/W 0h

Counter Reset on Capture Event 4

Reset type: SYSRSn

0h (R/W) = Do not reset counter on Capture Event 4 (absolute time

stamp operation)

1h (R/W) = Reset counter after Capture Event 4 time-stamp has

been captured (used in difference mode operation)

6 CAP4POL R/W 0h

Capture Event 4 Polarity select

Reset type: SYSRSn

0h (R/W) = Capture Event 4 triggered on a rising edge (RE)

1h (R/W) = Capture Event 4 triggered on a falling edge (FE)

Loading...

Loading...