eCAP Registers

www.ti.com

380

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Capture (eCAP)

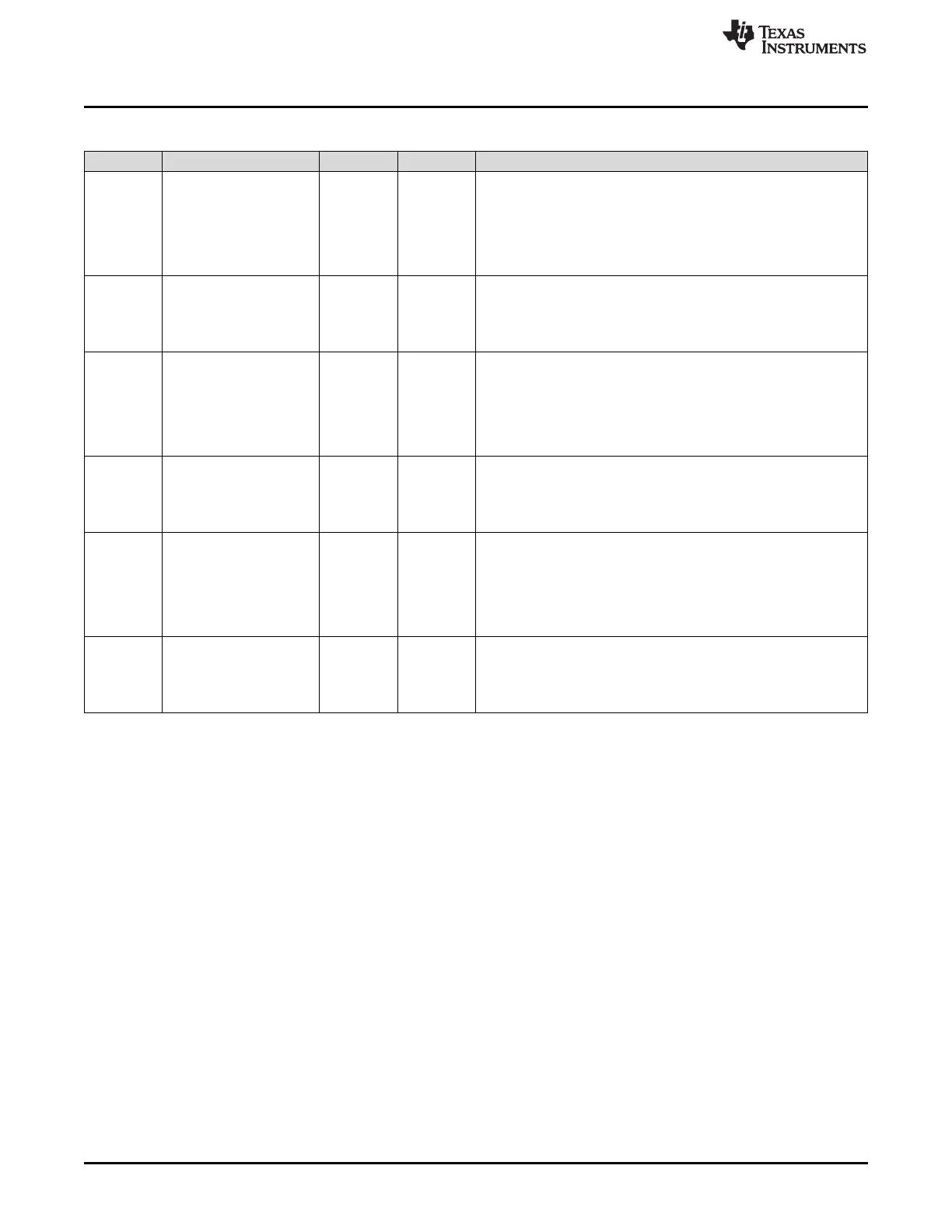

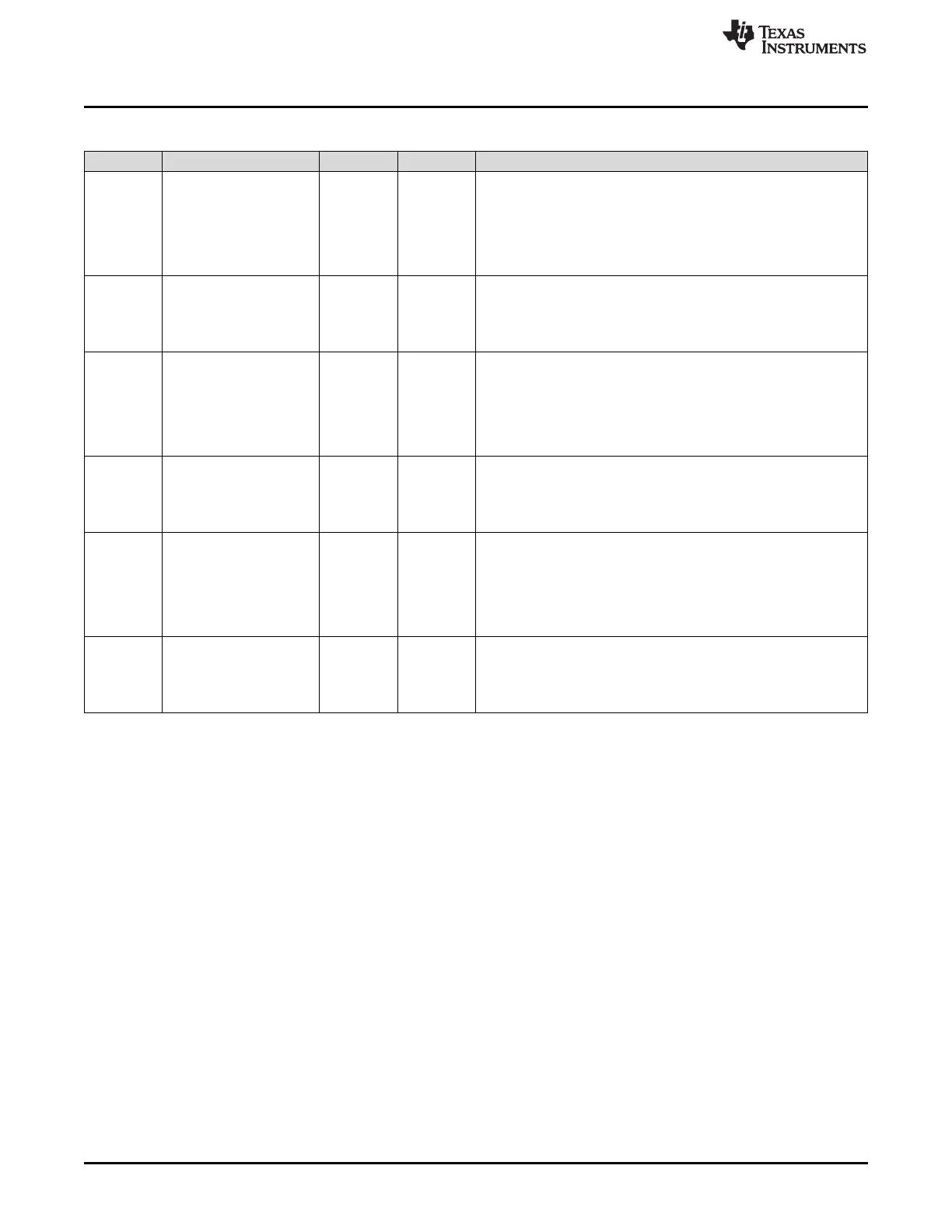

Table 5-10. ECCTL1 Register Field Descriptions (continued)

Bit Field Type Reset Description

5 CTRRST3 R/W 0h

Counter Reset on Capture Event 3

Reset type: SYSRSn

0h (R/W) = Do not reset counter on Capture Event 3 (absolute time

stamp)

1h (R/W) = Reset counter after Event 3 time-stamp has been

captured (used in difference mode operation)

4 CAP3POL R/W 0h

Capture Event 3 Polarity select

Reset type: SYSRSn

0h (R/W) = Capture Event 3 triggered on a rising edge (RE)

1h (R/W) = Capture Event 3 triggered on a falling edge (FE)

3 CTRRST2 R/W 0h

Counter Reset on Capture Event 2

Reset type: SYSRSn

0h (R/W) = Do not reset counter on Capture Event 2 (absolute time

stamp)

1h (R/W) = Reset counter after Event 2 time-stamp has been

captured (used in difference mode operation)

2 CAP2POL R/W 0h

Capture Event 2 Polarity select

Reset type: SYSRSn

0h (R/W) = Capture Event 2 triggered on a rising edge (RE)

1h (R/W) = Capture Event 2 triggered on a falling edge (FE)

1 CTRRST1 R/W 0h

Counter Reset on Capture Event 1

Reset type: SYSRSn

0h (R/W) = Do not reset counter on Capture Event 1 (absolute time

stamp)

1h (R/W) = Reset counter after Event 1 time-stamp has been

captured (used in difference mode operation)

0 CAP1POL R/W 0h

Capture Event 1 Polarity select

Reset type: SYSRSn

0h (R/W) = Capture Event 1 triggered on a rising edge (RE)

1h (R/W) = Capture Event 1 triggered on a falling edge (FE)

Loading...

Loading...