www.ti.com

McBSP Registers

765

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

12.15.9 Pin Control Register (PCR)

Each McBSP has one pin control register (PCR). Table 12-91 describes the bits of PCR. This register

enables you to:

• Choose a frame-synchronization mode for the transmitter (FSXM) and for the receiver (FSRM)

• Choose a clock mode for transmitter (CLKXM) and for the receiver (CLKRM)

• Select the input clock source for the sample rate generator (SCLKME, in conjunction with the CLKSM

bit of SRGR2)

• Choose whether frame-synchronization signals are active low or active high (FSXP for transmission,

FSRP for reception)

• Specify whether data is sampled on the falling edge or the rising edge of the clock signals (CLKXP for

transmission, CLKRP for reception)

The pin control register (PCR) is shown in Figure 12-79 and described in Table 12-91.

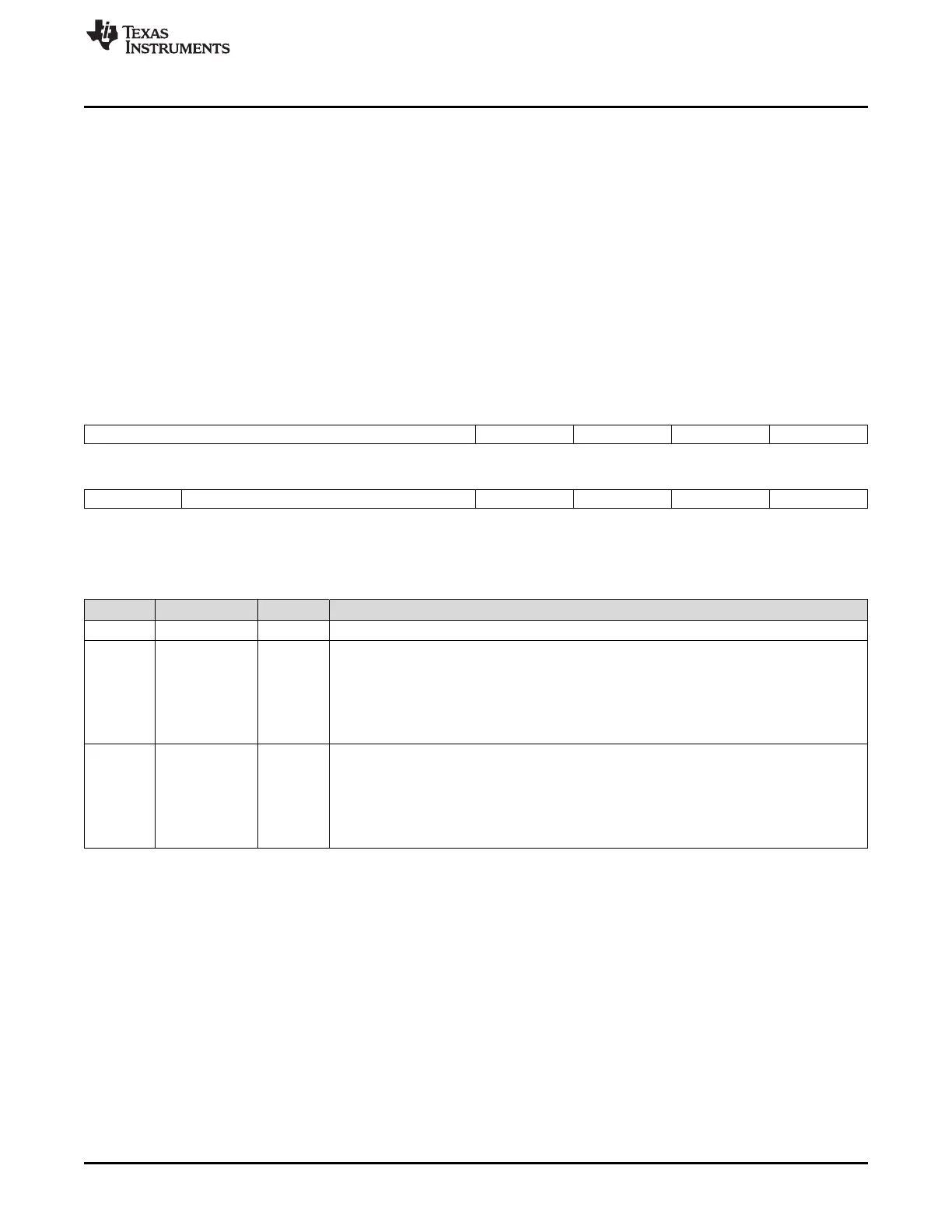

Figure 12-79. Pin Control Register (PCR)

15 12 11 10 9 8

Reserved FSXM FSRM CLKXM CLKRM

R-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 4 3 2 1 0

SCLKME Reserved FSXP FSRP CLKXP CLKRP

R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

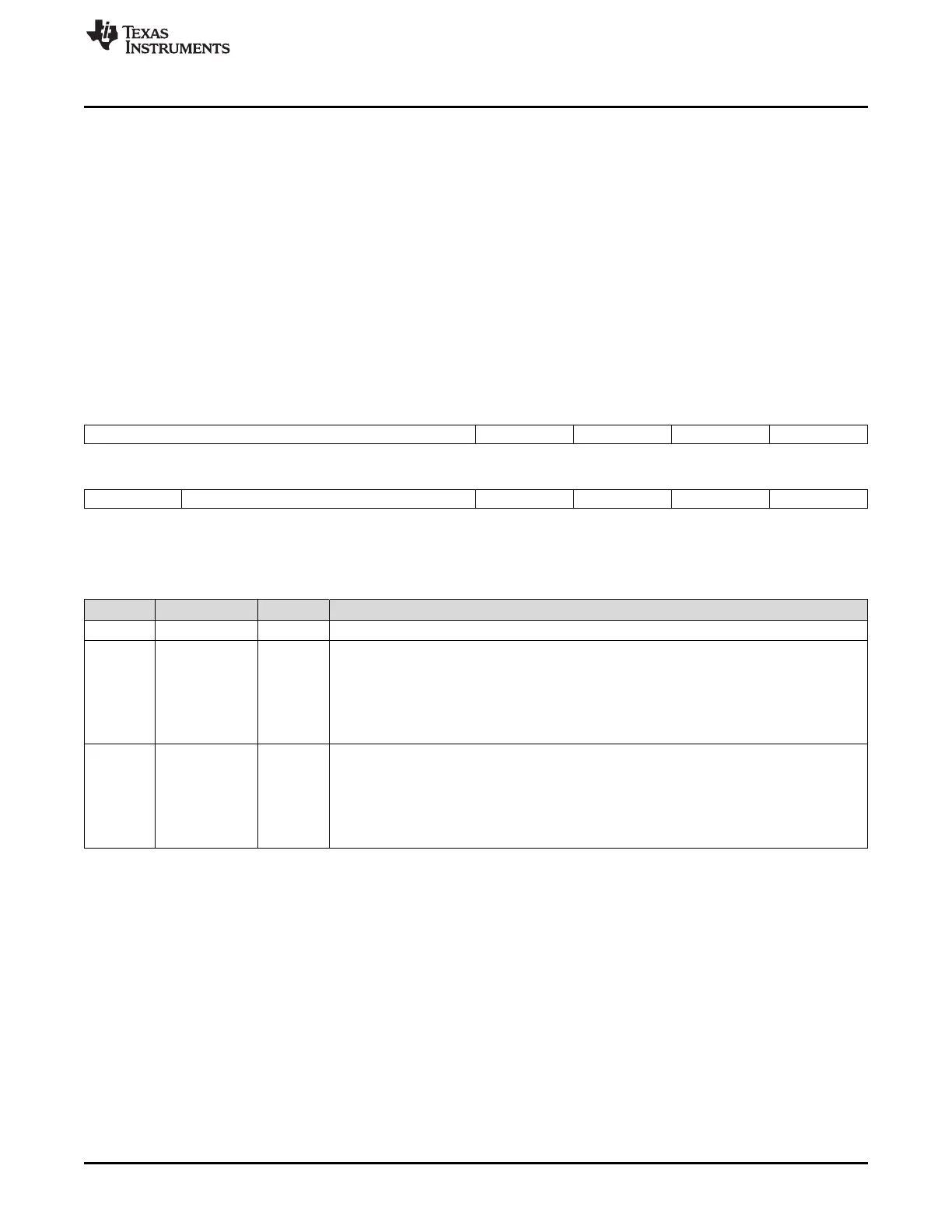

Table 12-91. Pin Control Register (PCR) Field Descriptions

Bit Field Value Description

15:12 Reserved 0 Reserved bit (not available for your use). It is a read-only bit and returns a 0 when read.

11 FSXM Transmit frame-synchronization mode bit. FSXM determines whether transmit frame-

synchronization pulses are supplied externally or internally. The polarity of the signal on the

FSX pin is determined by the FSXP bit.

0 Transmit frame synchronization is supplied by an external source via the FSX pin.

1 Transmit frame synchronization is generated internally by the Sample Rate generator, as

determined by the FSGM bit of SRGR2.

10 FSRM Receive frame-synchronization mode bit. FSRM determines whether receive frame-

synchronization pulses are supplied externally or internally. The polarity of the signal on the

FSR pin is determined by the FSRP bit.

0 Receive frame synchronization is supplied by an external source via the FSR pin.

1 Receive frame synchronization is supplied by the sample rate generator. FSR is an output pin

reflecting internal FSR, except when GSYNC = 1 in SRGR2.

Loading...

Loading...