www.ti.com

Peripheral Interrupt Expansion (PIE)

157

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

NOTE:

1. To clear a CPU IFR bit, you must write a zero to it, not a one.

2. When a maskable interrupt is acknowledged, only the IFR bit is cleared automatically.

The flag bit in the corresponding peripheral control register is not cleared. If an

application requires that the control register flag be cleared, the bit must be cleared by

software.

3. When an interrupt is requested by an INTR instruction and the corresponding IFR bit is

set, the CPU does not clear the bit automatically. If an application requires that the IFR

bit be cleared, the bit must be cleared by software.

4. IMR and IFR registers pertain to core-level interrupts. All peripherals have their own

interrupt mask and flag bits in their respective control/configuration registers. Note that

several peripheral interrupts are grouped under one core-level interrupt.

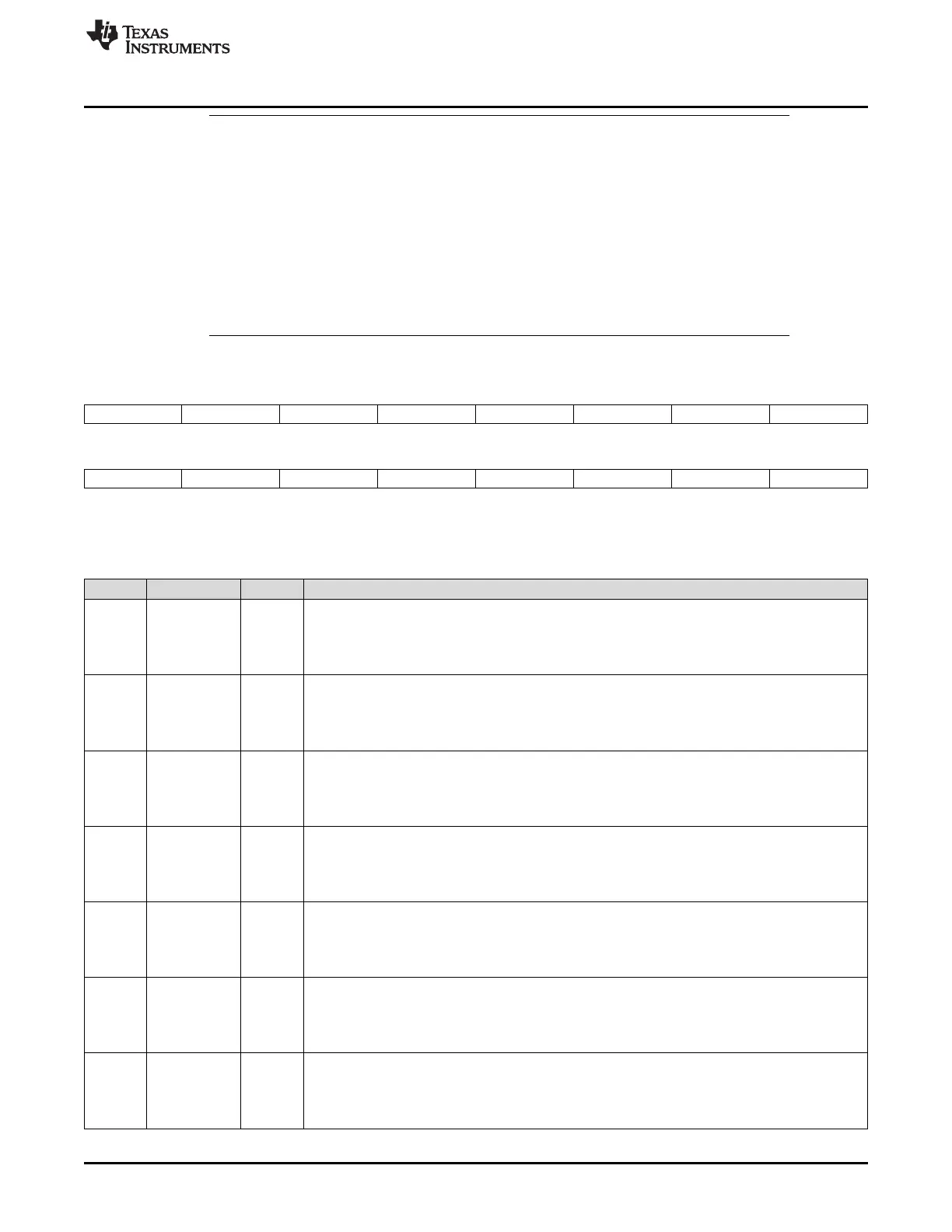

Figure 1-88. Interrupt Flag Register (IFR) — CPU Register

15 14 13 12 11 10 9 8

RTOSINT DLOGINT INT14 INT13 INT12 INT11 INT10 INT9

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

INT8 INT7 INT6 INT5 INT4 INT3 INT2 INT1

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

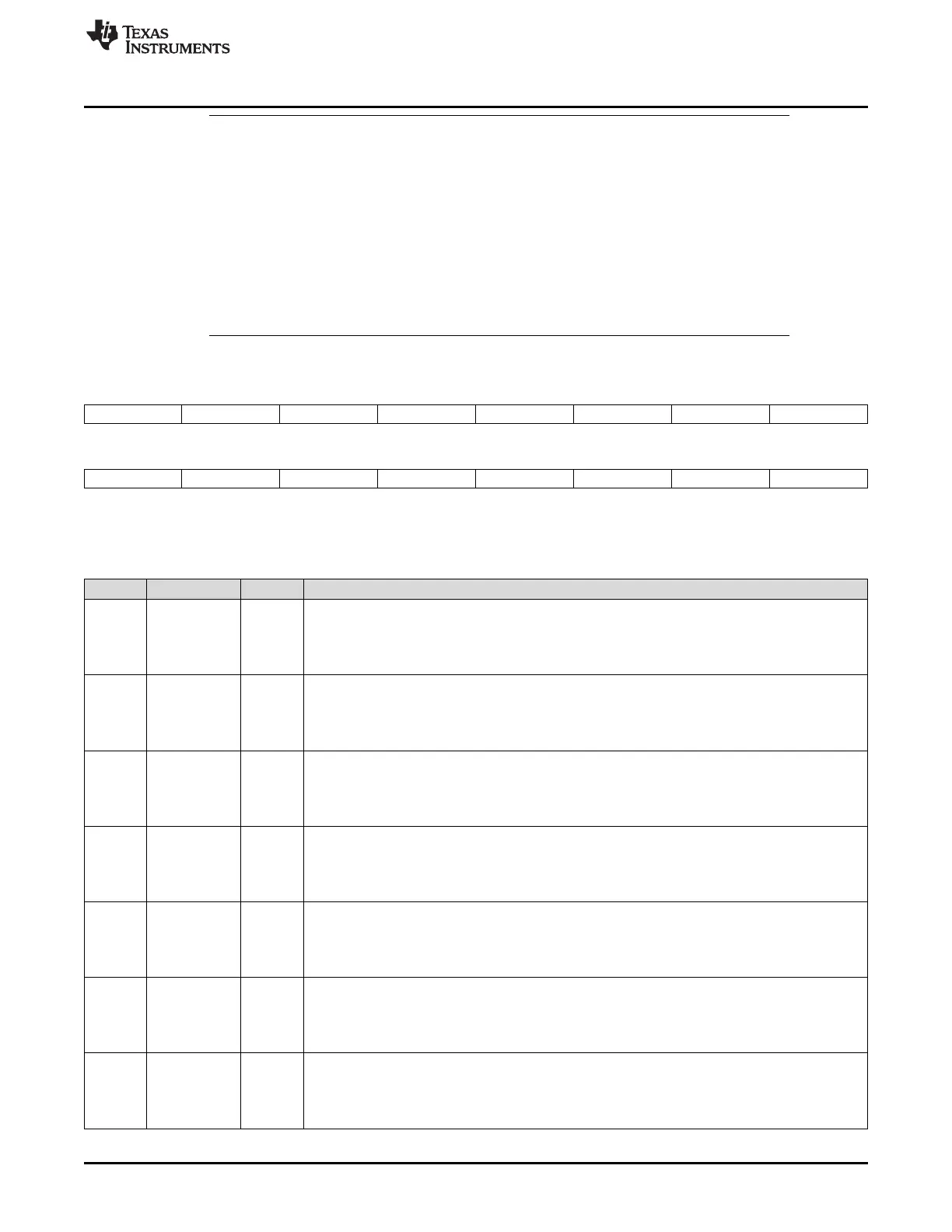

Table 1-118. Interrupt Flag Register (IFR) — CPU Register Field Descriptions

Bits Field Value Description

15 RTOSINT Real-time operating system flag. RTOSINT is the flag for RTOS interrupts.

0 No RTOS interrupt is pending

1 At least one RTOS interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

14 DLOGINT Data logging interrupt fag. DLOGINT is the flag for data logging interrupts.

0 No DLOGINT is pending

1 At least one DLOGINT interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

13 INT14 Interrupt 14 flag. INT14 is the flag for interrupts connected to CPU interrupt level INT14.

0 No INT14 interrupt is pending

1 At least one INT14 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

12 INT13 Interrupt 13 flag. INT13 is the flag for interrupts connected to CPU interrupt level INT13I.

0 No INT13 interrupt is pending

1 At least one INT13 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

11 INT12 Interrupt 12 flag. INT12 is the flag for interrupts connected to CPU interrupt level INT12.

0 No INT12 interrupt is pending

1 At least one INT12 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

10 INT11 Interrupt 11 flag. INT11 is the flag for interrupts connected to CPU interrupt level INT11.

0 No INT11 interrupt is pending

1 At least one INT11 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

9 INT10 Interrupt 10 flag. INT10 is the flag for interrupts connected to CPU interrupt level INT10.

0 No INT10 interrupt is pending

1 At least one INT6 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

Loading...

Loading...