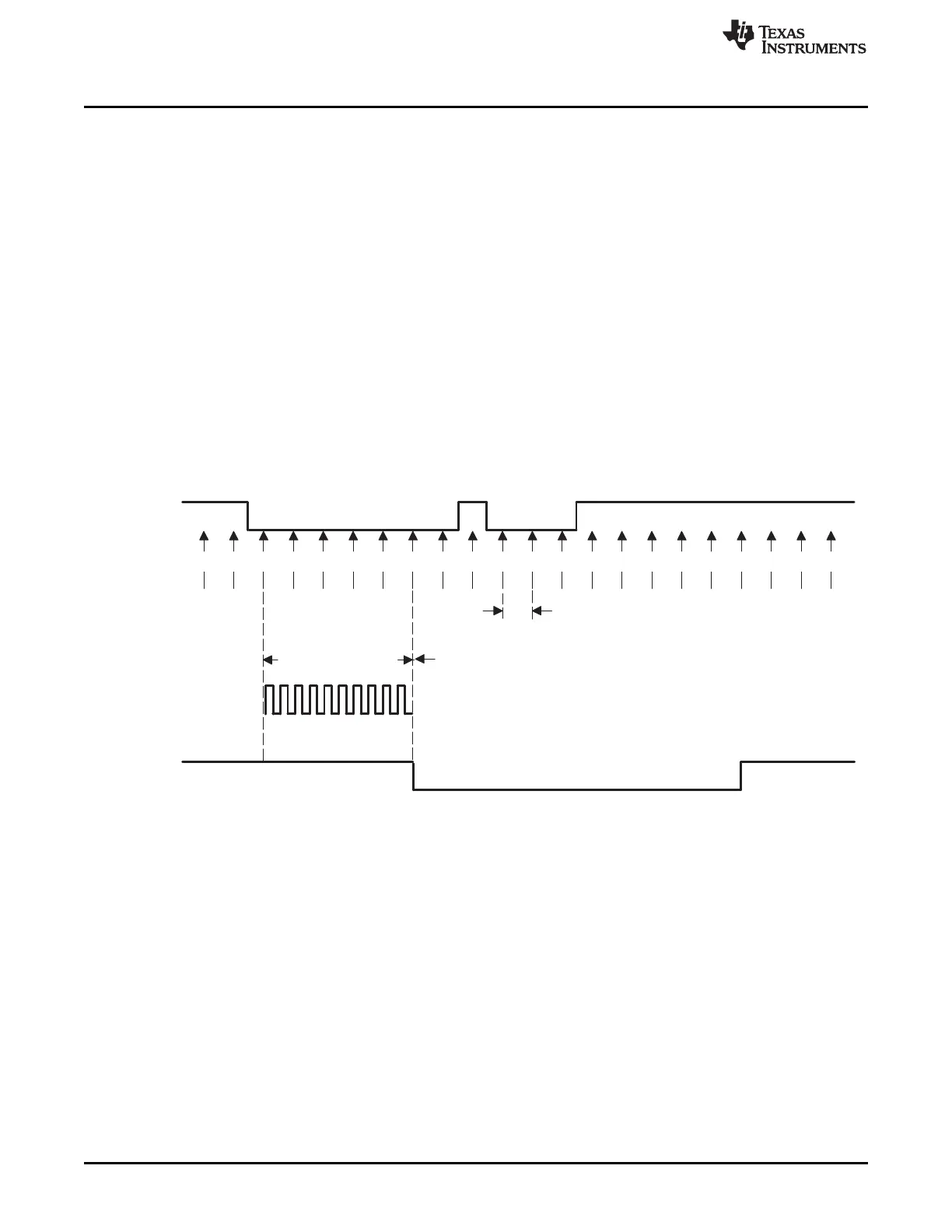

GPIO Signal

1

Sampling Window

Output From

Qualifier

1 1 1 1 1 1 1 1 1 1 10 0 0 0 0 0 0 0 0 0

SYSCLKOUT

QUALPRD = 1

(SYSCLKOUT/2)

(SYSCLKOUT cycle * 2 * QUALPRD) * 5

(C)

)

(A)

GPxQSELn = 1,0 (6 samples)

Sampling Period determined

by GPxCTRL[QUALPRD]

(B)

A. This glitch will be ignored by the input qualifier. The QUALPRD bit field specifies the qualification sampling period. It can vary from 00 to

0xFF. If QUALPRD = 00, then the sampling period is 1 SYSCLKOUT cycle. For any other value “n”, the qualification sampling period in 2n

SYSCLKOUT cycles (i.e., at every 2n SYSCLKOUT cycles, the GPIO pin will be sampled).

B. The qualification period selected via the GPxCTRL register applies to groups of 8 GPIO pins.

C. The qualification block can take either three or six samples. The GPxQSELn Register selects which sample mode is used.

D. In the example shown, for the qualifier to detect the change, the input should be stable for 10 SYSCLKOUT cycles or greater. In other words,

the inputs should be stable for (5 x QUALPRD x 2) SYSCLKOUT cycles. That would ensure 5 sampling periods for detection to occur. Since

external signals are driven asynchronously, an 13-SYSCLKOUT-wide pulse ensures reliable recognition.

(D)

t

w(SP)

t

w(IQSW)

General-Purpose Input/Output (GPIO)

www.ti.com

98

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

Example Qualification Window:

For the example shown in Figure 1-46, the input qualification has been configured as follows:

• GPxQSEL1/2 = 1,0. This indicates a six-sample qualification.

• GPxCTRL[QUALPRDn] = 1. The sampling period is t

w

(SP) = 2 × GPxCTRL[QUALPRDn] × T

SYSCLKOUT

.

This configuration results in the following:

• The width of the sampling window is: .

t

w

(IQSW) = 5 × t

w

(SP) = 5 × 2 × GPxCTRL[QUALPRDn] × T

SYSCLKOUT

or 5 × 2 × T

SYSCLKOUT

• If, for example, T

SYSCLKOUT

= 6.67 ns, then the duration of the sampling window is:

t

w

(IQSW) = 5 × 2 × 6.67 ns = 67 ns.

• To account for the asynchronous nature of the input relative to the sampling period and SYSCLKOUT,

up to an additional sampling period, t

w

(SP), + T

SYSCLKOUT

may be required to detect a change in the

input signal. For this example:

t

w

(SP) + T

SYSCLKOUT

= 13.34 ns + 6.67 ns = 20 ns

• In Figure 1-46, the glitch (A) is shorter then the qualification window and will be ignored by the input

qualifier.

Figure 1-46. Input Qualifier Clock Cycles

Loading...

Loading...