www.ti.com

I2C Registers

637

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

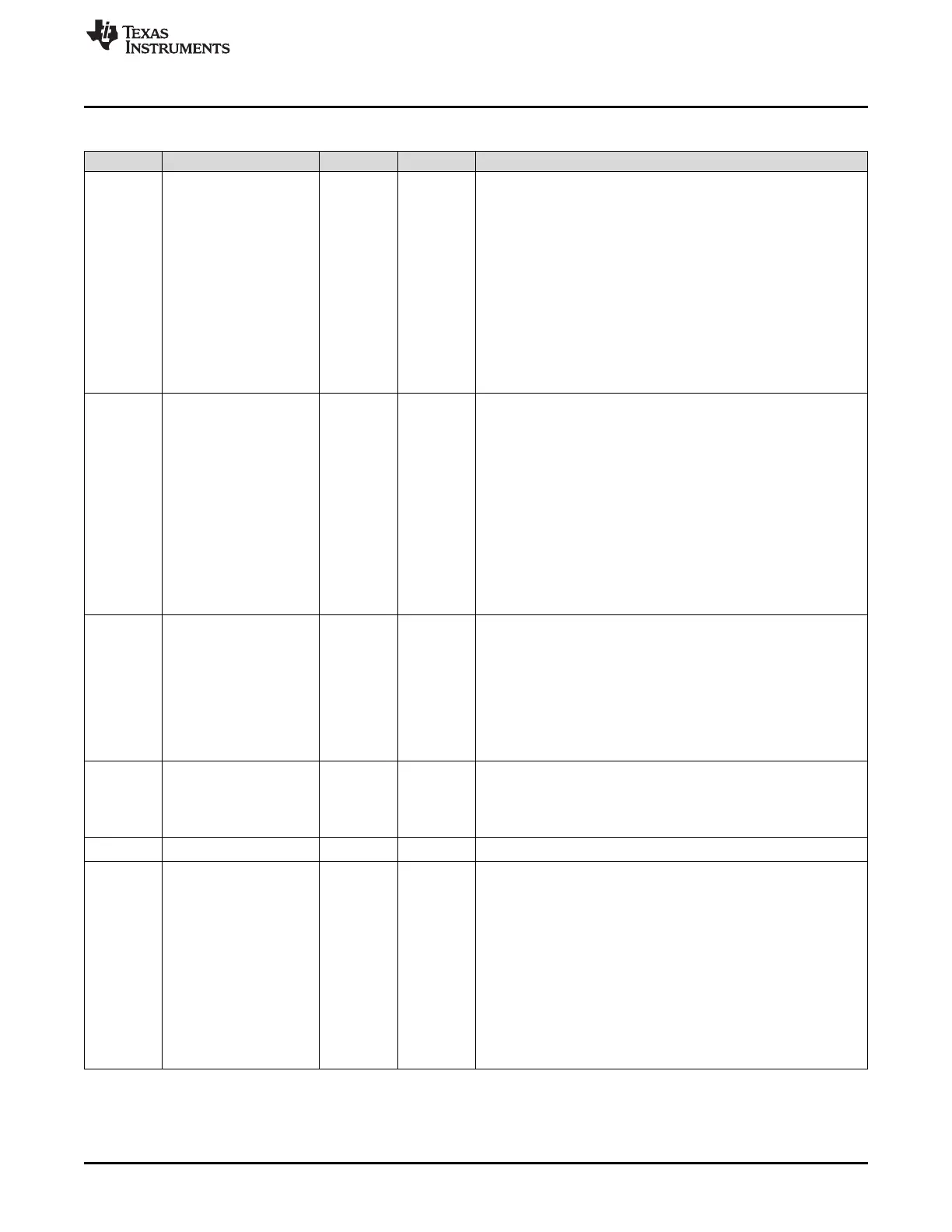

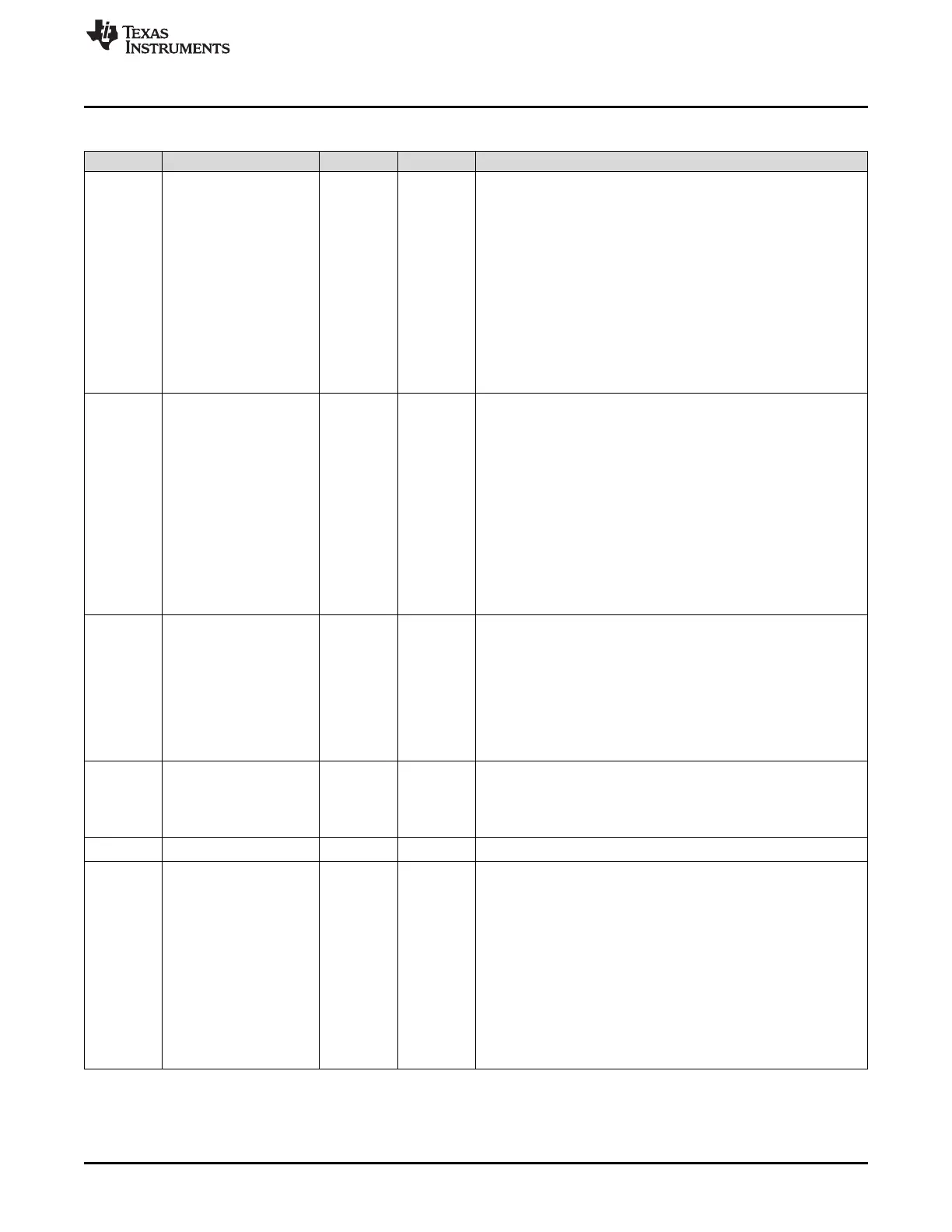

Table 11-12. I2CSTR Register Field Descriptions (continued)

Bit Field Type Reset Description

11 RSFULL R 0h

Receive shift register full bit.

RSFULL indicates an overrun condition during reception. Overrun

occurs when new data is received into the shift register (I2CRSR)

and the old data has not been read from the receive register

(I2CDRR). As new bits arrive from the SDA pin, they overwrite the

bits in I2CRSR. The new data will not be copied to ICDRR until the

previous data is read.

Reset type: SYSRSn

0h (R/W) = No overrun detected. RSFULL is cleared by any one of

the following events:

- I2CDRR is read is read by the CPU. Emulator reads of the

I2CDRR do not affect this bit.

- The I2C module is reset.

1h (R/W) = Overrun detected

10 XSMT R 1h

Transmit shift register empty bit.

XSMT = 0 indicates that the transmitter has experienced underflow.

Underflow occurs when the transmit shift register (I2CXSR) is empty

but the data transmit register (I2CDXR) has not been loaded since

the last I2CDXR-to-I2CXSR transfer. The next I2CDXR-to-I2CXSR

transfer will not occur until new data is in I2CDXR. If new data is not

transferred in time, the previous data may be re-transmitted on the

SDA pin.

Reset type: SYSRSn

0h (R/W) = Underflow detected (empty)

1h (R/W) = No underflow detected (not empty). XSMT is set by one

of the following events:

- Data is written to I2CDXR.

- The I2C module is reset

9 AAS R 0h

Addressed-as-slave bit

Reset type: SYSRSn

0h (R/W) = In the 7-bit addressing mode, the AAS bit is cleared

when receiving a NACK, a STOP condition, or a repeated START

condition. In the 10-bit addressing mode, the AAS bit is cleared

when receiving a NACK, a STOP condition, or by a slave address

different from the I2C peripheral's own slave address.

1h (R/W) = The I2C module has recognized its own slave address

or an address of all zeros (general call).

8 AD0 R 0h

Address 0 bits

Reset type: SYSRSn

0h (R/W) = AD0 has been cleared by a START or STOP condition.

1h (R/W) = An address of all zeros (general call) is detected.

7-6 RESERVED R/W 0h

Reserved

5 SCD R/W1C 0h

Stop condition detected bit.

SCD is set when the I2C sends or receives a STOP condition. The

I2C module delays clearing of the I2CMDR[STP] bit until the SCD bit

is set.

Reset type: SYSRSn

0h (R/W) = STOP condition not detected since SCD was last

cleared. SCD is cleared by any one of the following events:

- I2CISRC is read by the CPU when it contains the value 110b

(stop condition detected). Emulator reads of the I2CISRC do not

affect this bit.

- SCD is manually cleared. To clear this bit, write a 1 to it.

- The I2C module is reset.

1h (R/W) = A STOP condition has been detected on the I2C bus.

Loading...

Loading...