Flash and OTP Memory Blocks

www.ti.com

48

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

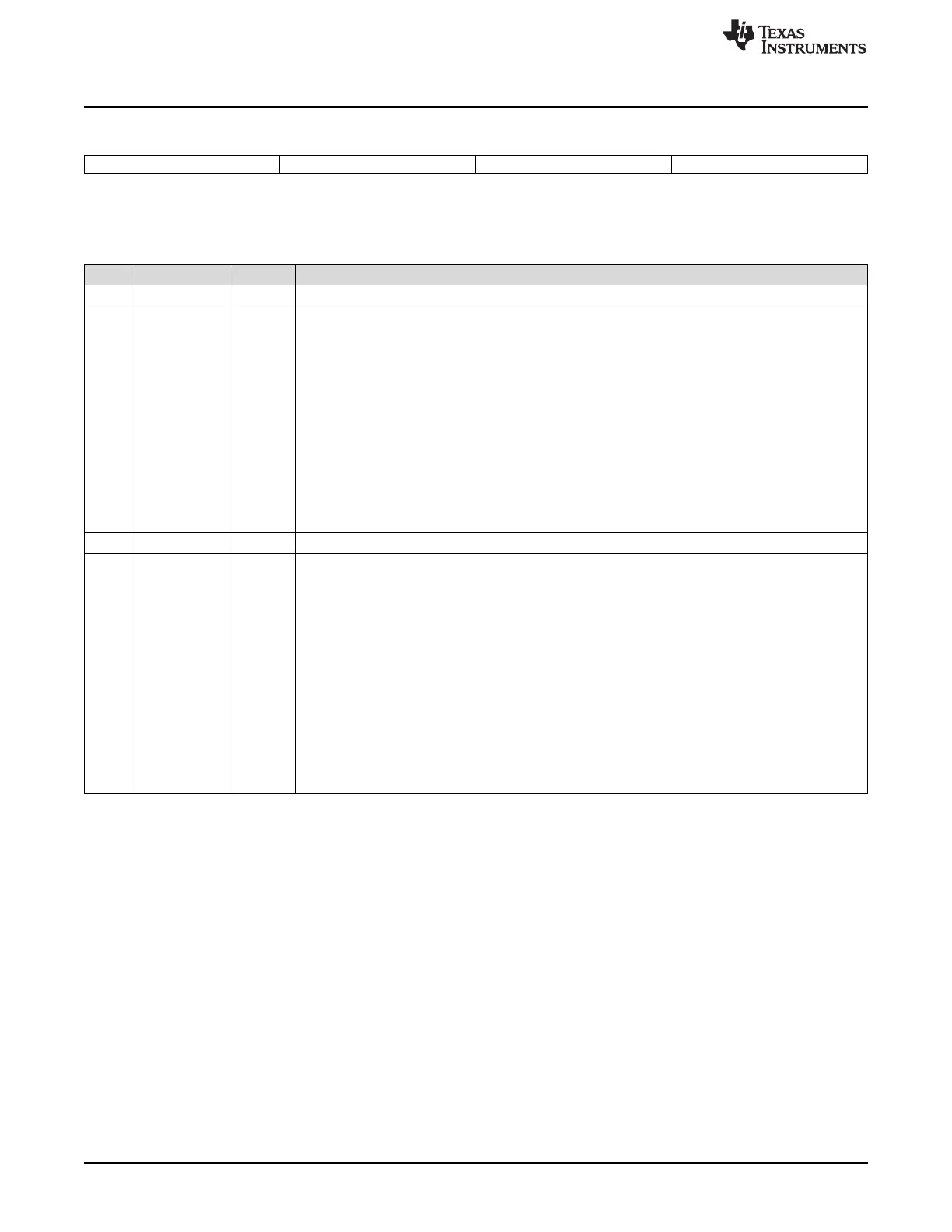

Figure 1-9. Flash Wait-State Register (FBANKWAIT)

15 12 11 8 7 4 3 0

Reserved PAGEWAIT Reserved RANDWAIT

R-0 R/W-0xF R-0 R/W-0xF

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

(2)

This register is protected by the Code Security Module (CSM). See Section 1.2 for more information.

(3)

When writing to this register, follow the procedure described in Section 1.1.3.4.

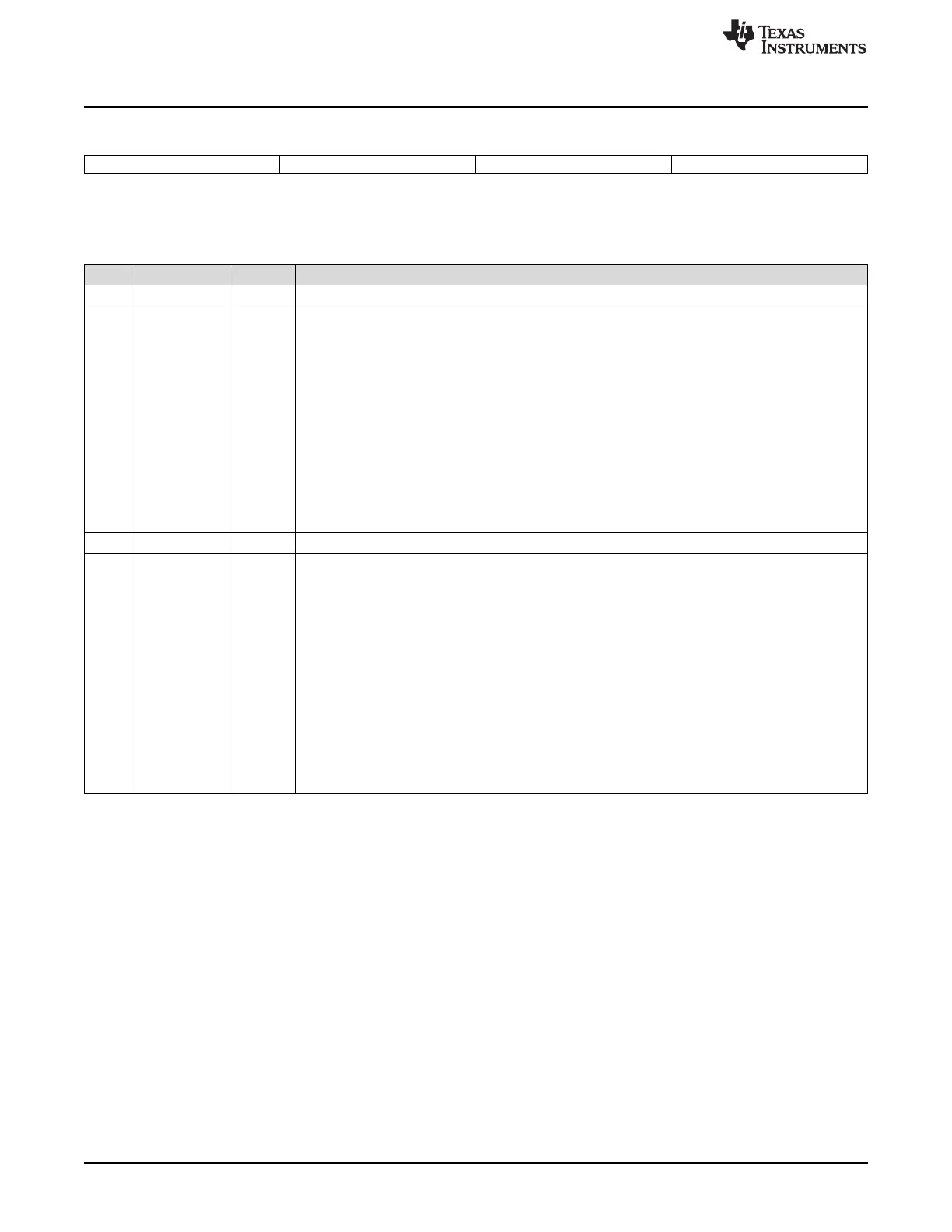

Table 1-7. Flash Wait-State Register (FBANKWAIT) Field Descriptions

Bits Field Value Description

(1) (2) (3)

15-12 Reserved Reserved

11-8 PAGEWAIT Flash Paged Read Wait States. These register bits specify the number of wait states for a paged

read operation in CPU clock cycles (0..15 SYSCLKOUT cycles) to the flash bank. See

Section 1.1.3.1 for more information.

See the device-specific data manual for the minimum time required for a PAGED flash access.

You must set RANDWAIT to a value greater than or equal to the PAGEWAIT setting. No hardware is

provided to detect a PAGEWAIT value that is greater then RANDWAIT.

0000 Illegal value. PAGEWAIT must be set greater then 0.

0001 One wait state per paged flash access or a total of two SYSCLKOUT cycles per access.

0010 Two wait states per paged flash access or a total of three SYSCLKOUT cycles per access.

0011 Three wait states per paged flash access or a total of four SYSCLKOUT cycles per access.

. . . . . .

1111 15 wait states per paged flash access or a total of 16 SYSCLKOUT cycles per access. (default)

7-4 Reserved Reserved

3-0 RANDWAIT Flash Random Read Wait States. These register bits specify the number of wait states for a random

read operation in CPU clock cycles (1..15 SYSCLKOUT cycles) to the flash bank. See

Section 1.1.3.1 for more information.

See the device-specific data manual for the minimum time required for a RANDOM flash access.

RANDWAIT must be set greater than 0. That is, at least 1 random wait state must be used. In

addition, you must set RANDWAIT to a value greater than or equal to the PAGEWAIT setting. The

device will not detect and correct a PAGEWAIT value that is greater then RANDWAIT.

0000 Illegal value. RANDWAIT must be set greater then 0.

0001 One wait state per random flash access or a total of two SYSCLKOUT cycles per access.

0010 Two wait states per random flash access or a total of three SYSCLKOUT cycles per access.

0011 Three wait states per random flash access or a total of four SYSCLKOUT cycles per access.

. . . . . .

1111 15 wait states per random flash access or a total of 16 SYSCLKOUT cycles per access. (default)

Loading...

Loading...