WDINT

LPMINT

Watchdog

Low-PowerModels

Sync

SYSCLKOUT

WAKEINT

DMA

Clear

Peripherals

(SPI,SCI,I2C,CAN,McBSP

C )

(A)

,

ePWM ,eCAP,eQEP, AD

(A) (A)

DMA

XINT1

InterruptControl

XINT1CR(15:0)

XINT1CTR(15:0)

XINT1

Latch

MUX

GPIOXINT1SEL(4:0)

DMA

XINT2

InterruptControl

XINT2CR(15:0)

XINT2CTR(15:0)

XINT2

Latch

MUX

GPIOXINT2SEL(4:0)

ADC

XINT2SOC

DMA

TINT0

CPUTimer0

DMA

TINT2

CPUTimer2

CPUTimer1

MUX

TINT1

InterruptControl

XNMICR(15:0)

XNMICTR(15:0)

MUX

1

DMA

NMI

INT13

INT14

INT1

to

INT12

C28

Core

96Interrupts

PIE

XNMI_

XINT13

Latch

MUX

GPIOXNMISEL(4:0)

GPIO

Mux

GPIO0.int

GPIO31.int

www.ti.com

Peripheral Interrupt Expansion (PIE)

143

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

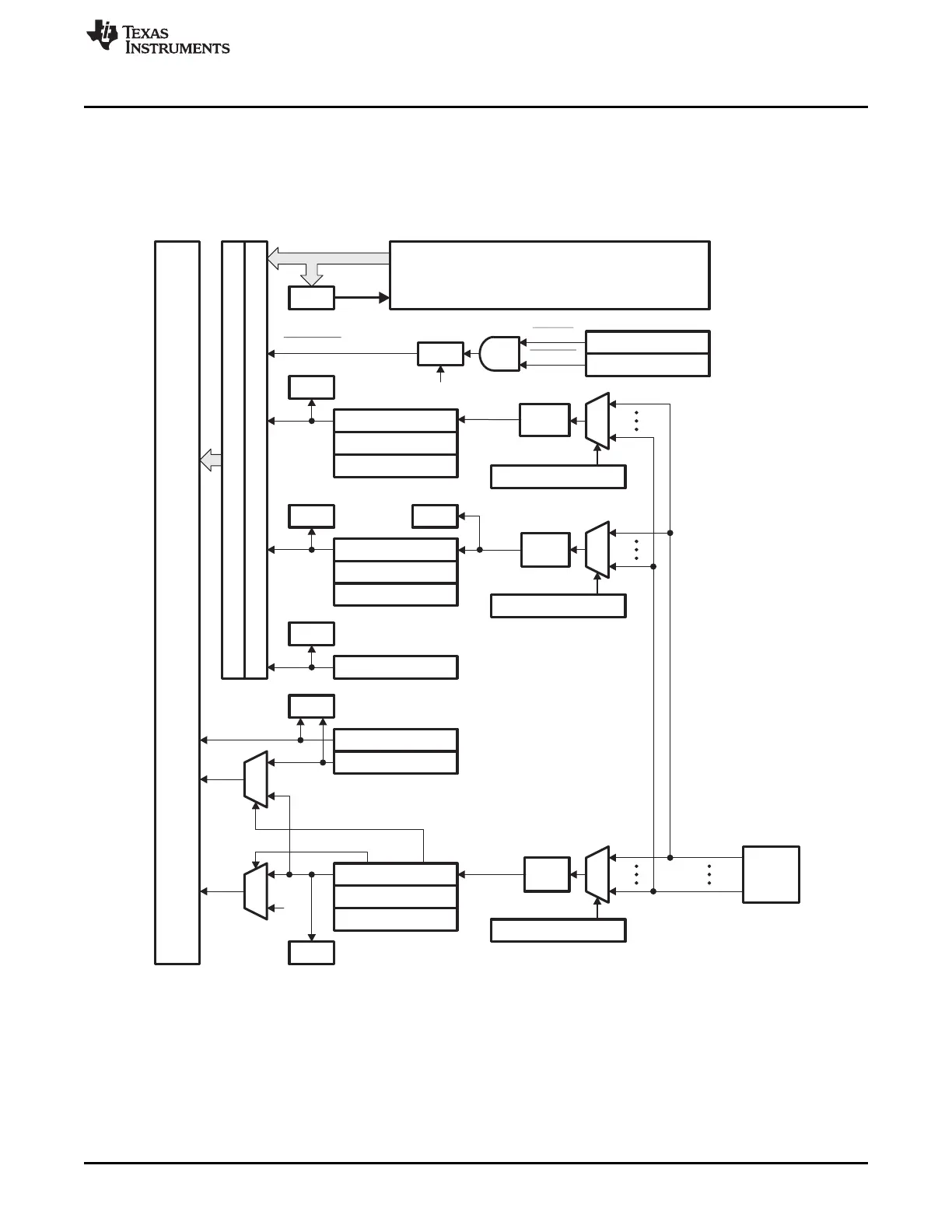

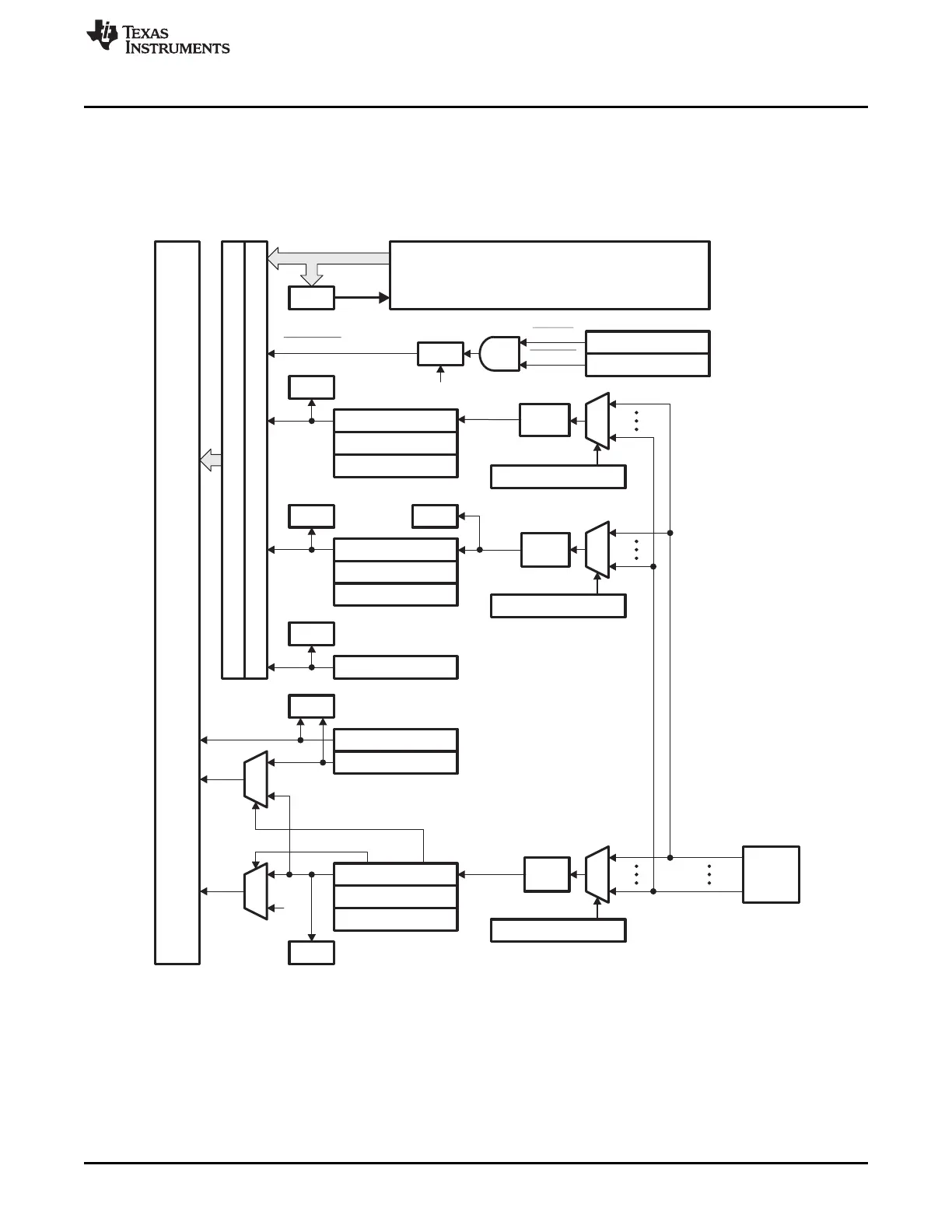

1.6.3 Interrupt Sources

Figure 1-81 shows how the various interrupt sources are multiplexed within the devices. This multiplexing

(MUX) scheme may not be exactly the same on all 28x devices. See the data manual of your particular

device for details.

Figure 1-81. PIE Interrupt Sources and External Interrupts XINT1/XINT2

A DMA accessible

Loading...

Loading...