CTR=PRD

TBPRD shadow (16)

TBPRD active (16)

Counter

up/down

(16 bit)

TBCNT

active (16)

TBCTL[PHSEN]

TBCTL[SWFSYNC]

(software forced sync)

EPWMxSYNCI

CTR=ZERO

CTR_Dir

CTR=CMPB

Disabled

Sync

in/out

select

Mux

TBCTL[SYNCOSEL]

EPWMxSYNCO

TBPHS active (24)

16

8

TBPHSHR (8)

Phase

control

Time−base (TB)

CTR=CMPA

CMPA active (24)

16

CMPA shadow (24)

Action

qualifier

(AQ)

8

16

Counter compare (CC)

CMPB active (16)

CTR=CMPB

CMPB shadow (16)

CMPAHR (8)

EPWMA

EPWMB

Dead

band

(DB) (PC)

chopper

PWM

zone

(TZ)

Trip

CTR = ZERO

EPWMxAO

EPWMxBO

EPWMxTZINT

TZ1 to TZ6

HiRes PWM (HRPWM)

CTR = PRD

CTR = ZERO

CTR = CMPB

CTR = CMPA

CTR_Dir

Event

trigger

and

interrupt

(ET)

EPWMxINT

EPWMxSOCA

EPWMxSOCB

CTR=ZERO

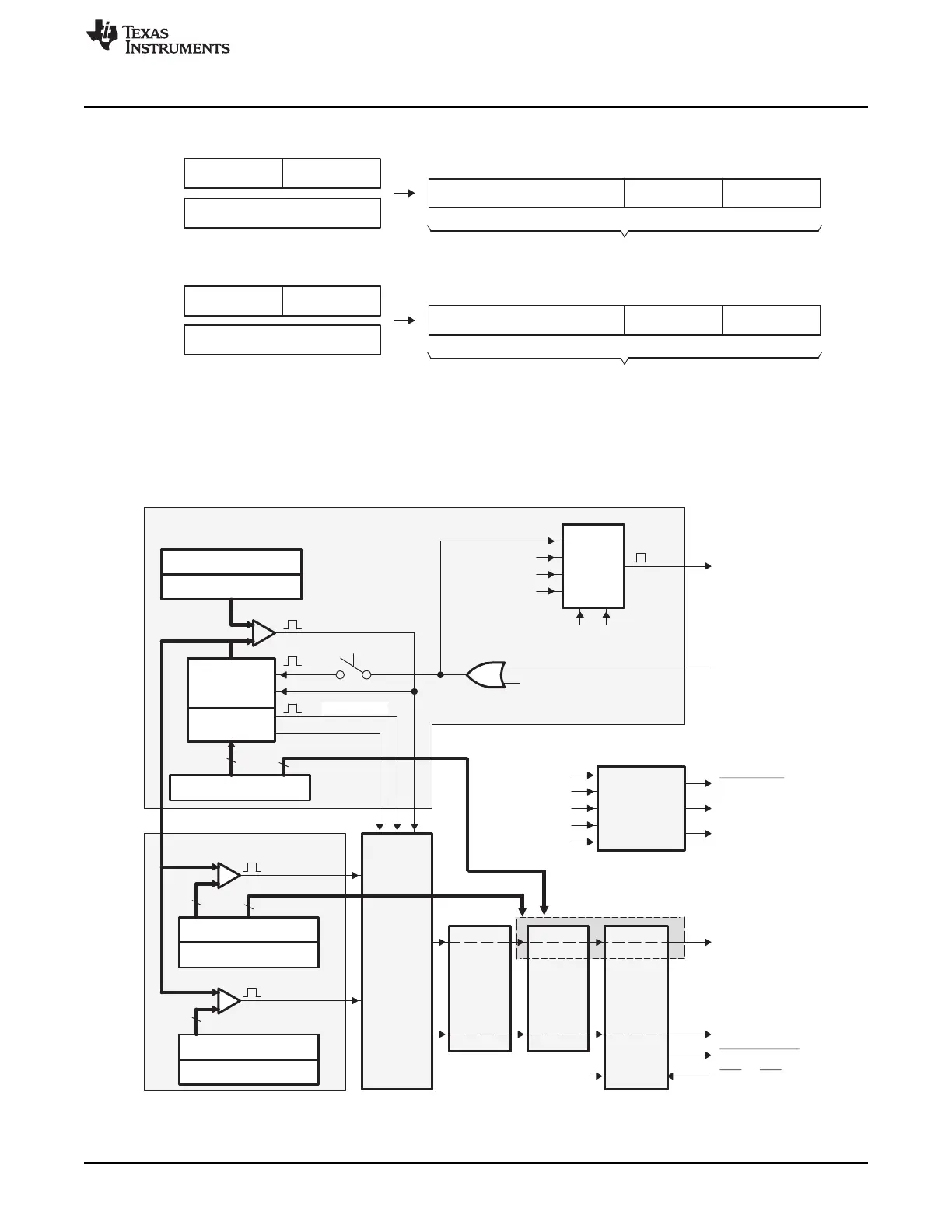

TBPHSHR (8) Reserved (8)

TBPHS (16)

0x0002

0x0003

Reserved (8)

TBPHSHR (8)TBPHS (16)

31 16 15 8 7 0

Single 32 bit write

Reserved (8)

CMPA (16)

CMPAHR (8)0x0008

0x0009

Single 32 bit write

CMPA (16)

31

CMPAHR (8) Reserved (8)

16 15 8 7 0

www.ti.com

Operational Description of HRPWM

329

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

High-Resolution Pulse Width Modulator (HRPWM)

Figure 4-3. HRPWM Extension Registers and Memory Configuration

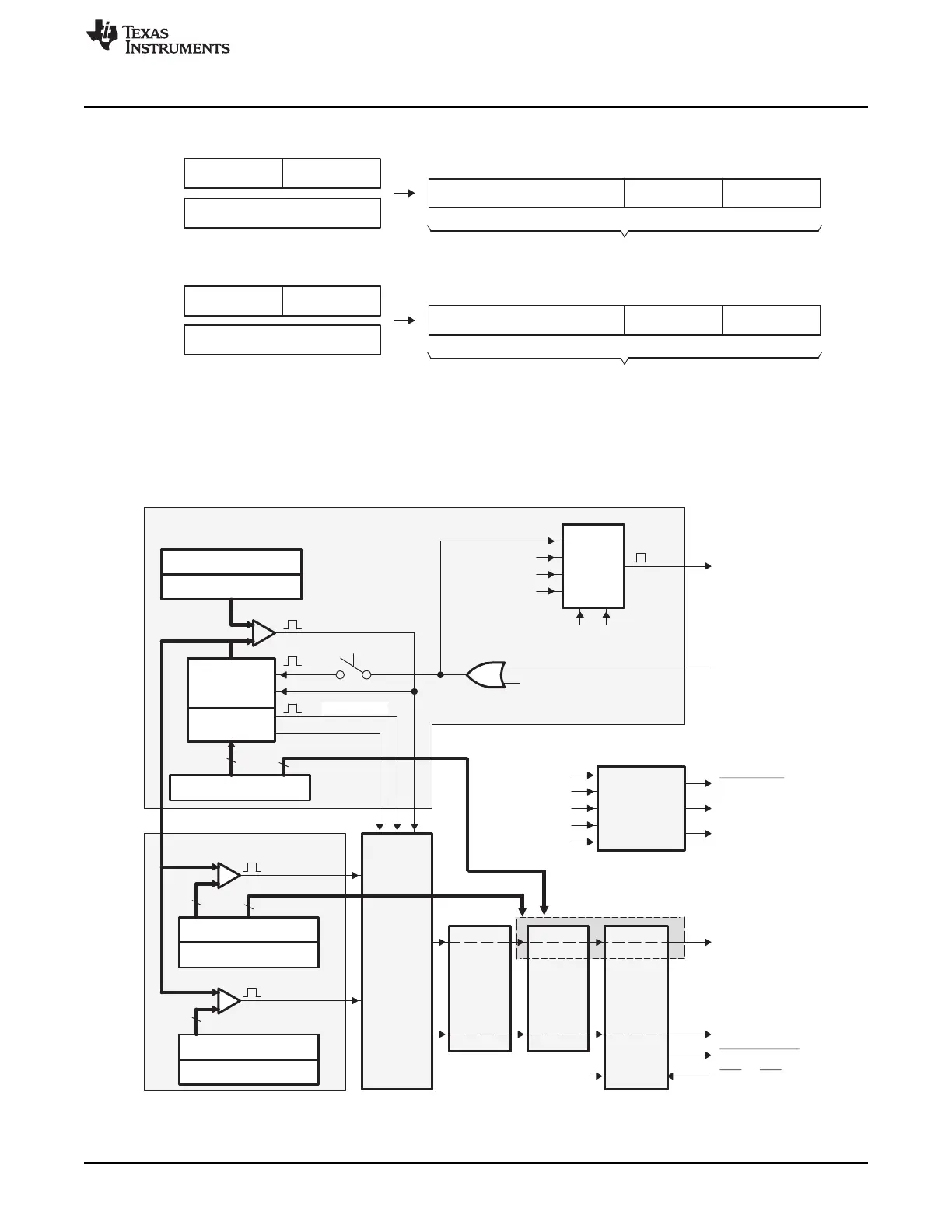

HRPWM capabilities are controlled using the Channel A PWM signal path. Figure 4-4 shows how the

HRPWM interfaces with the 8-bit extension registers.

Figure 4-4. HRPWM System Interface

Loading...

Loading...