General-Purpose Input/Output (GPIO)

www.ti.com

104

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

1.4.6 Register Bit Definitions

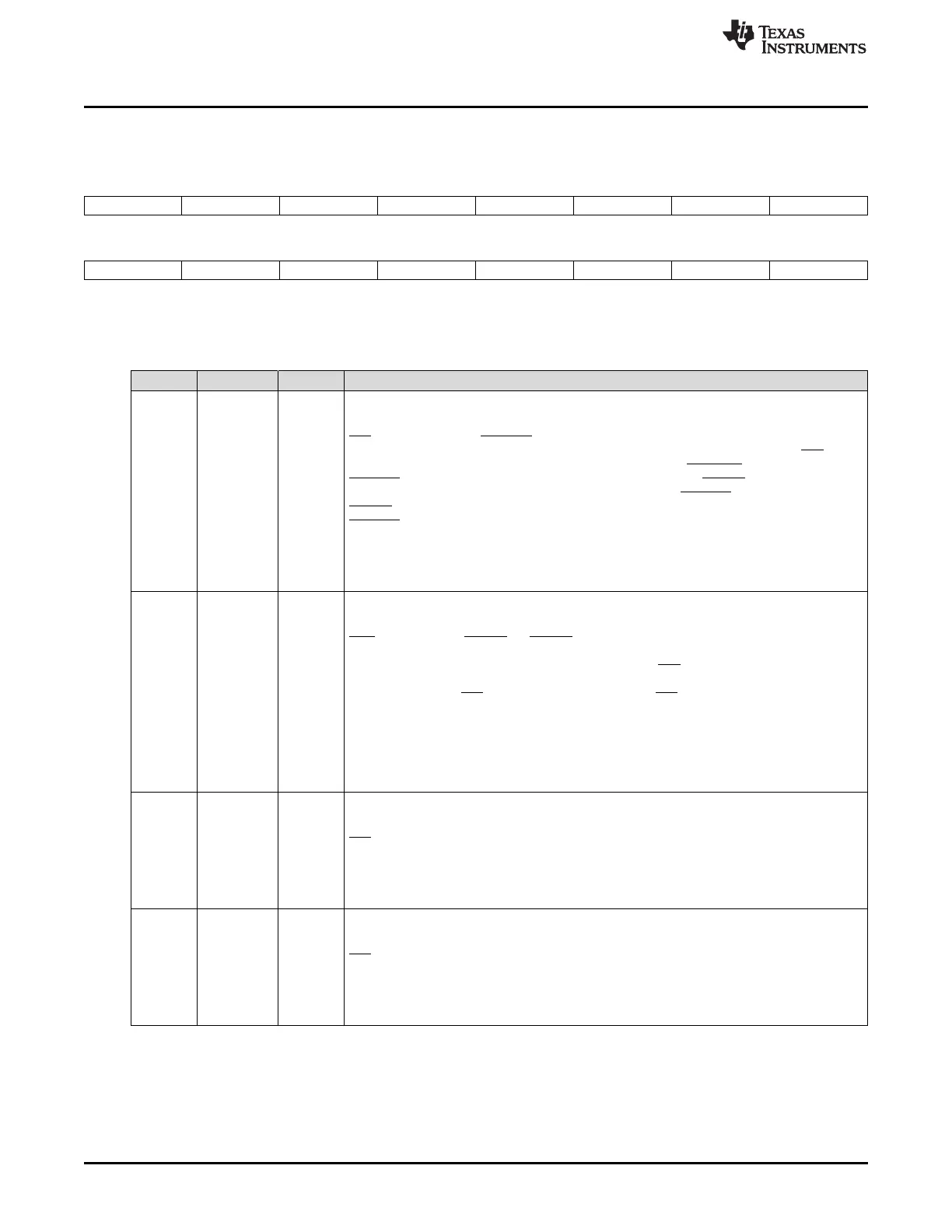

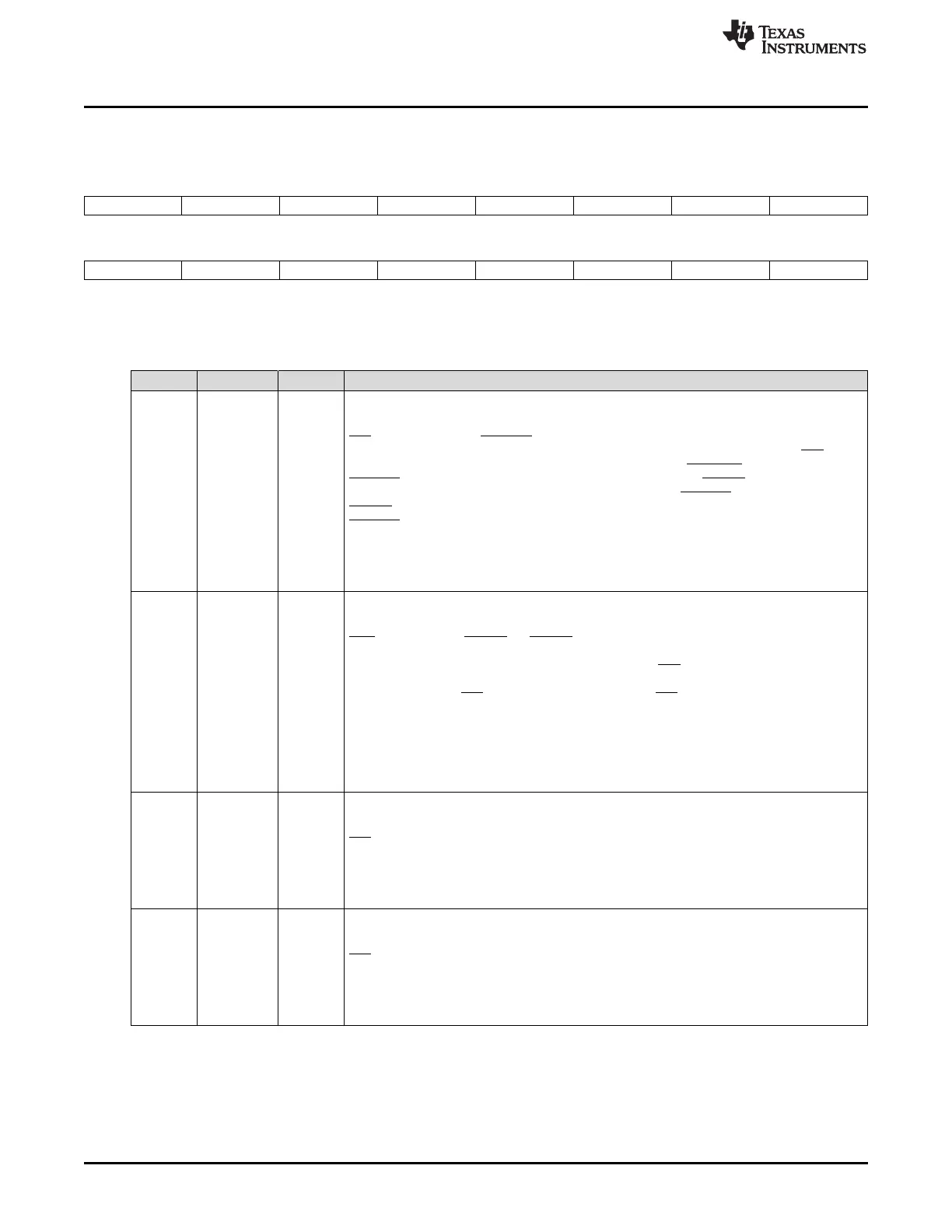

Figure 1-47. GPIO Port A MUX 1 (GPAMUX1) Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO10 GPIO9 GPIO8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND- R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

(2)

If reserved configurations are selected, then the state of the pin will be undefined and the pin may be driven. These selections

are reserved for future expansion and should not be used.

Table 1-50. GPIO Port A Multiplexing 1 (GPAMUX1) Register Field Descriptions

Bits Field Value Description

(1)

31-30 GPIO15 Configure the GPIO15 pin as:

00 GPIO15 - General purpose input/output 15 (default) (I/O)

01 TZ4 - Trip Zone 4 (I) or XHOLDA (O). The pin function for this option is based on the

direction chosen in the GPADIR register. If the pin is configured as an input, then TZ4

function is chosen. If the pin is configured as an output, then XHOLDA function is chosen.

XHOLDA is driven active (low) when the XINTF has granted an XHOLD request. All XINTF

buses and strobe signals will be in a high-impedance state. XHOLDA is released when the

XHOLD signal is released. External devices should only drive the external bus when

XHOLDA is active (low).

10 SCIRXDB - SCI-B receive. (I)

11 MFSXB - McBSP-B transmit frame synch (I/O)

This option is reserved on devices that do not have a McBSP-B port.

(2)

29-28 GPIO14 Configure the GPIO14 pin as:

00 GPIO14 - General purpose I/O 14 (default) (I/O)

01 TZ3 - Trip zone 3 or XHOLD (I). XHOLD, when active (low), requests the external memory

interface (XINTF) to release the external bus and place all buses and strobes into a high-

impedance state. To prevent this from happening when TZ3 signal goes active, disable this

function by writing XINTCNF2[HOLD] = 1. If this is not done, the XINTF bus will go into high

impedance anytime TZ3 goes low. On the ePWM side, TZn signals are ignored by default,

unless they are enabled by the code. The XINTF will release the bus when any current

access is complete and there are no pending accesses on the XINTF. (I)

10 SCITXDB - SCI-B transmit (O)

11 MCLKXB - McBSP-B transmit clock (I/O)

This option is reserved on devices that do not have a McBSP-B port.

(2)

27-26 GPIO13 Configure the GPIO13 pin as:

00 GPIO13 - General purpose I/O 13 (default) (I/O)

01 TZ2 - Trip zone 2 (I)

10 CANRXB - eCAN-B receive. (I)

11 MDRB - McBSP-B Data Receive (I)

This option is reserved on devices that do not have a McBSP-B port.

(2)

25-24 GPIO12 Configure the GPIO12 pin as:

00 GPIO12 - General purpose I/O 12 (default) (I/O)

01 TZ1 - Trip zone 1 (I)

10 CANTXB - eCAN-B transmit. (O)

11 MDXB - McBSP-B, Data transmit (O)

This option is reserved on devices that do not have a McBSP-B port.

(2)

Loading...

Loading...