I2C Registers

www.ti.com

652

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

11.6.2.13 I2CPSC Register (Offset = Ch) [reset = 0h]

I2CPSC is shown in Figure 11-30 and described in Table 11-22.

Return to the Summary Table.

The I2C prescaler register (I2CPSC) is a 16-bit register (see Figure 14-21) used for dividing down the I2C

input clock to obtain the desired module clock for the operation of the I2C module. See the device-specific

data manual for the supported range of values for the module clock frequency.

IPSC must be initialized while the I2C module is in reset (IRS = 0 in I2CMDR). The prescaled frequency

takes effect only when IRS is changed to 1. Changing the IPSC value while IRS = 1 has no effect.

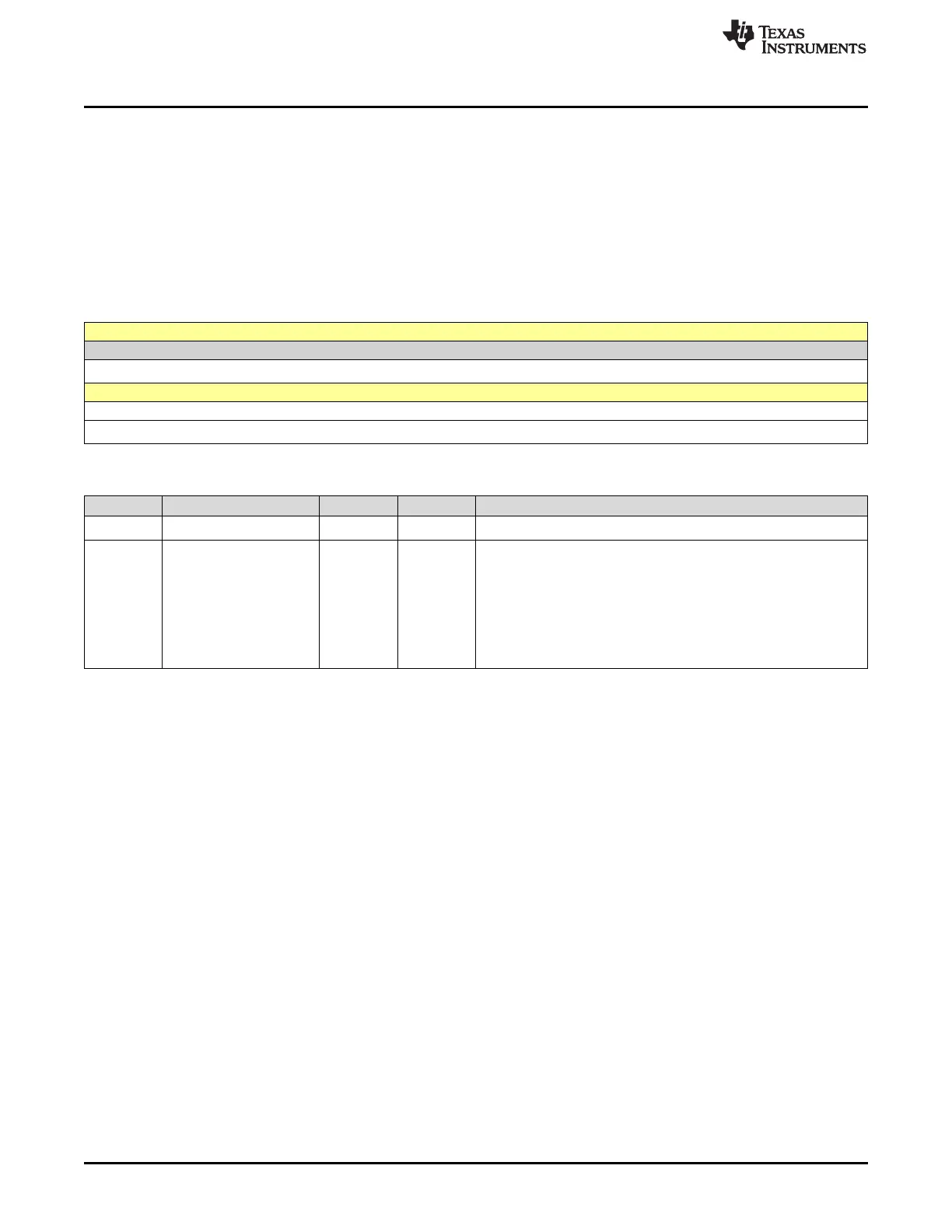

Figure 11-30. I2CPSC Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

IPSC

R/W-0h

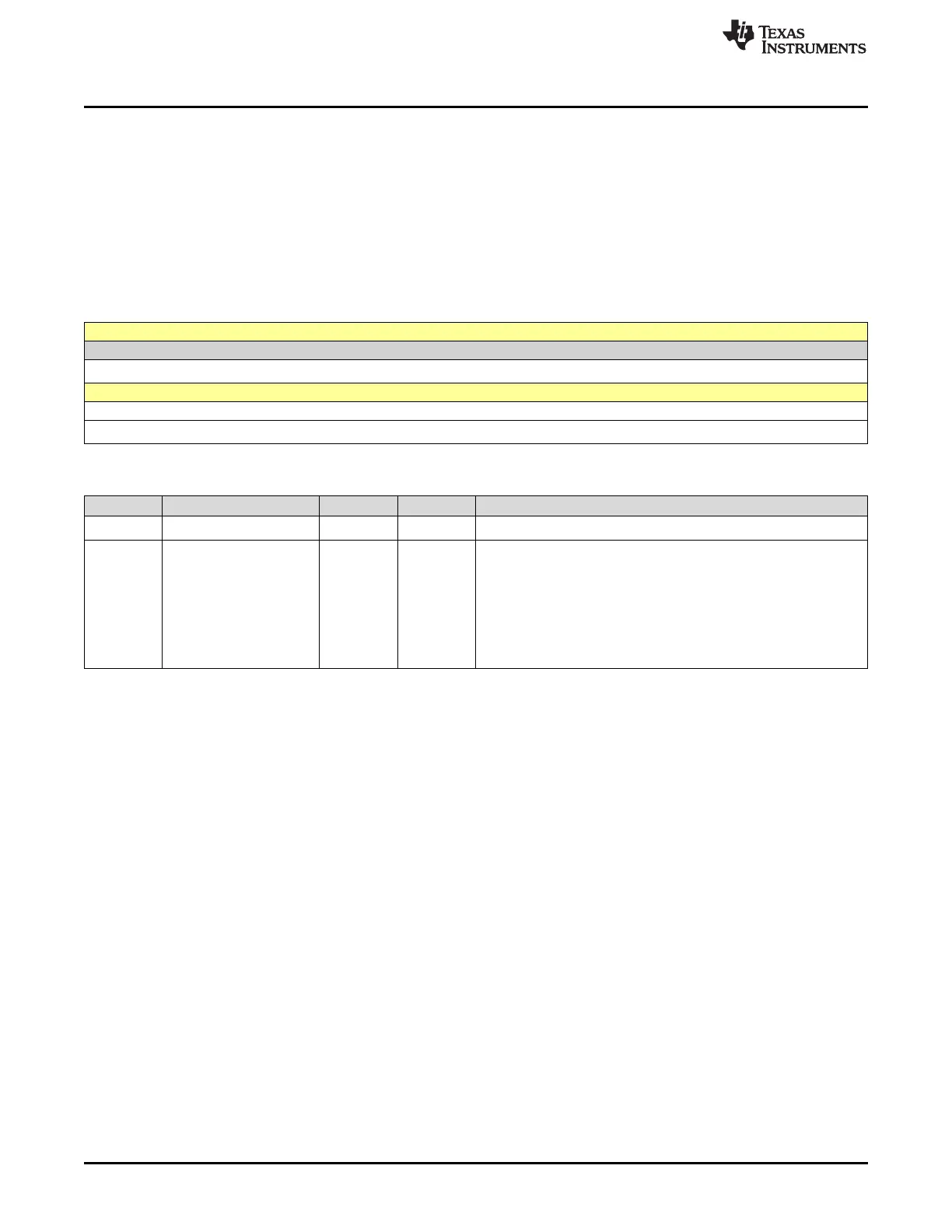

Table 11-22. I2CPSC Register Field Descriptions

Bit Field Type Reset Description

15-8 RESERVED R 0h

Reserved

7-0 IPSC R/W 0h

I2C prescaler divide-down value.

IPSC determines how much the CPU clock is divided to create the

module clock of the I2C module:

module clock frequency = I2C input clock frequency/(IPSC + 1)

Note: IPSC must be initialized while the I2C module is in reset (IRS

= 0 in I2CMDR).

Reset type: SYSRSn

Loading...

Loading...