www.ti.com

Register Descriptions

515

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

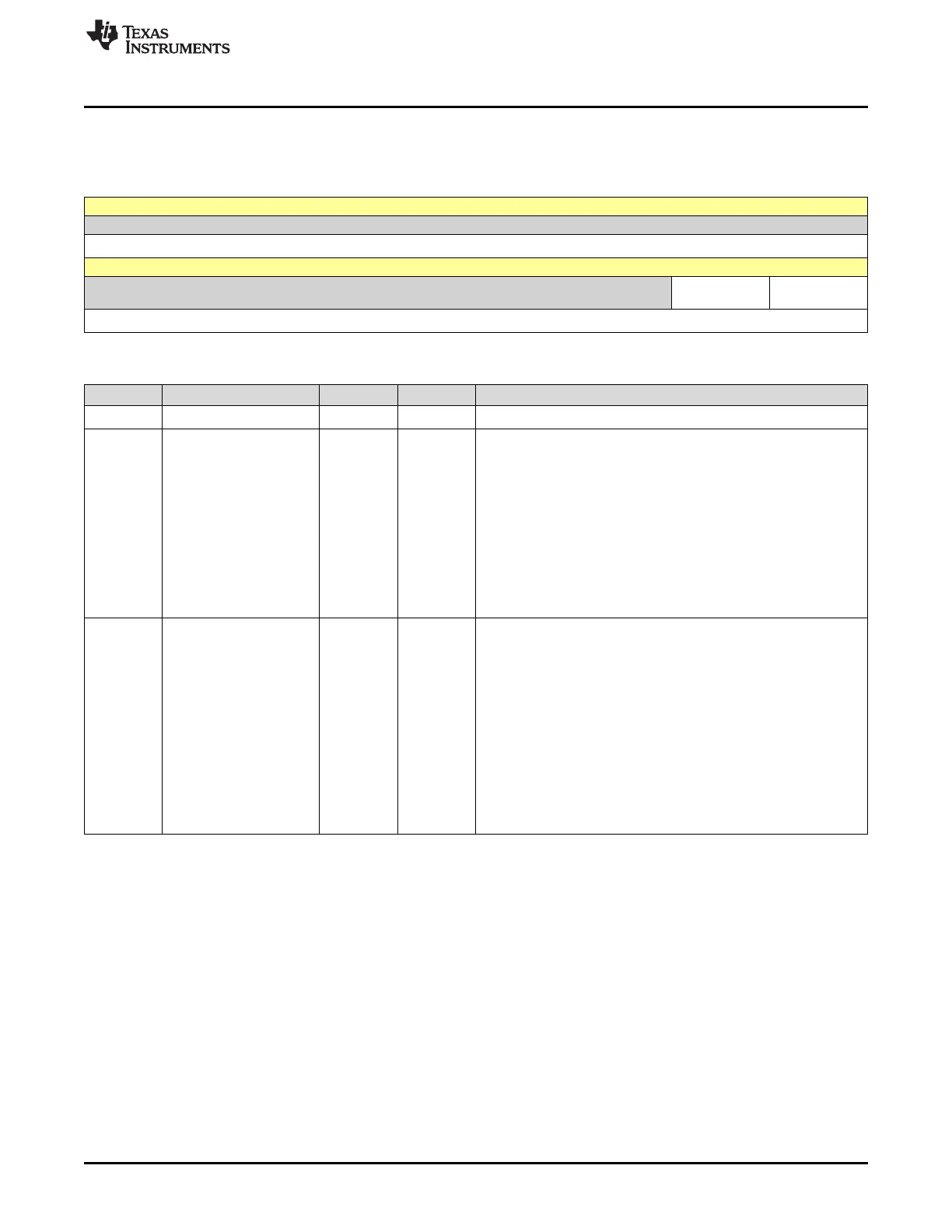

8.9.1 DMACTRL Register (Offset = 1000h) [reset = 0h]

DMACTRL is shown in Figure 8-8 and described in Table 8-3.

Figure 8-8. DMACTRL Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED PRIORITYRES

ET

HARDRESET

R-0h RS-0h RS-0h

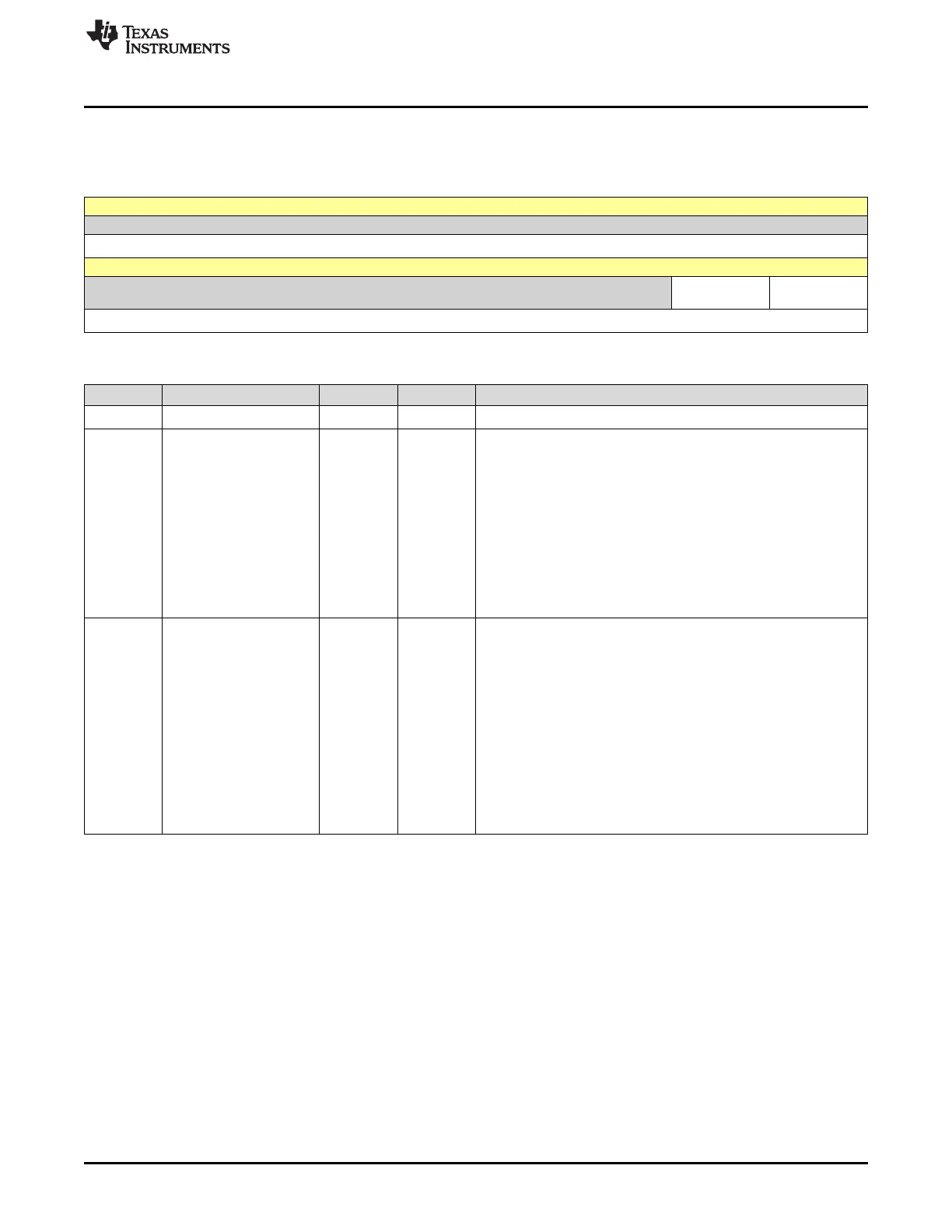

Table 8-3. DMACTRL Register Field Descriptions

Bit Field Type Reset Description

15-2 RESERVED R 0h

Reserved

1 PRIORITYRESET RS 0h The priority reset bit resets the round-robin state machine when a 1

is written.

Service starts from the first enabled channel.

Writes of 0 are ignored and this bit always reads back a 0.

When a 1 is written to this bit, any pending burst transfer completes

before resetting the channel priority machine.

If CH1 is configured as a high priority channel, and this bit is written

to while CH1 is servicing a burst, the CH1 burst is completed and

then any lower priority channel burst is also completed (if CH1

interrupted in the middle of a burst), before the state machine is

reset.

In case CH1 is high priority, the state machine restarts from CH2 (or

the next highest enabled channel).

0 HARDRESET RS 0h Writing a 1 to the hard reset bit resets the whole DMA and aborts

any current access (similar to applying a device reset).

Writes of 0 are ignored and this bit always reads back a 0.

For a soft reset, a bit is provided for each channel to perform a

gentler reset.

Refer to the channel control registers.

If the DMA was performing an access to the XINTF and the DMA

access was stalled (XREADY not responding), then a HARDRESET

would abort the access.

The XINTF access would only complete if XREADY is released.

When writing to this bit, there is a one cycle delay before it takes

effect.

Hence at least a one cycle delay (i.e., a NOP instruction) after

writing to this bit should be introduced before attempting an access

to any other DMA register.

Loading...

Loading...