www.ti.com

SPI Registers

573

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

9.5.2.7 SPITXBUF Register (Offset = 8h) [reset = 0h]

SPITXBUF is shown in Figure 9-14 and described in Table 9-13.

Return to the Summary Table.

SPITXBUF stores the next character to be tranmitted. Writing to this register sets the TX BUF FULL Flag

bit in SPISTS. When the transmission of the current character is complete, the contents of this register are

automatically loaded in SPIDAT and the TX BUF FULL Flag is cleared. If no tranmission is currently

active, data written to this register falls through into the SPIDAT register and the TX BUF FULL Flag is not

set.

In master mode, if no tranmission is currently active, writing to this register initiates a transmission in the

same manner that writing to SPIDAT does.

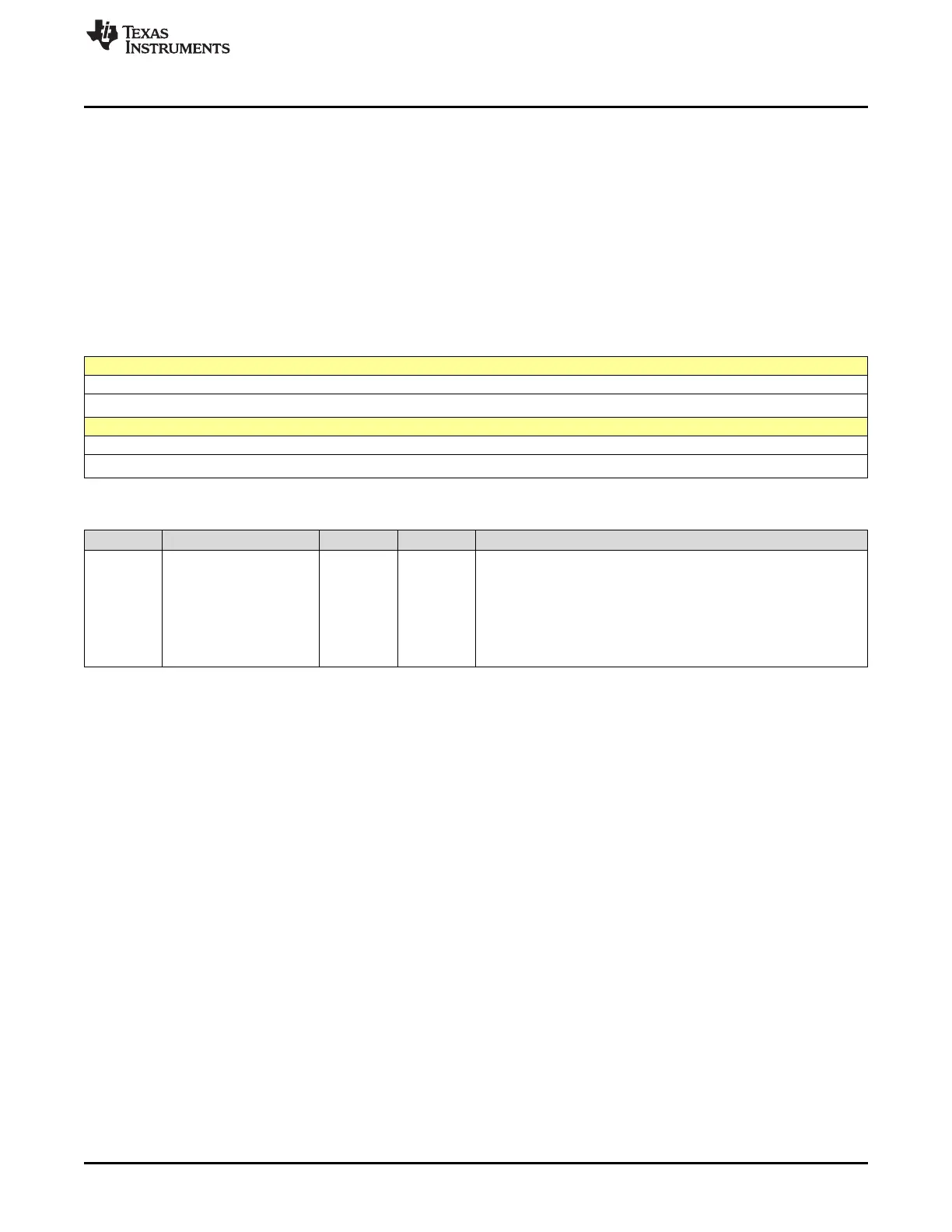

Figure 9-14. SPITXBUF Register

15 14 13 12 11 10 9 8

TXBn

R/W-0h

7 6 5 4 3 2 1 0

TXBn

R/W-0h

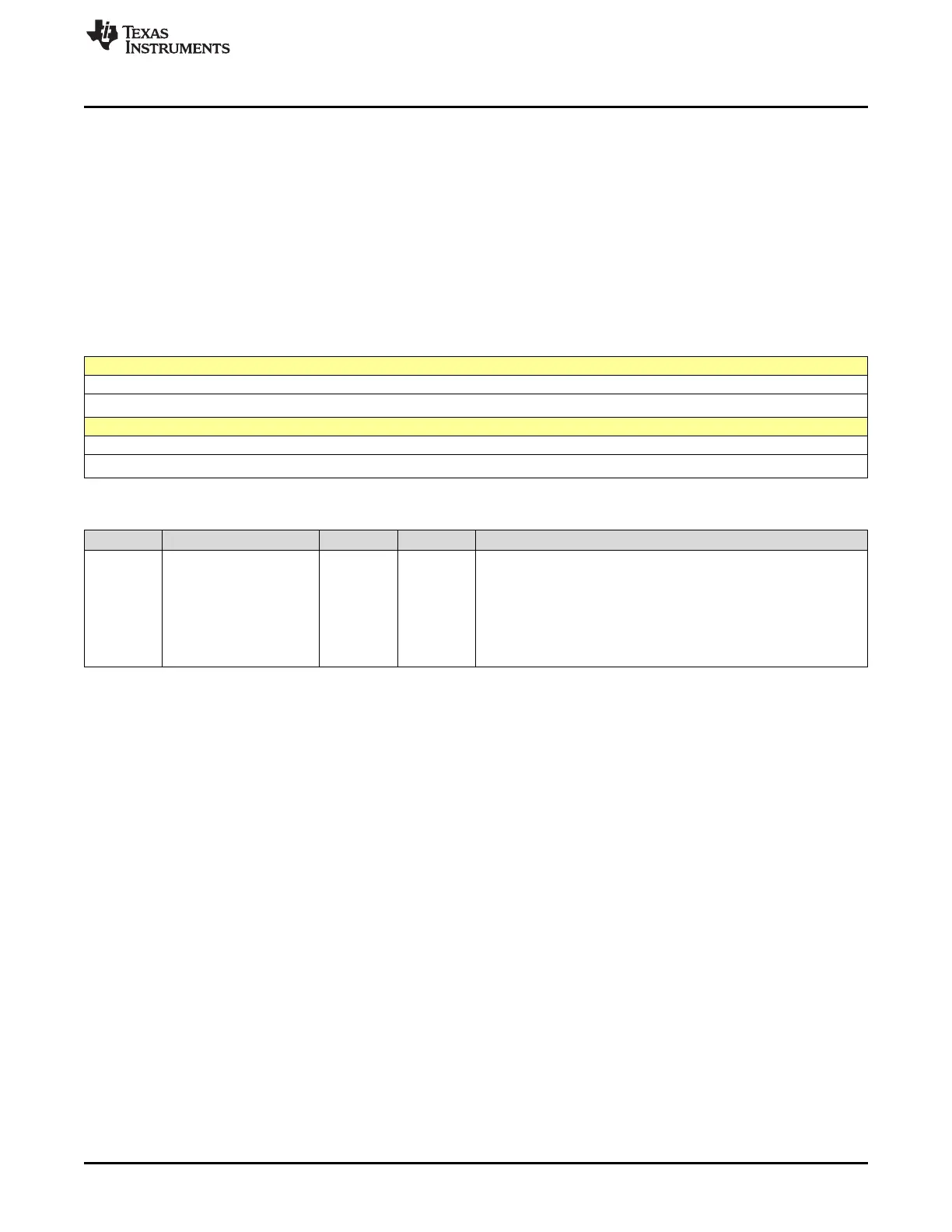

Table 9-13. SPITXBUF Register Field Descriptions

Bit Field Type Reset Description

15-0 TXBn R/W 0h

Transmit Data Buffer

This is where the next character to be transmitted is stored. When

the transmission of the current character has completed, if the TX

BUF FULL Flag bit is set, the contents of this register is

automatically transferred to SPIDAT, and the TX BUF FULL Flag is

cleared. Writes to SPITXBUF must be left-justified.

Reset type: SYSRSn

Loading...

Loading...