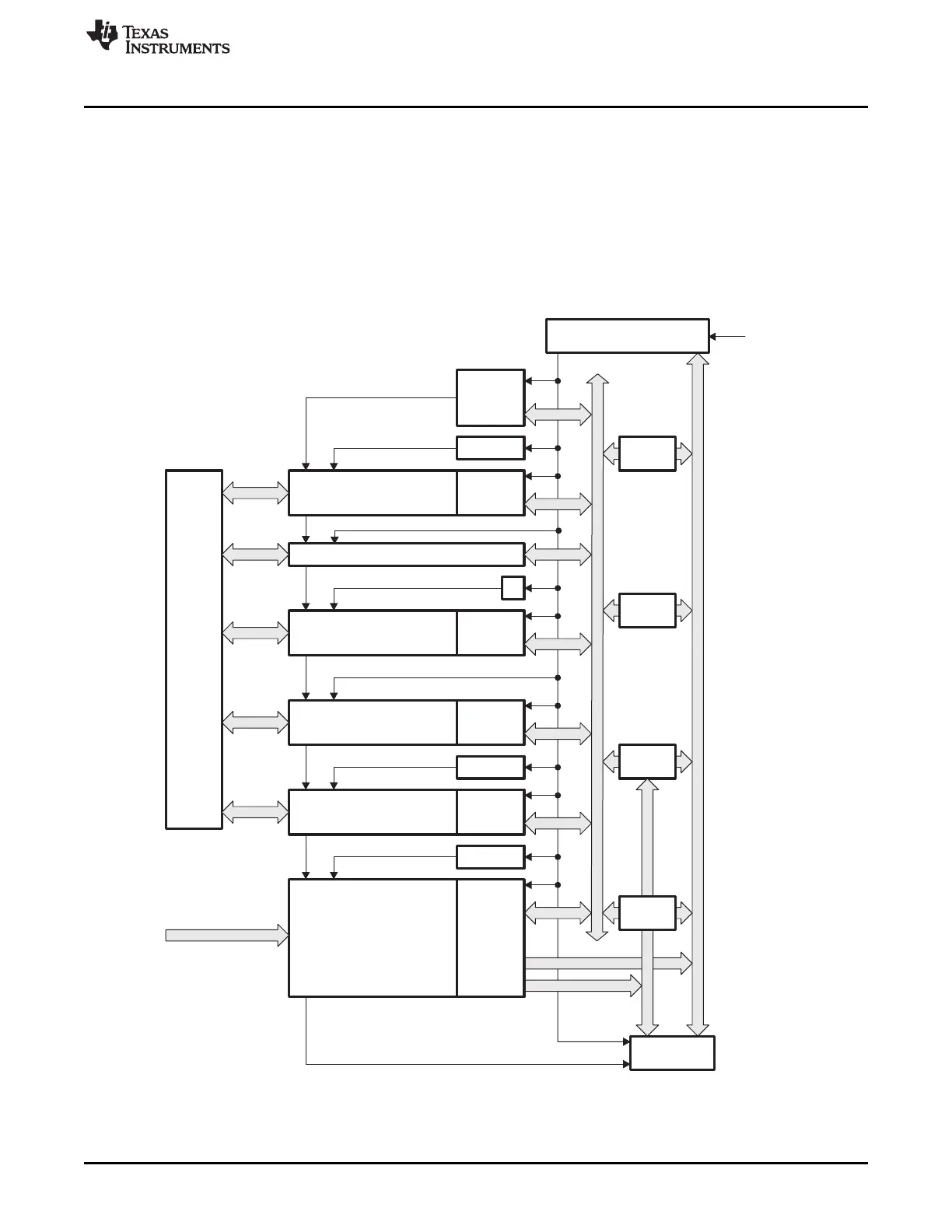

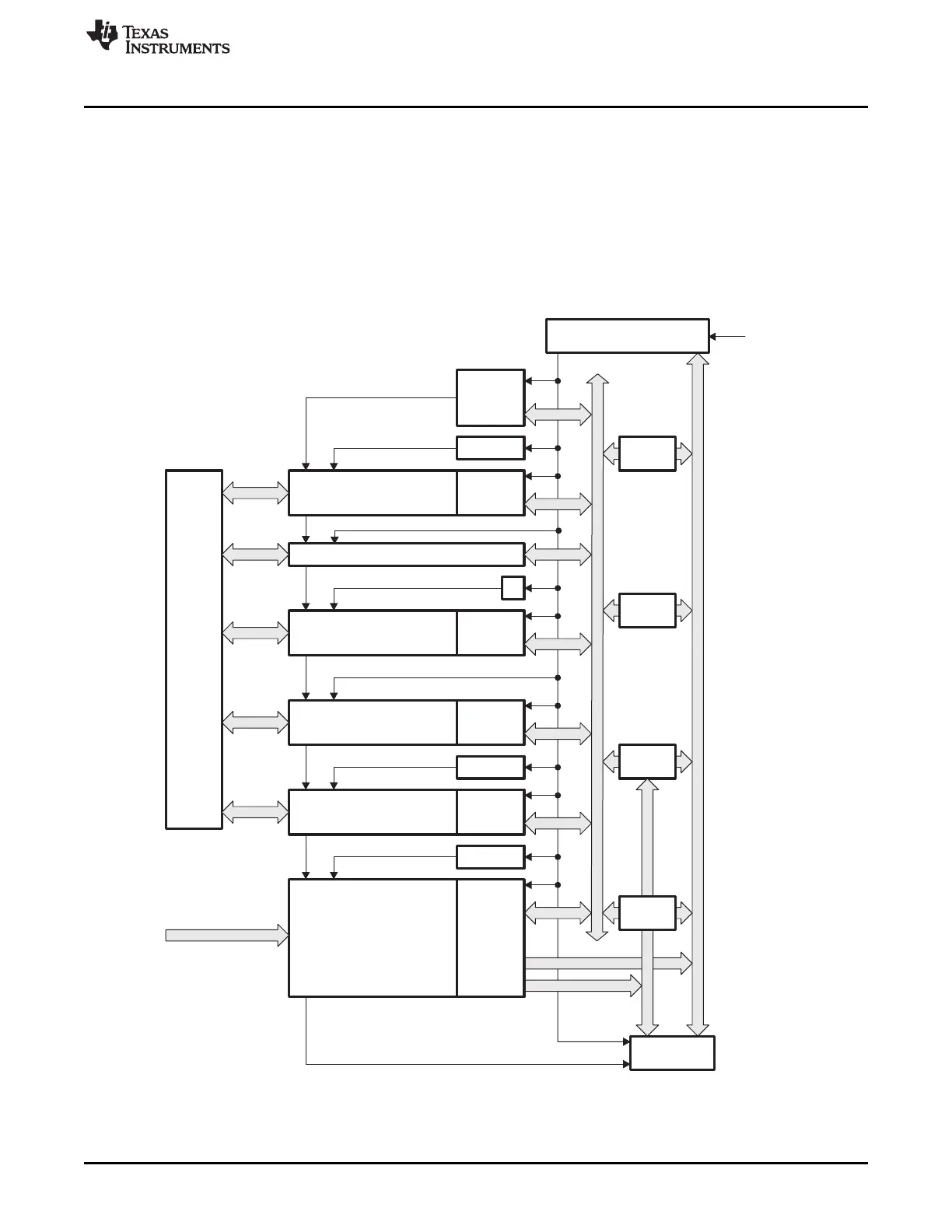

ePWM1/../6,HRPWM1/../6,

eCAP1/../6,eQEP1/2

Peripheral

Registers

Bridge

ClockEnables

I/O

Peripheral

Registers

ClockEnables

I/O

eCAN-A/B

/2

Peripheral

Registers

ClockEnables

I/O

SPI-A,SCI-A/B/C

LOSPCP

LSPCLK

System

Control

Register

Bridge

SYSCLKOUT

MemoryBus

C28xCore

GPIO

Mux

ClockEnables

Peripheral

Registers

I/O

McBSP-A/B

LOSPCP

LSPCLK

ClockEnables

Bridge

HISPCP

HSPCLK

DMA

Bus

Result

Registers

Bridge

12-Bit ADC

ADC

Registers

16Channels

DMA

ClockEnables

PeripheralBus

CLKIN

I2C-A

ClockEnables

www.ti.com

Clocking and System Control

59

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

1.3 Clocking and System Control

This section describes the oscillator, PLL and clocking mechanisms, the watchdog function, and the low-

power modes.

1.3.1 Clocking

Figure 1-13 shows the various clock and reset domains.

The PLL, clocking, watchdog and low-power modes, are controlled by the registers listed in Table 1-14 .

Figure 1-13. Clock and Reset Domains

A CLKIN is the clock into the CPU. It is passed out of the CPU as SYSCLKOUT (that is, CLKIN is the same frequency

as SYSCLKOUT).

Loading...

Loading...