www.ti.com

SCI Registers

615

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

10.14.2.13 SCIPRI Register (Offset = Fh) [reset = 0h]

SCIPRI is shown in Figure 10-23 and described in Table 10-19.

Return to the Summary Table.

SCIPRI determines what happens when an emulation suspend event occurs.

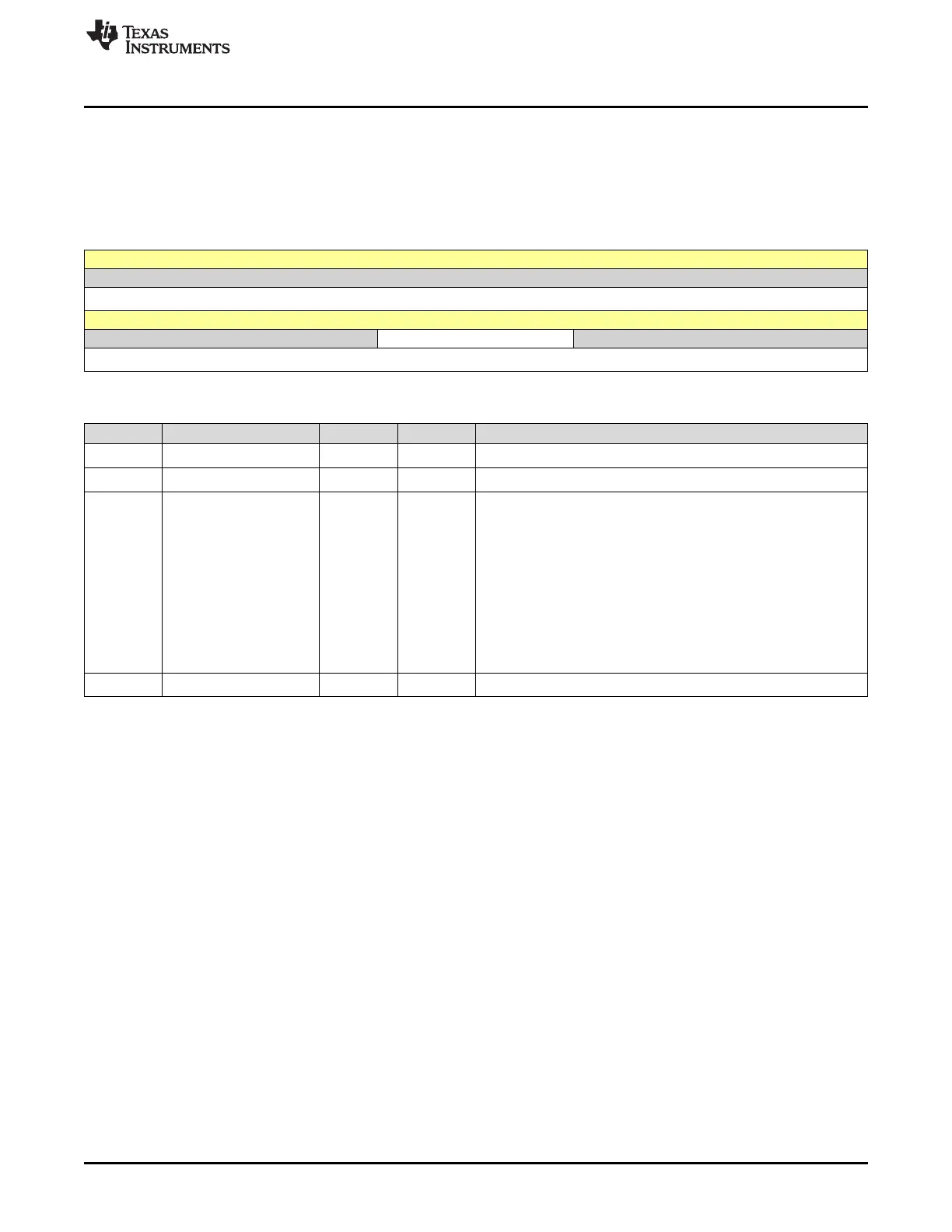

Figure 10-23. SCIPRI Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED FREESOFT RESERVED

R-0h R/W-0h R-0h

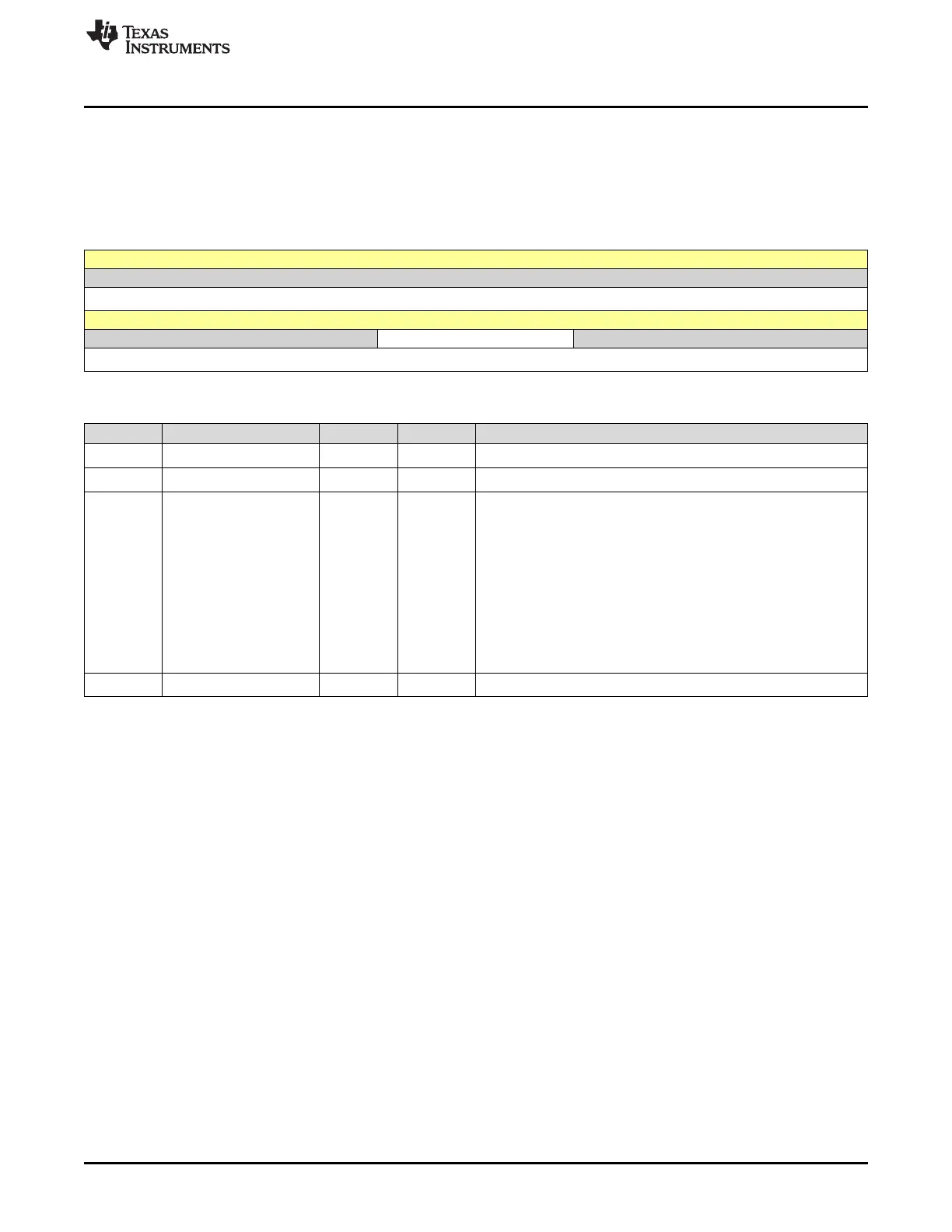

Table 10-19. SCIPRI Register Field Descriptions

Bit Field Type Reset Description

15-8 RESERVED R 0h

Reserved

7-5 RESERVED R 0h

Reserved

4-3 FREESOFT R/W 0h

These bits determine what occurs when an emulation suspend event

occurs (for example, when the debugger hits a breakpoint). The

peripheral can continue whatever it is doing (free-run mode), or if in

stop mode, it can either stop immediately or stop when the current

operation (the current receive/transmit sequence) is complete.

Reset type: SYSRSn

0h (R/W) = Immediate stop on suspend

1h (R/W) = Complete current receive/transmit sequence before

stopping

2h (R/W) = Free run

3h (R/W) = Free run

2-0 RESERVED R 0h

Reserved

Loading...

Loading...