Register Descriptions

www.ti.com

516

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

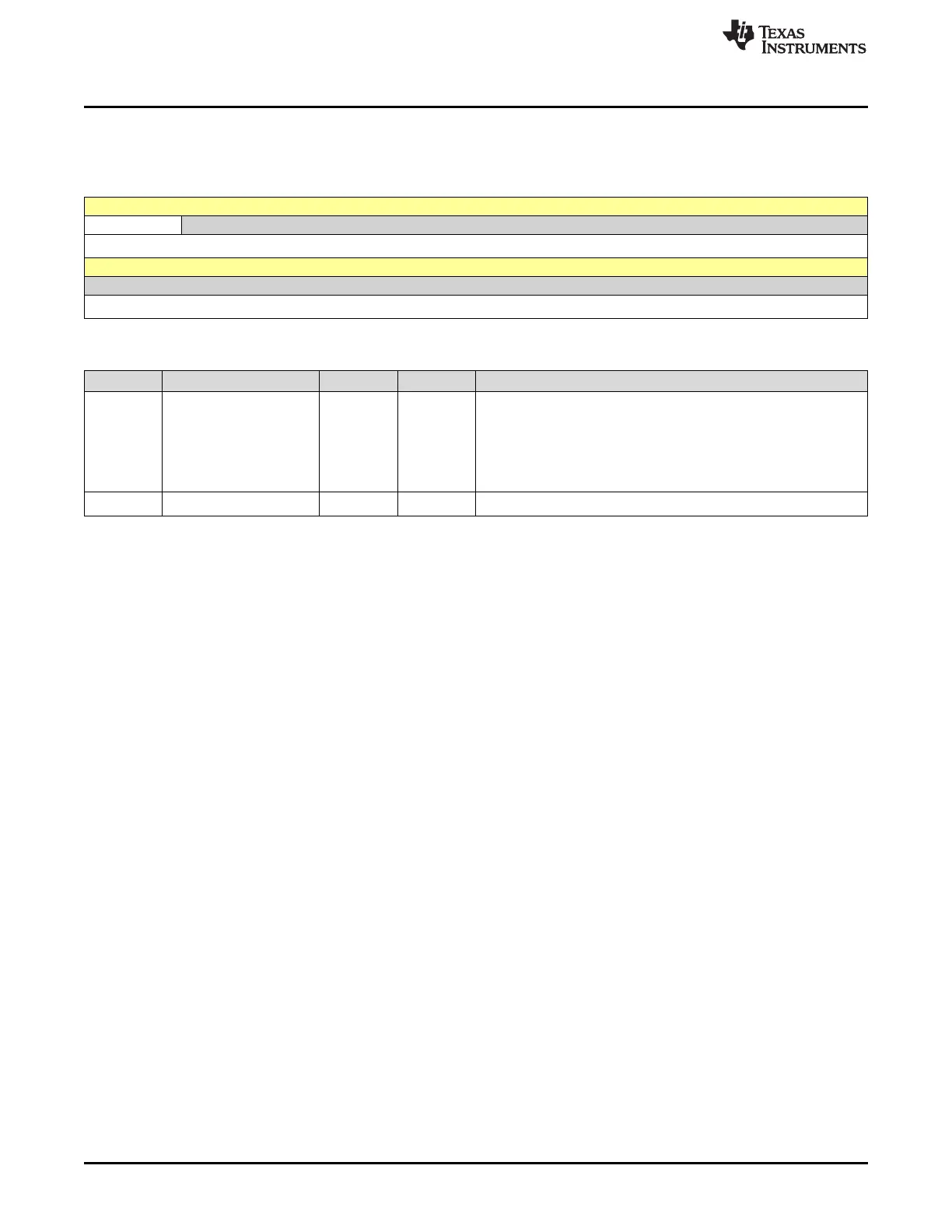

8.9.2 DEBUGCTRL Register (Offset = 1001h) [reset = 0h]

DEBUGCTRL is shown in Figure 8-9 and described in Table 8-4.

Figure 8-9. DEBUGCTRL Register

15 14 13 12 11 10 9 8

FREE RESERVED

R/W-0h R-0h

7 6 5 4 3 2 1 0

RESERVED

R-0h

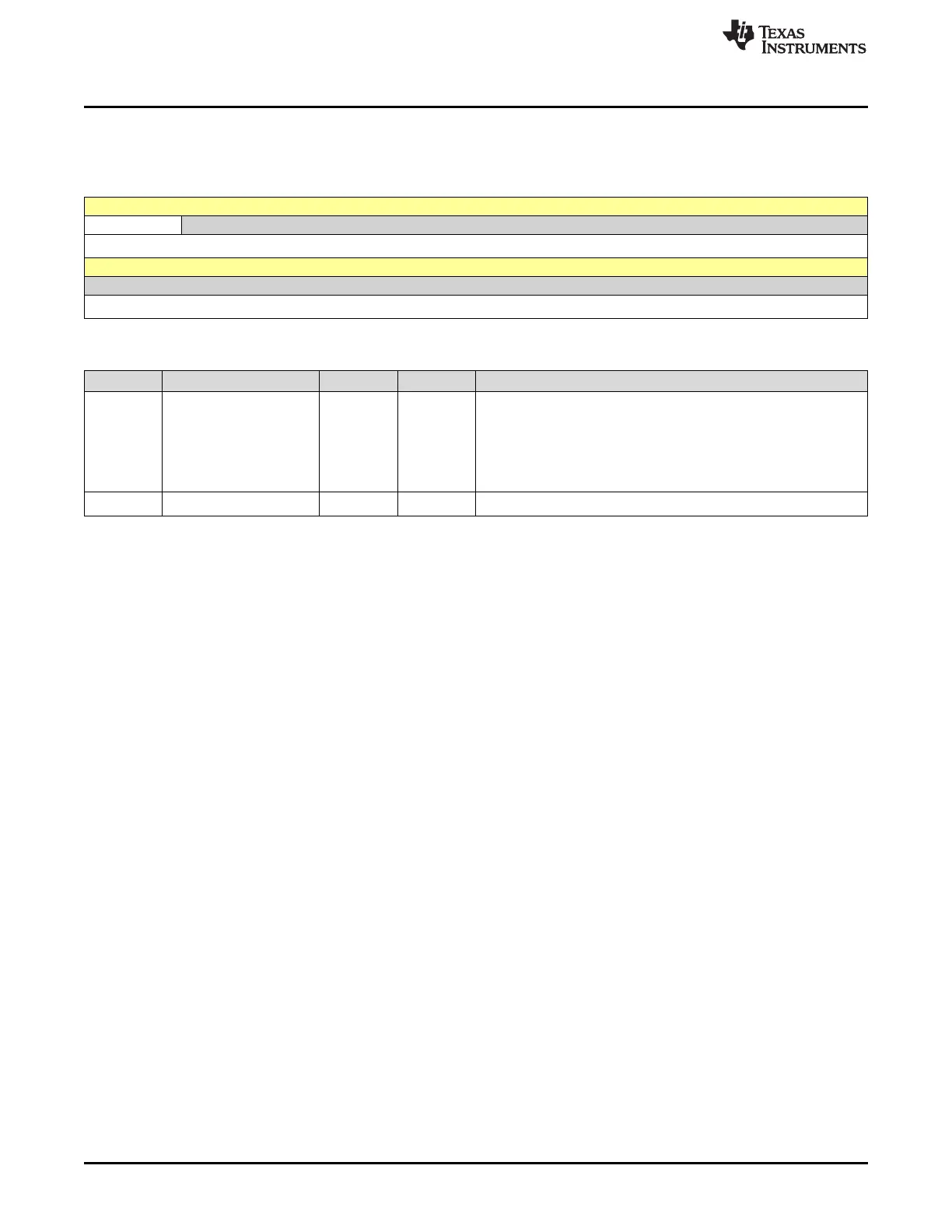

Table 8-4. DEBUGCTRL Register Field Descriptions

Bit Field Type Reset Description

15 FREE R/W 0h

Emulation Control Bit: This bit specifies the action when an

emulation halt event occurs.

0h = DMA runs until the current DMA read-write access is completed

and the current status of a DMA is frozen. See the HALT points in

Figure 8-5 for possible halt states.

1h = DMA is unaffected by emulation suspend (run free)

14-0 RESERVED R 0h

Reserved

Loading...

Loading...