Peripheral Interrupt Expansion (PIE)

www.ti.com

154

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

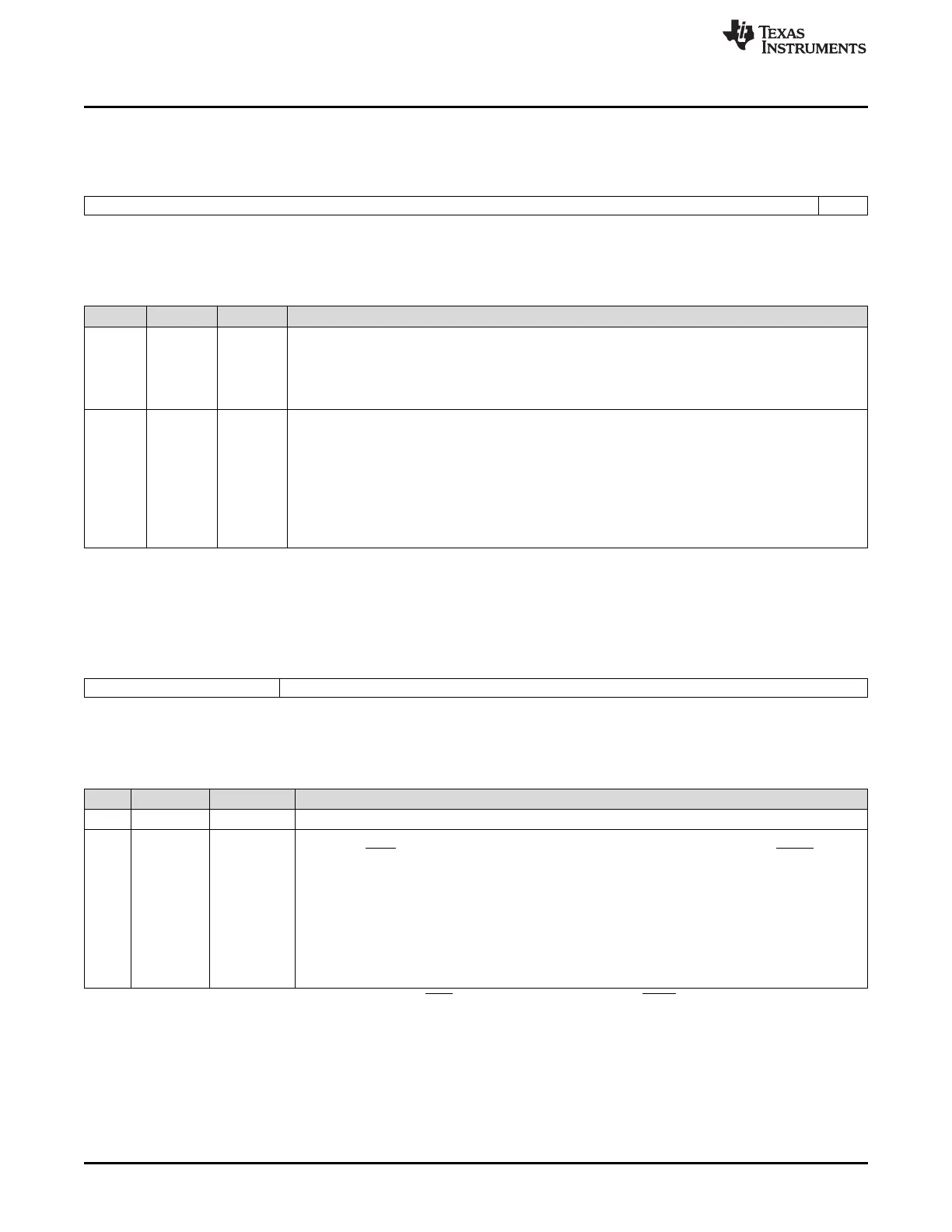

1.6.4.1 PIE Control Register (PIECTRL)

Figure 1-84. PIE Control Register (PIECTRL) (Address CE0)

15 1 0

PIEVECT ENPIE

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 1-114. PIE Control Register (PIECTRL) Field Descriptions

Bits Field Value Description

15-1 PIEVECT These bits indicate the address within the PIE vector table from which the vector was fetched. The

least significant bit of the address is ignored and only bits 1 to 15 of the address is shown. You can

read the vector value to determine which interrupt generated the vector fetch.

For Example: If PIECTRL = 0x0D27 then the vector from address 0x0D26 (illegal operation) was

fetched.

0 ENPIE Enable vector fetching from PIE vector table.

Note: The reset vector is never fetched from the PIE, even when it is enabled. This vector is always

fetched from boot ROM.

0 If this bit is set to 0, the PIE block is disabled and vectors are fetched from the CPU vector table in

boot ROM. All PIE block registers (PIEACK, PIEIFR, PIEIER) can be accessed even when the PIE

block is disabled.

1 When ENPIE is set to 1, all vectors, except for reset, are fetched from the PIE vector table. The reset

vector is always fetched from the boot ROM.

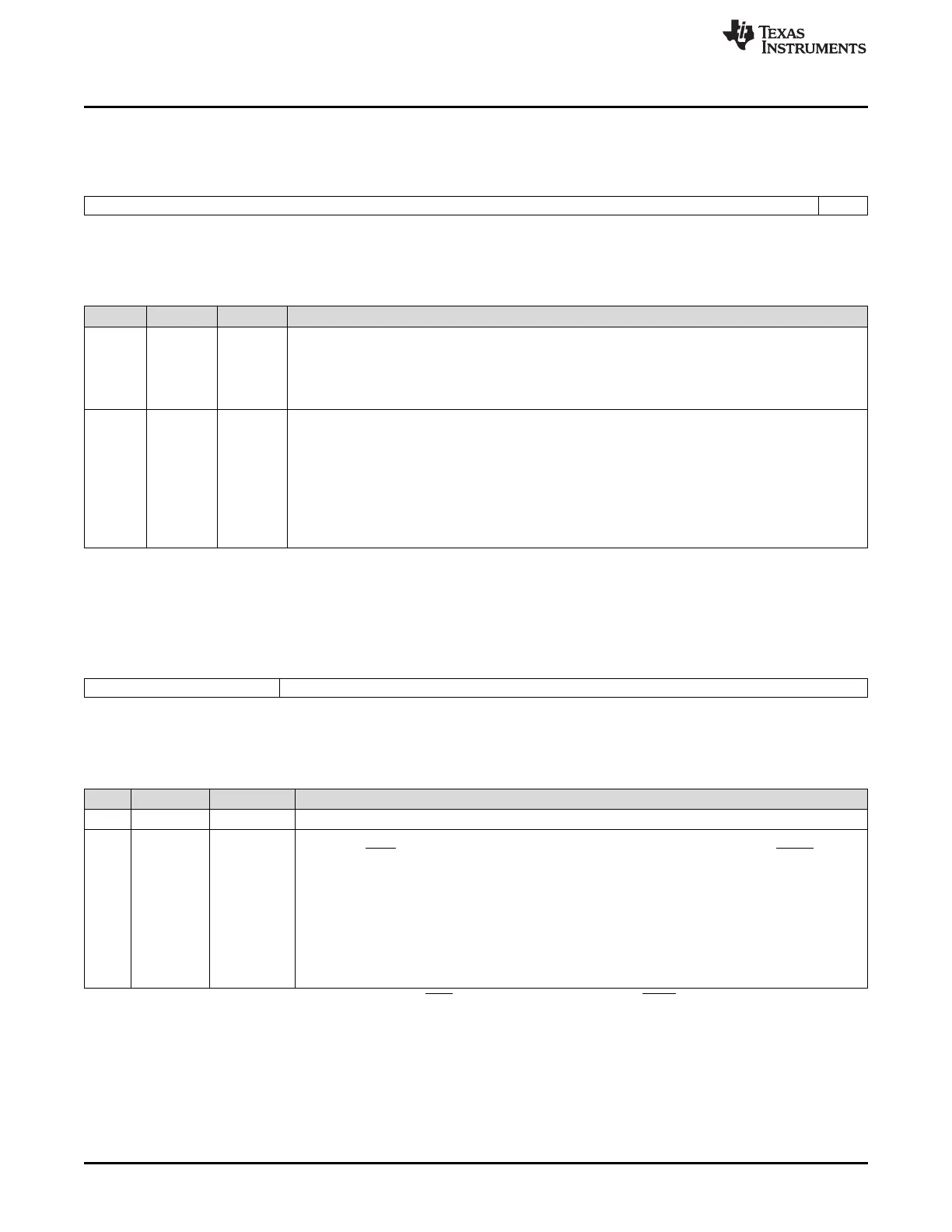

1.6.4.2 PIE Interrupt Acknowledge Register (PIEACK)

Figure 1-85. PIE Interrupt Acknowledge Register (PIEACK) (Address CE1)

15 12 11 0

Reserved PIEACK

R-0 R/W1C-0

LEGEND: R/W1C = Read/Write 1 to clear; R = Read only; -n = value after reset

(1)

bit x = PIEACK bit 0 - PIEACK bit 11. Bit 0 refers to CPU INT1 up to Bit 11, which refers to CPU INT12

Table 1-115. PIE Interrupt Acknowledge Register (PIEACK) Field Descriptions

Bits Field Value Description

15-12 Reserved Reserved

11-0 PIEACK Each bit in PIEACK refers to a specific PIE group. Bit 0 refers to interrupts in PIE group 1 that are

MUXed into INT1 up to Bit 11, which refers to PIE group 12 which is MUXed into CPU INT12

bit x = 0

(1)

If a bit reads as a 0, it indicates that the PIE can send an interrupt from the respective group to the

CPU.

Writes of 0 are ignored.

bit x = 1 Reading a 1 indicates if an interrupt from the respective group has been sent to the CPU and all

other interrupts from the group are currently blocked.

Writing a 1 to the respective interrupt bit clears the bit and enables the PIE block to drive a pulse into

the CPU interrupt input if an interrupt is pending for that group.

Loading...

Loading...