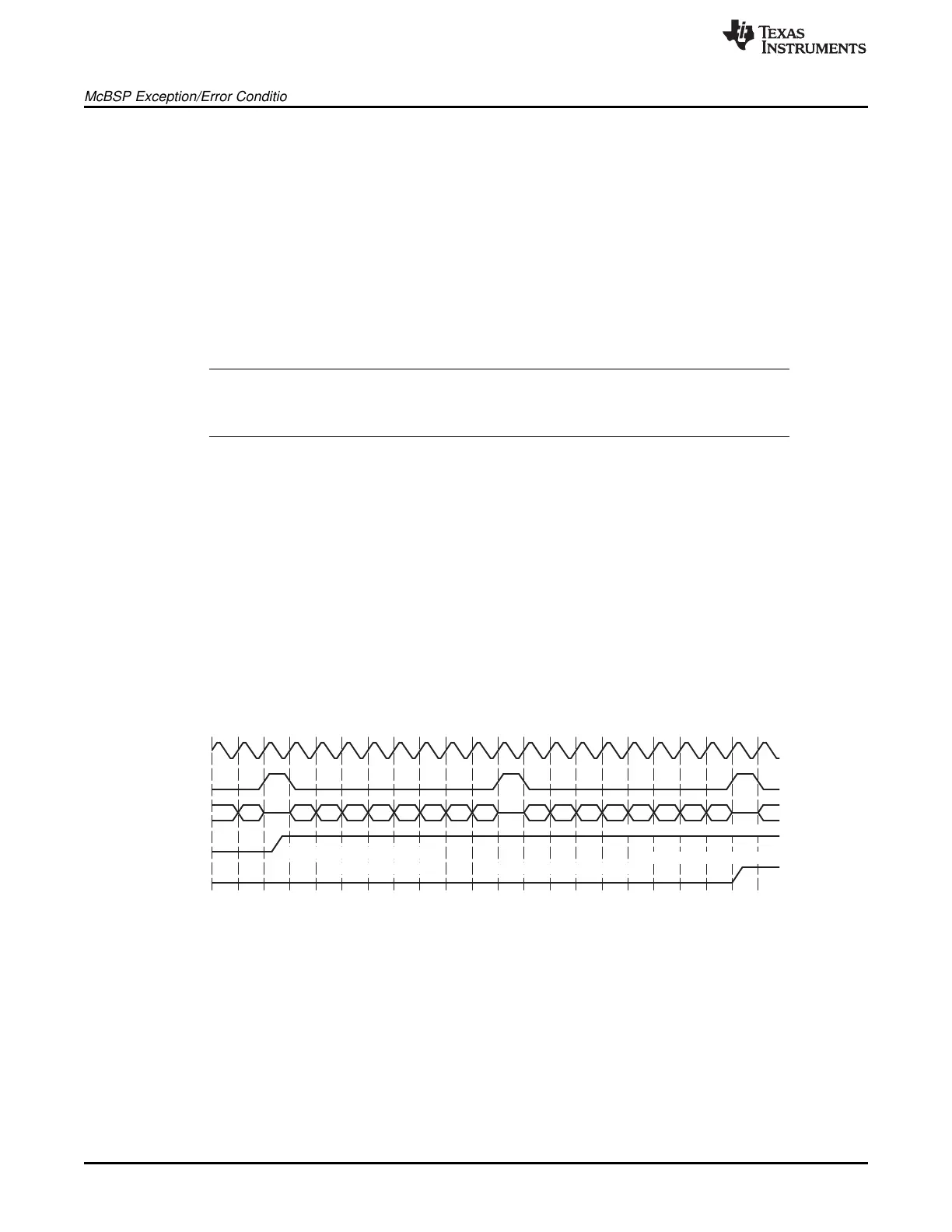

No RSR1 to RBR1 copy(C)

No read from DRR1(A)

No RBR1 to DRR1 copy(B)No read from DRR1(A)

RBR1 to DRR1 copy(A)

D7C0C1C2C3C4C5C6C7B0B1B2B3B4B5B6B7A0A1

RFULL

RRDY

DR

FSR

CLKR

McBSP Exception/Error Conditions

www.ti.com

678

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

1. DRR1 has not been read since the last RBR-to-DRR copy (RRDY = 1).

2. RBR1 is full and an RBR-to-DRR copy has not occurred.

3. RSR1 is full and an RSR1-to-RBR copy has not occurred.

As described in Section 12.3.5, data arriving on DR is continuously shifted into RSR1 (for word length of

16 bits or smaller) or RSR2 and RSR1 (for word length larger than 16 bits). Once a complete word is

shifted into the RSR(s), an RSR-to-RBR copy can occur only if the previous data in RBR1 has been

copied to DRR1. The RRDY bit is set when new data arrives in DRR1 and is cleared when that data is

read from DRR1. Until RRDY = 0, the next RBR-to-DRR copy does not take place, and the data is held in

the RSR(s). New data arriving on the DR pin is shifted into RSR(s), and the previous content of the

RSR(s) is lost.

You can prevent the loss of data if DRR1 is read no later than 2.5 cycles before the end of the third word

is shifted into the RSR1.

NOTE: If both DRRs are needed (word length larger than 16 bits), the CPU or the DMA controller

must read from DRR2 first and then from DRR1. As soon as DRR1 is read, the next RBR-to-

DRR copy is initiated. If DRR2 is not read first, the data in DRR2 is lost.

After the receiver starts running from reset, a minimum of three words must be received before RFULL is

set. Either of the following events clears the RFULL bit and allows subsequent transfers to be read

properly:

• The CPU or DMA controller reads DRR1.

• The receiver is reset individually (RRST = 0) or as part of a device reset.

Another frame-synchronization pulse is required to restart the receiver.

12.5.2.1 Example of Overrun Condition

Figure 12-21 shows the receive overrun condition. Because serial word A is not read from DRR1 before

serial word B arrives in RBR1, B is not transferred to DRR1 yet. Another new word ©) arrives and RSR1 is

full with this data. DRR1 is finally read, but not earlier than 2.5 cycles before the end of word C. Therefore,

new data (D) overwrites word C in RSR1. If DRR1 is not read in time, the next word can overwrite D.

Figure 12-21. Overrun in the McBSP Receiver

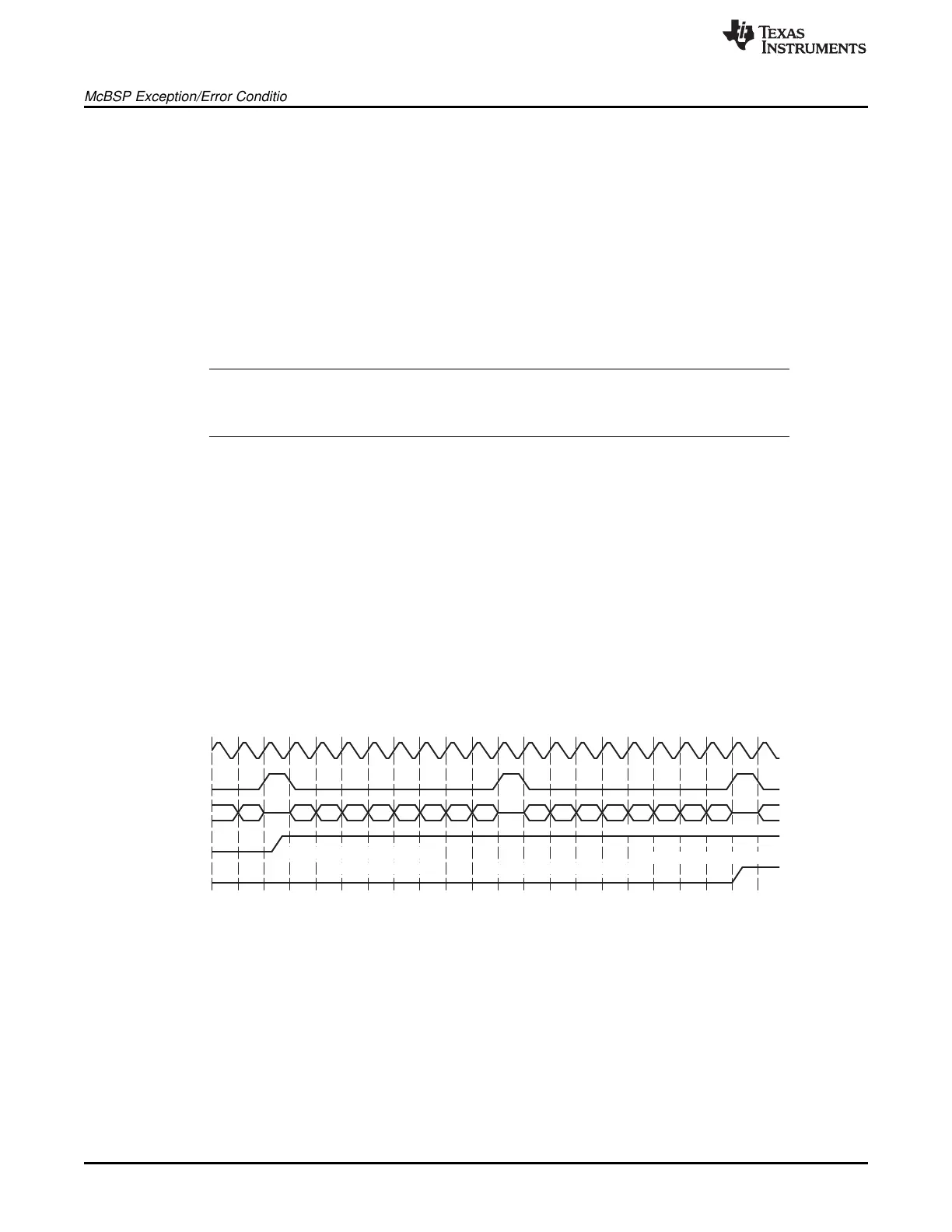

12.5.2.2 Example of Preventing Overrun Condition

Figure 12-22 shows the case where RFULL is set, but the overrun condition is prevented by a read from

DRR1 at least 2.5 cycles before the next serial word ©) is completely shifted into RSR1. This ensures that

an RBR1-to-DRR1 copy of word B occurs before receiver attempts to transfer word C from RSR1 to

RBR1.

Loading...

Loading...