SPI Registers

www.ti.com

580

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

9.5.2.12 SPIPRI Register (Offset = Fh) [reset = 0h]

SPIPRI is shown in Figure 9-19 and described in Table 9-18.

Return to the Summary Table.

SPIPRI controls auxillary functions for the SPI including emulation control, and 3-wire control.

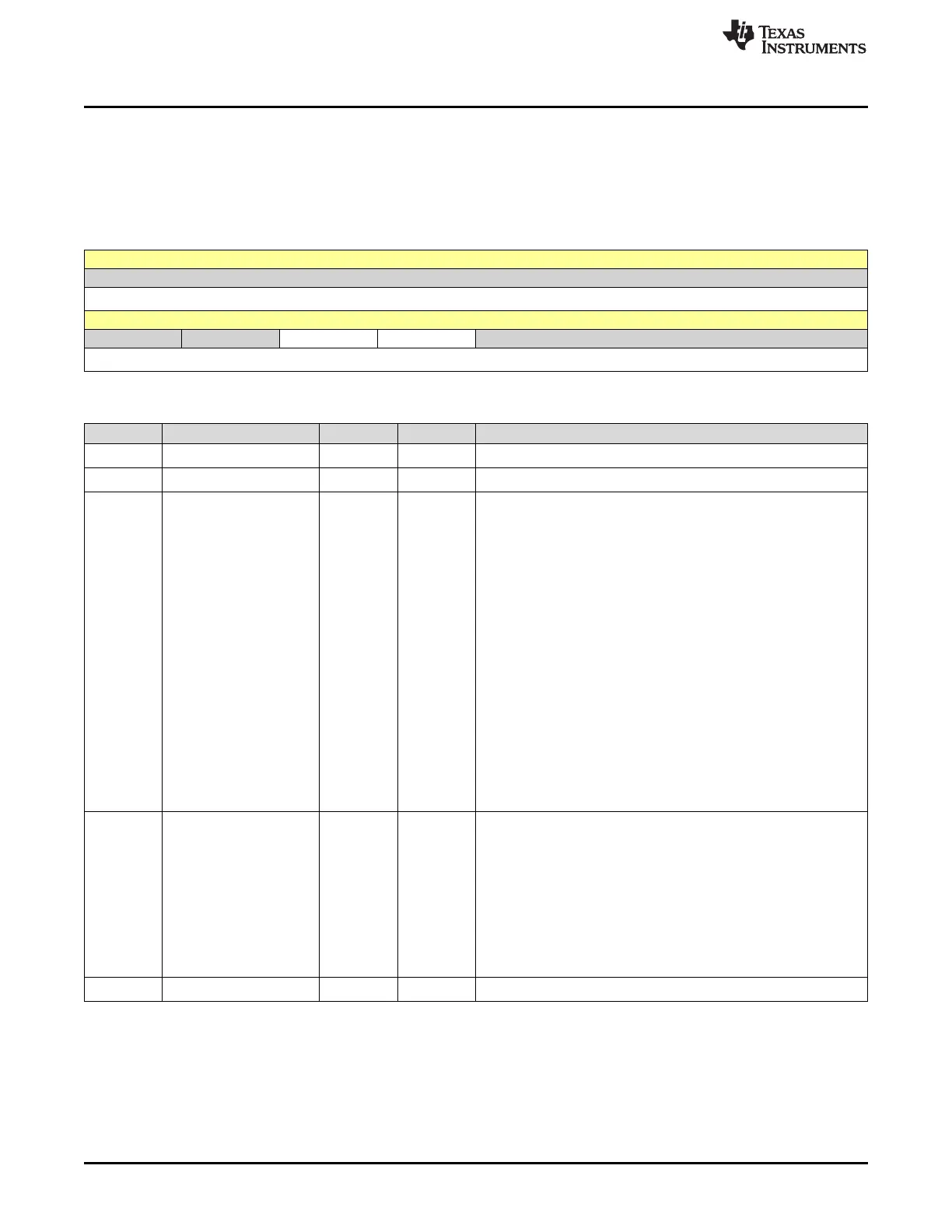

Figure 9-19. SPIPRI Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED RESERVED SOFT FREE RESERVED

R-0h R/W-0h R/W-0h R-0h

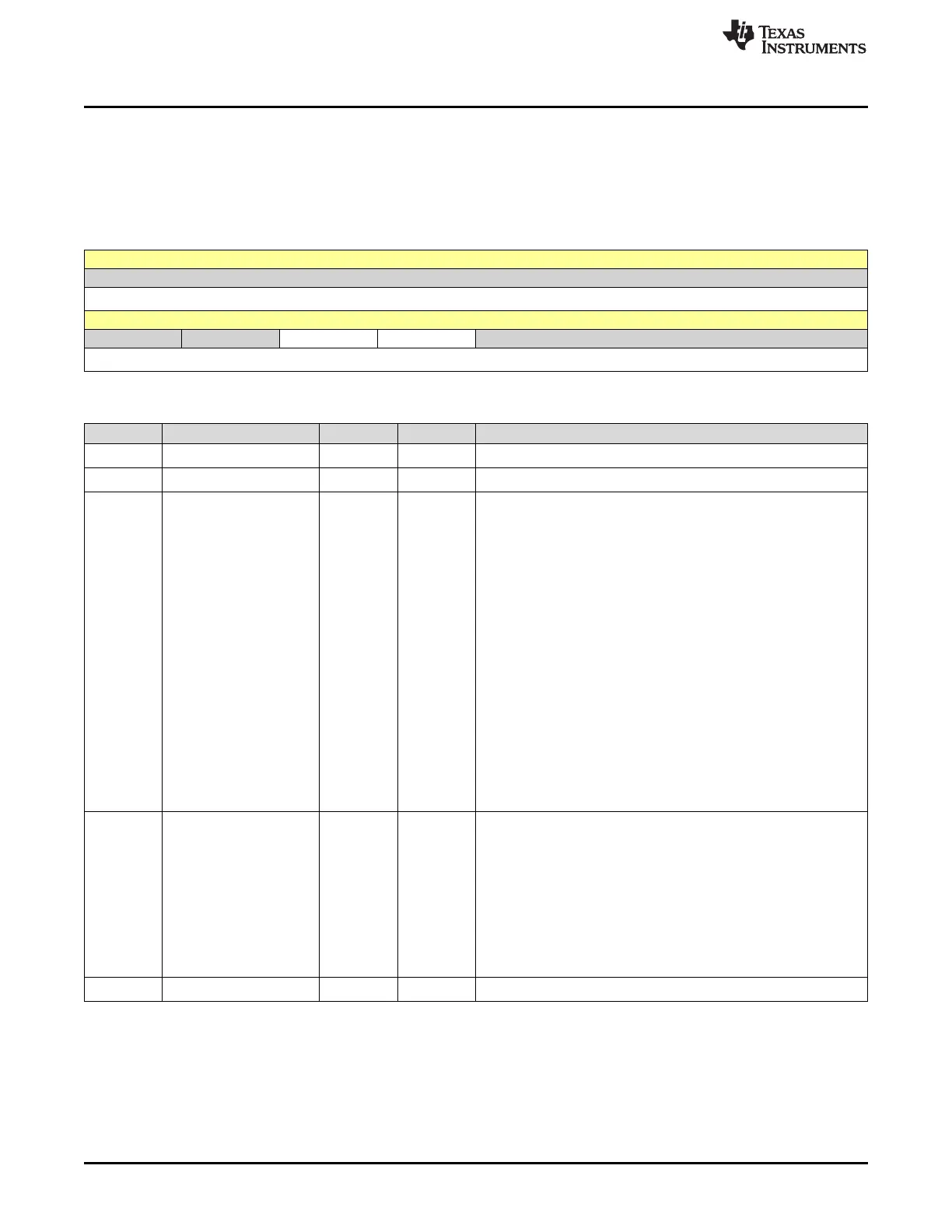

Table 9-18. SPIPRI Register Field Descriptions

Bit Field Type Reset Description

15-7 RESERVED R 0h

Reserved

6 RESERVED R/W 0h

Reserved

5 SOFT R/W 0h

Emulation Soft Run

This bit only has an effect when the FREE bit is 0.

Reset type: SYSRSn

0h (R/W) = Transmission stops midway in the bit stream while

TSUSPEND is asserted. Once TSUSPEND is deasserted without a

system reset, the remainder of the bits pending in the DATBUF are

shifted. Example: If SPIDAT has shifted 3 out of 8 bits, the

communication freezes right there. However, if TSUSPEND is later

deasserted without resetting the SPI, SPI starts transmitting from

where it had stopped (fourth bit in this case) and will transmit 8 bits

from that point.

1h (R/W) = If the emulation suspend occurs before the start of a

transmission, (that is, before the first SPICLK pulse) then the

transmission will not occur. If the emulation suspend occurs after

the start of a transmission, then the data will be shifted out to

completion. When the start of transmission occurs is dependent on

the baud rate used.

Standard SPI mode: Stop after transmitting the words in the shift

register and buffer. That is, after TXBUF and SPIDAT are empty.

In FIFO mode: Stop after transmitting the words in the shift register

and buffer. That is, after TX FIFO and SPIDAT are empty.

4 FREE R/W 0h

Emulation Free Run

These bits determine what occurs when an emulation suspend

occurs (for example, when the debugger hits a breakpoint). The

peripheral can continue whatever it is doing (free-run mode) or, if in

stop mode, it can either stop immediately or stop when the current

operation (the current receive/transmit sequence) is complete.

Reset type: SYSRSn

0h (R/W) = Emulation mode is selected by the SOFT bit

1h (R/W) = Free run, continue SPI operation regardless of suspend

or when the suspend occurred.

3-0 RESERVED R 0h

Reserved

Loading...

Loading...