ADC Registers

www.ti.com

478

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Analog-to-Digital Converter (ADC)

7.4.1 ADCTRL1 Register (Offset = 0h) [reset = 0h]

ADCTRL1 is shown in Figure 7-15 and described in Table 7-10.

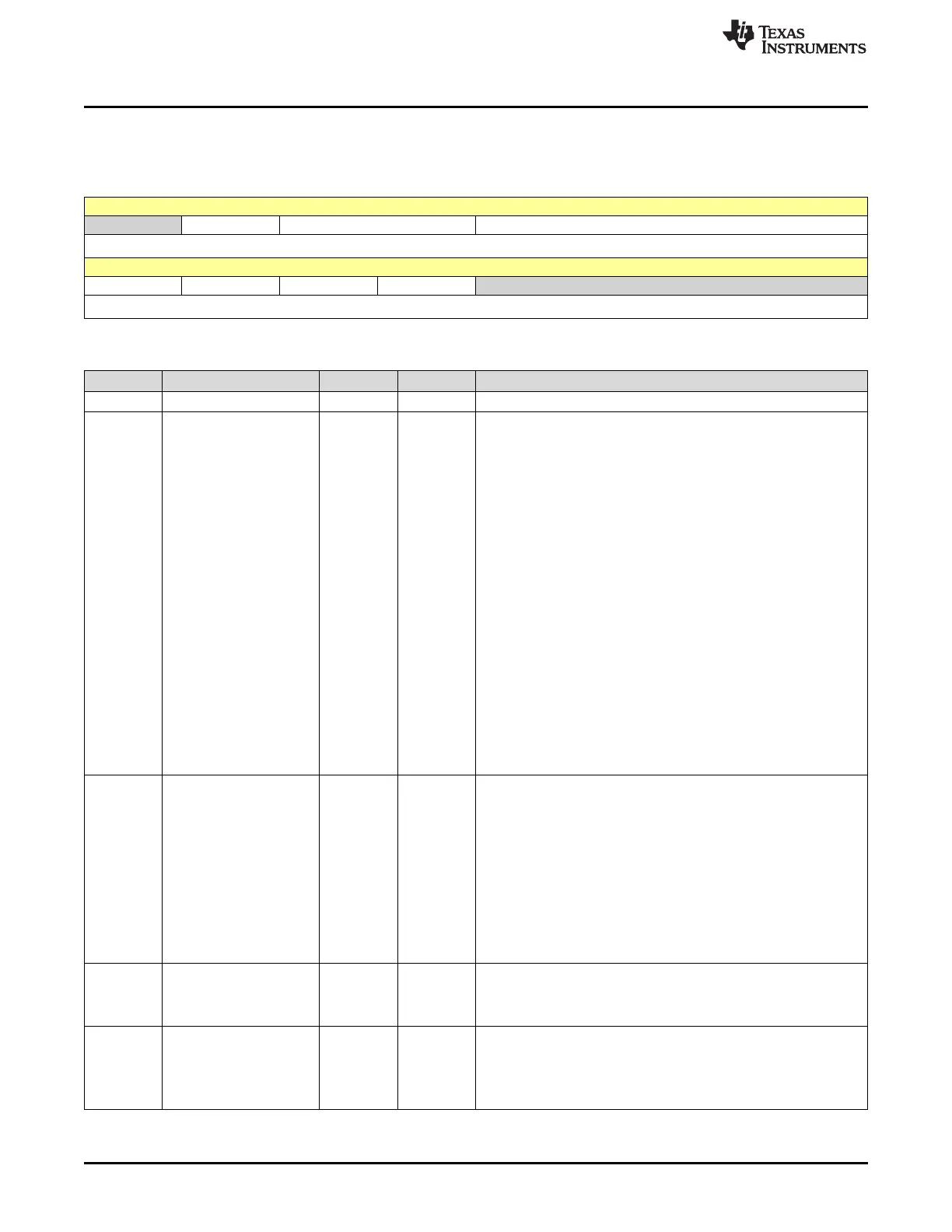

Figure 7-15. ADCTRL1 Register

15 14 13 12 11 10 9 8

RESERVED RESET SUSMOD[1:0] ACQ_PS[3:0]

R-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

CPS CONT_RUN SEQ_OVRD SEQ_CASC RESERVED

R/W-0h R/W-0h R/W-0h R/W-0h R-0h

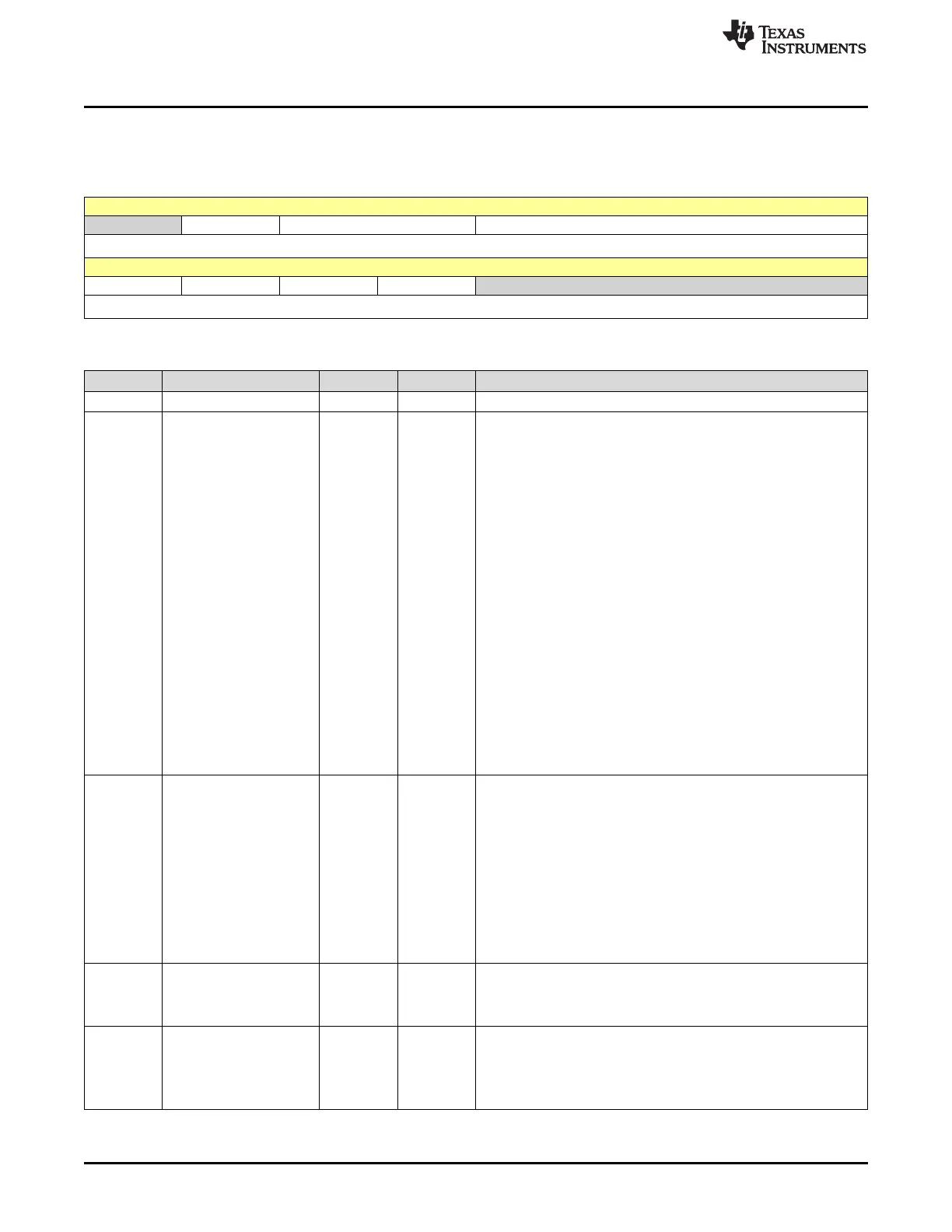

Table 7-10. ADCTRL1 Register Field Descriptions

Bit Field Type Reset Description

15 RESERVED R 0h Reads return a zero. Writes have no effect.

14 RESET R/W 0h ADC module software reset.

This bit causes a master reset on the entire ADC module. All register

bits and sequencer state machines are reset to the initial state as

occurs when the device reset pin is pulled low (or after a power-on

reset). This is a one-time-effect bit, meaning this bit is self-cleared

immediately after it is set to 1. Read of this bit always returns a 0.

Also, the reset of ADC has a latency of two clock cycles (that is,

other ADC control register bits should not be modified until two ADC

clock cycles after the instruction that resets the ADC.

Note: The ADC module is reset during a system reset. If an ADC

module reset is desired at any other time, you can do so by writing a

1 to this bit. After two ADC clock domain cycles, you can then write

the appropriate values to the ADCCTRL1 register bits. The example

below assumes 150-MHz DSP Clock and 25-MHz ADCCLK.

Assembly code:

MOV ADCTRL1, #00xxxxxxxxxxxxxxb Configures ADCTRL1 to user-

desired value.

RPT #10|| NOP; Provides the required delay between writes to

ADCTRL1

MOV ADCTRL1, #01xxxxxxxxxxxxxxb Resets the ADC (RESET = 1)

Note that the second MOV is not required if the default configuration

is sufficient.

0h = No effect

1h = Resets entire ADC module (bit is then set back to 0 by ADC

logic)

13-12 SUSMOD[1:0] R/W 0h Emulation-suspend mode. These bits determine what occurs when

an emulation-suspend occurs (due to the debugger hitting a

breakpoint, for example).

00b = Mode 0. Emulation suspend is ignored.

01b = Mode 1. Sequencer and other wrapper logic stops after

current sequence is complete, final result is latched, and state

machine is updated.

10b = Mode 2. Sequencer and other wrapper logic stops after

current conversion is complete, result is latched, and state machine

is updated.

11b = Mode 3. Sequencer and other wrapper logic stops

immediately on emulation suspend.

11-8 ACQ_PS[3:0] R/W 0h Acquisition window size. This bit field controls the width of SOC

pulse, which, in turn, determines for what time duration the sampling

switch is closed. The width of SOC pulse is ADCTRL1[11:8] + 1

times the ADCLK period.

7 CPS R/W 0h Core clock prescaler. The prescaler is applied to divided device

peripheral clock, HSPCLK.

Note: F

clk

= Prescaled HSPCLK (ADCCLKPS[3:0])

0h = ADCCLK = F

clk

/1

1h = ADCCLK = F

clk

/2

Loading...

Loading...