www.ti.com

ADC Registers

479

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Analog-to-Digital Converter (ADC)

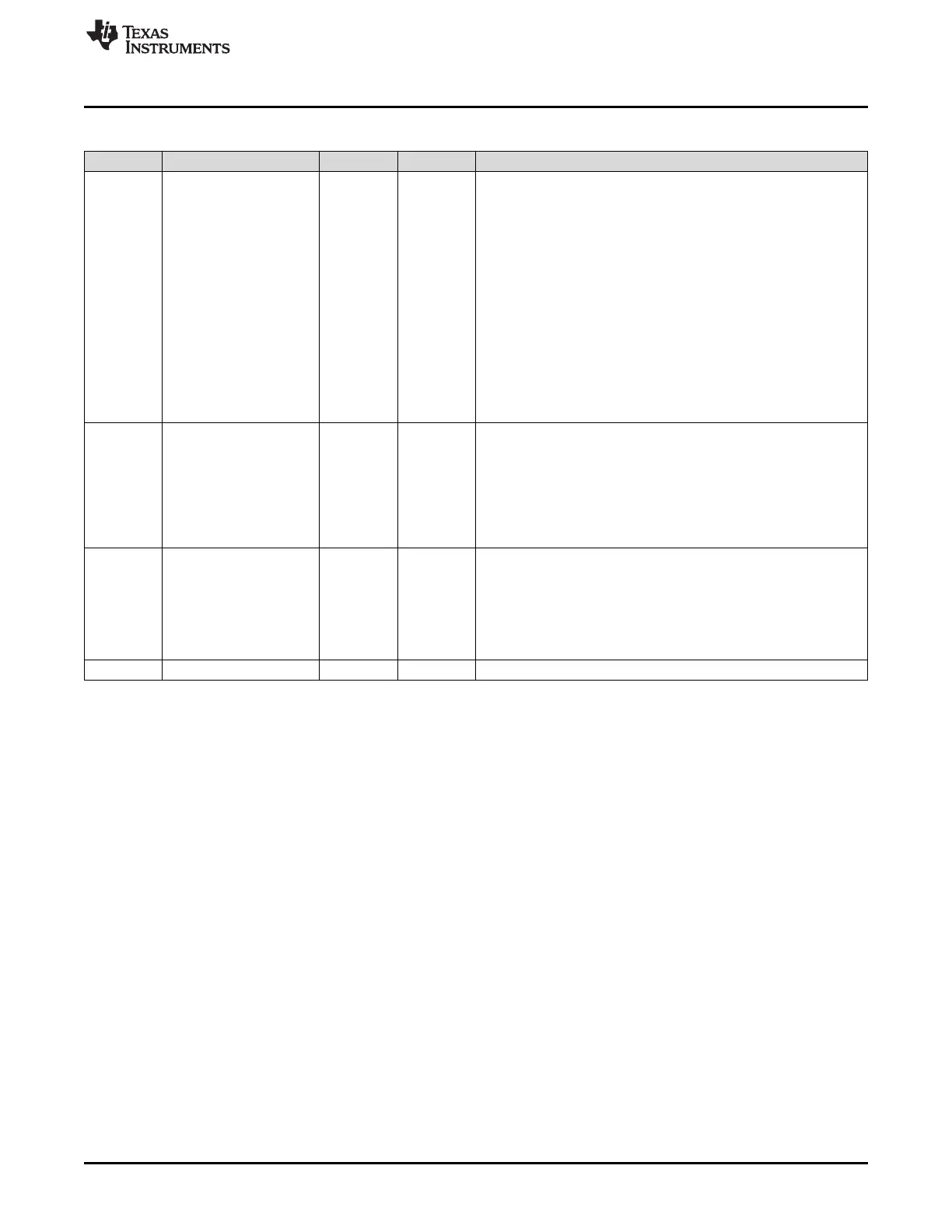

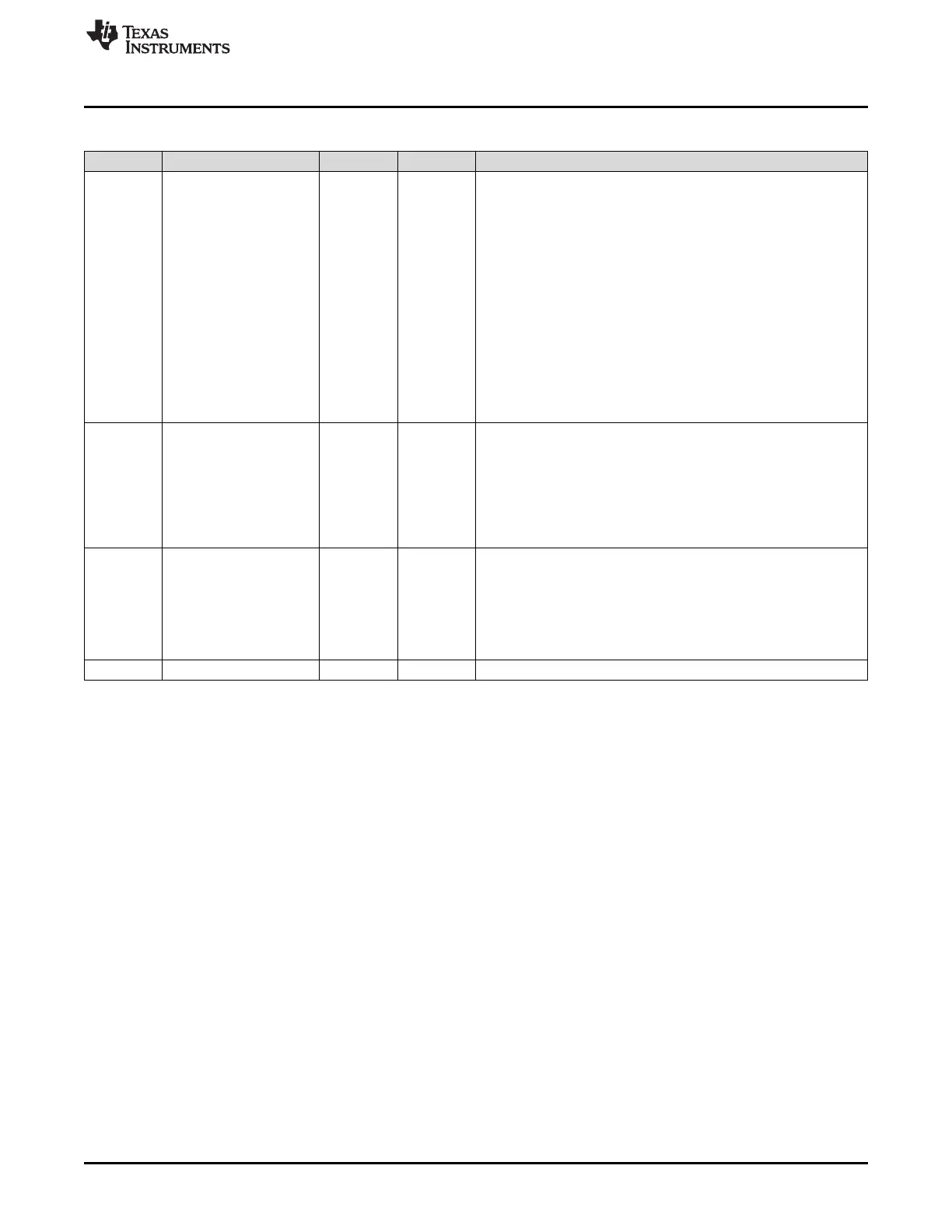

Table 7-10. ADCTRL1 Register Field Descriptions (continued)

Bit Field Type Reset Description

6 CONT_RUN R/W 0h Continuous run. This bit determines whether the sequencer operates

in continuous conversion mode or start-stop mode. This bit can be

written while a current conversion sequence is active. This bit will

take effect at the end of the current conversion sequence i.e.,

software can set/clear this bit until EOS has occurred, for valid action

to be taken. In the continuous conversion mode, there is no need to

reset the sequencer however, the sequencer must be reset in the

start-stop mode to put the converter in state CONV00.

0h = Start-stop mode. Sequencer stops after reaching EOS. On the

next SOC, the sequencer starts from the state where it ended unless

a sequencer reset is performed.

1h = Continuous conversion mode. After reaching EOS, the behavior

of the sequencer depends on the state of the SEQ_OVRD bit. If this

bit is cleared, the sequencer starts over again from its reset state

(CONV00 for SEQ1 and cascaded, CONV08 for SEQ2). If

SEQ_OVRD is set, the sequencer starts again from its current

position, without resetting.

5 SEQ_OVRD R/W 0h Sequencer override. Provides additional sequencer flexibility in

continuous run mode by overriding the wrapping around at the end

of conversions set by MAX_CONVn.

0h = Disabled - Allows the sequencer to wrap around at the end of

conversions set by MAX_CONVn.

1h = Enabled - Overrides the sequencer from wrapping around at

the end of conversions set by MAX_CONVn. Wraparound occurs

only at the end of the sequencer.

4 SEQ_CASC R/W 0h Cascaded sequencer operation. This bit determines whether SEQ1

and SEQ2 operate as two 8-state sequencers or as a single 16-state

sequencer (SEQ).

0h = Dual-sequencer mode. SEQ1 and SEQ2 operate as two 8-state

sequencers.

1h = Cascaded mode. SEQ1 and SEQ2 operate as a single 16-state

sequencer (SEQ).

3-0 RESERVED R 0h Reads return zero. Writes have no effect.

Loading...

Loading...