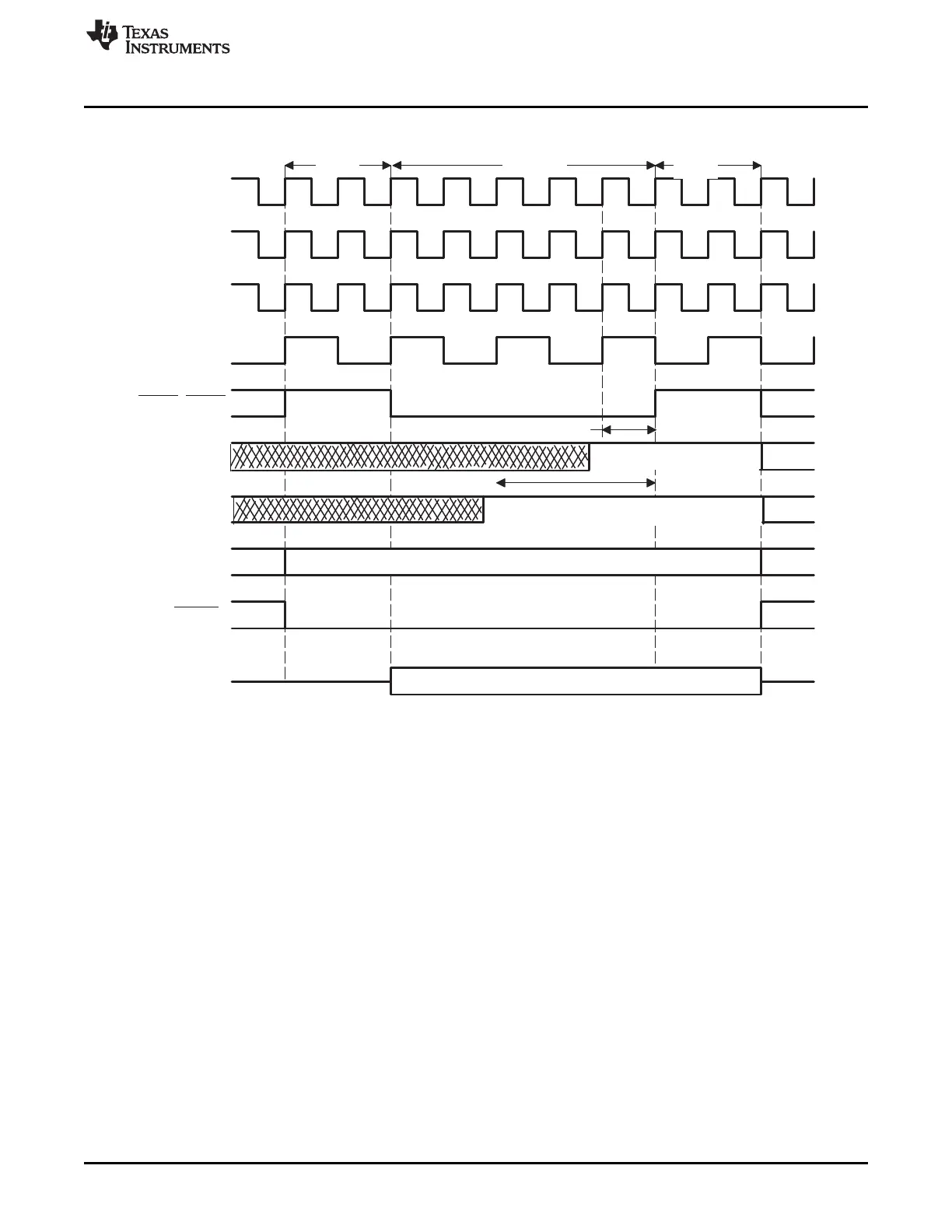

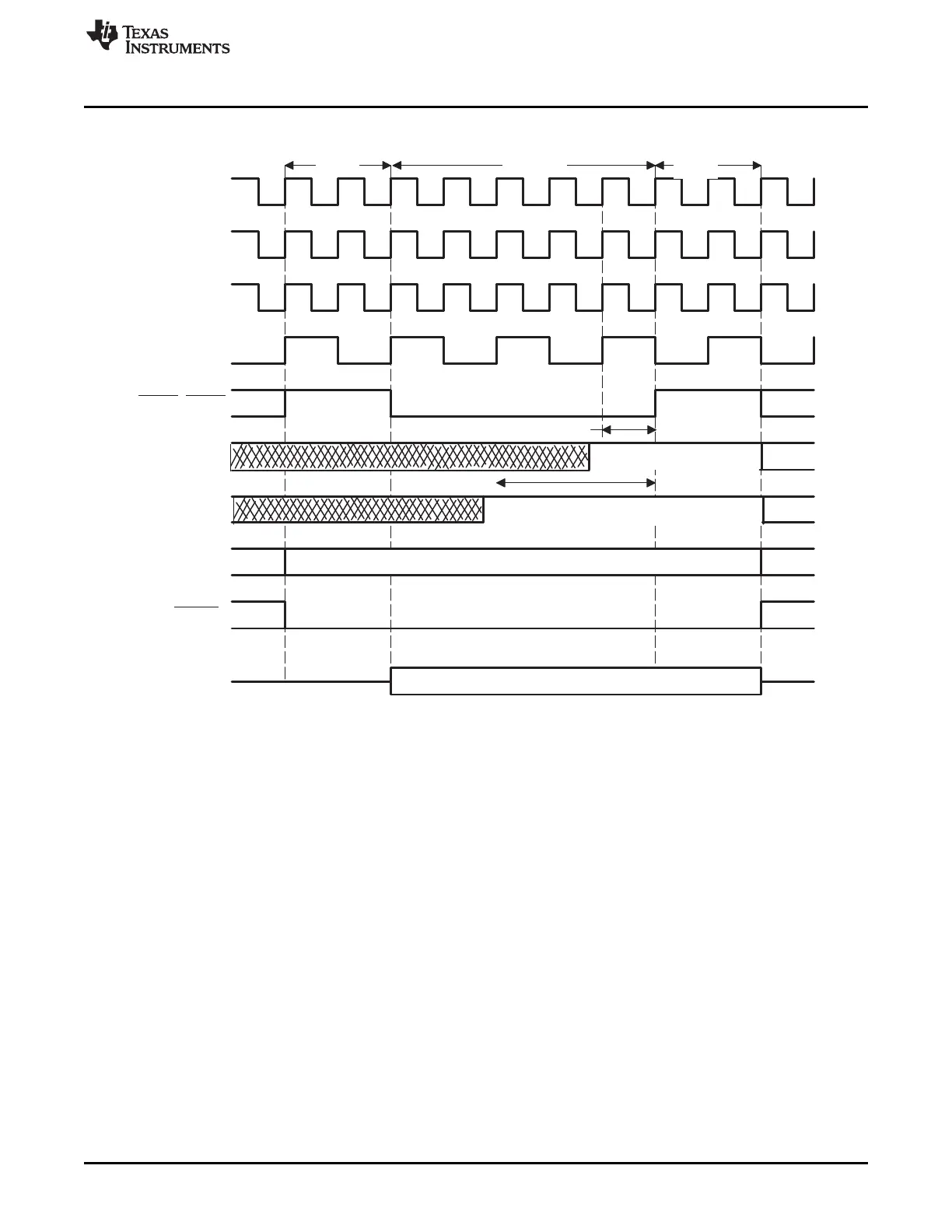

valid

valid

Lead

Active

Trail

1XTIMCLK

3XTIMCLK

SYSCLKOUT

XTIMCLK

(/1 Mode)

XCLKOUT

(/1 Mode)

XCLKOUT

(/2 Mode)

XWE0, XWE1

XREADY

(synch)

XREADY

(asynch)

XA(19:0)

XZCSx

XD(15:0)

or XD(31:0)

www.ti.com

Waveforms

867

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

External Interface (XINTF)

Figure 14-15. Generic Write Cycle (XTIMCLK = SYSCLKOUT mode)

A XWRACTIVE = 2, XWRACTIVE = 4, XWRTRAIL = 2

B If the lead and active timing parameters are set low enough, it may not be possible to generate a valid XREADY

signal. No hardware is added to detect this.

Loading...

Loading...