I2C Registers

www.ti.com

642

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

11.6.2.6 I2CCNT Register (Offset = 5h) [reset = 0h]

I2CCNT is shown in Figure 11-23 and described in Table 11-15.

Return to the Summary Table.

I2CCNT is a 16-bit register used to indicate how many data bytes to transfer when the I2C module is

configured as a transmitter, or to receive when configured as a master receiver. In the repeat mode (RM =

1), I2CCNT is not used.

The value written to I2CCNT is copied to an internal data counter. The internal data counter is

decremented by 1 for each byte transferred (I2CCNT remains unchanged). If a STOP condition is

requested in the master mode (STP = 1 in I2CMDR), the I2C module terminates the transfer with a STOP

condition when the countdown is complete (that is, when the last byte has been transferred).

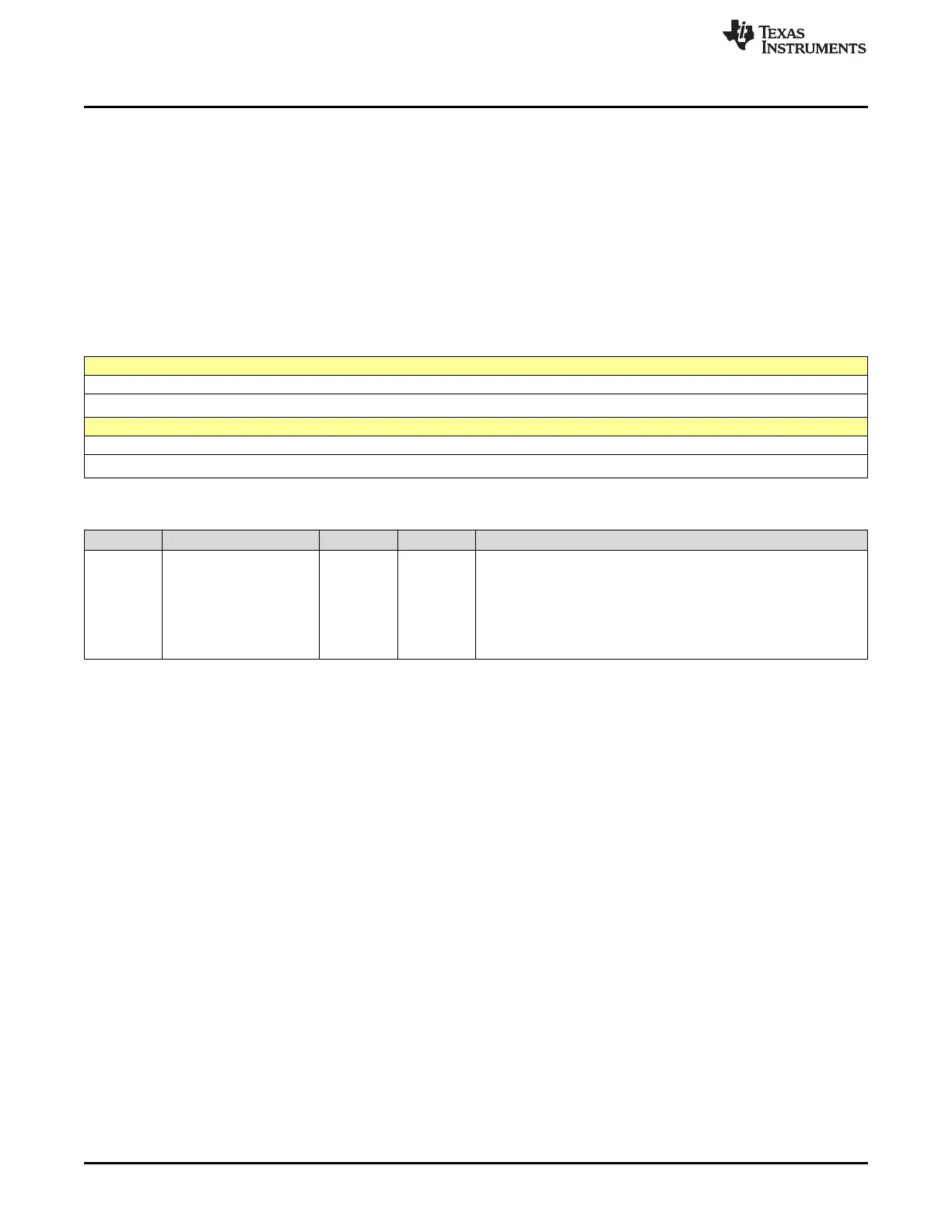

Figure 11-23. I2CCNT Register

15 14 13 12 11 10 9 8

I2CCNT

R/W-0h

7 6 5 4 3 2 1 0

I2CCNT

R/W-0h

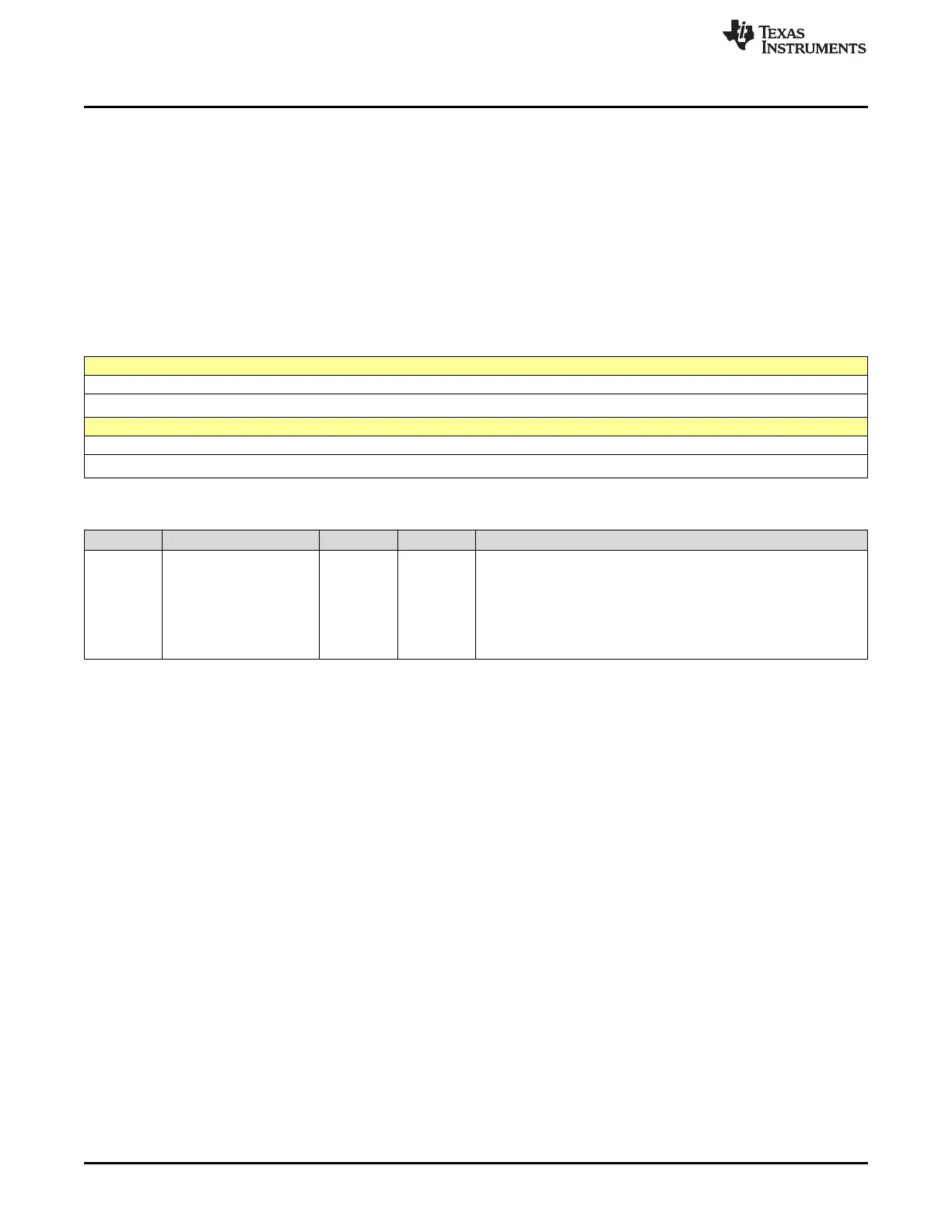

Table 11-15. I2CCNT Register Field Descriptions

Bit Field Type Reset Description

15-0 I2CCNT R/W 0h

Data count value. I2CCNT indicates the number of data bytes to

transfer or receive. The value in I2CCNT is a don't care when the

RM bit in I2CMDR is set to 1.

The start value loaded to the internal data counter is 65536.

The start value loaded to internal data counter is 1-65535.

Reset type: SYSRSn

Loading...

Loading...