www.ti.com

Register Descriptions

519

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

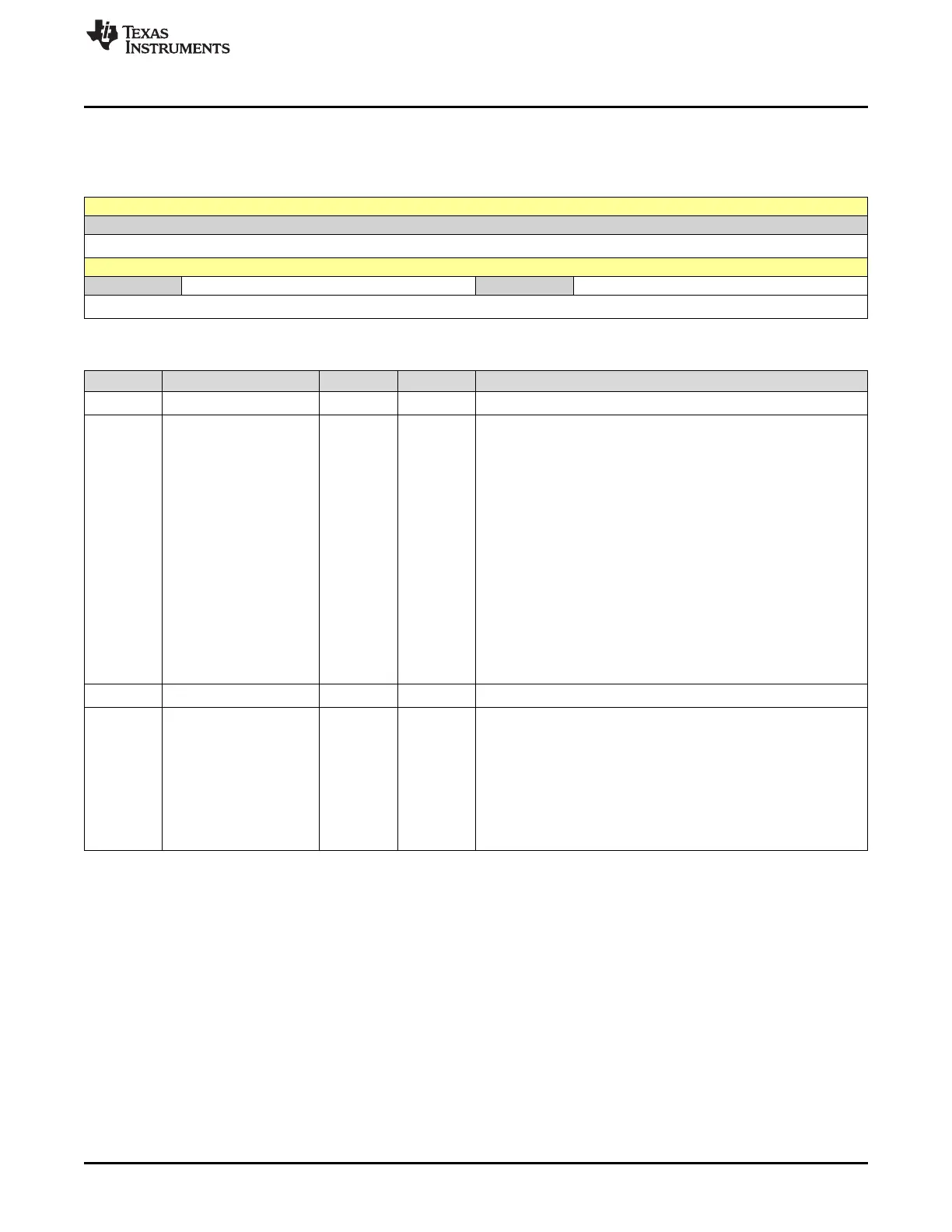

8.9.5 PRIORITYSTAT Register (Offset = 1006h) [reset = 0h]

PRIORITYSTAT is shown in Figure 8-12 and described in Table 8-7.

Figure 8-12. PRIORITYSTAT Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED ACTIVESTS_SHADOW RESERVED ACTIVESTS

R-0h R-0h R-0h R-0h

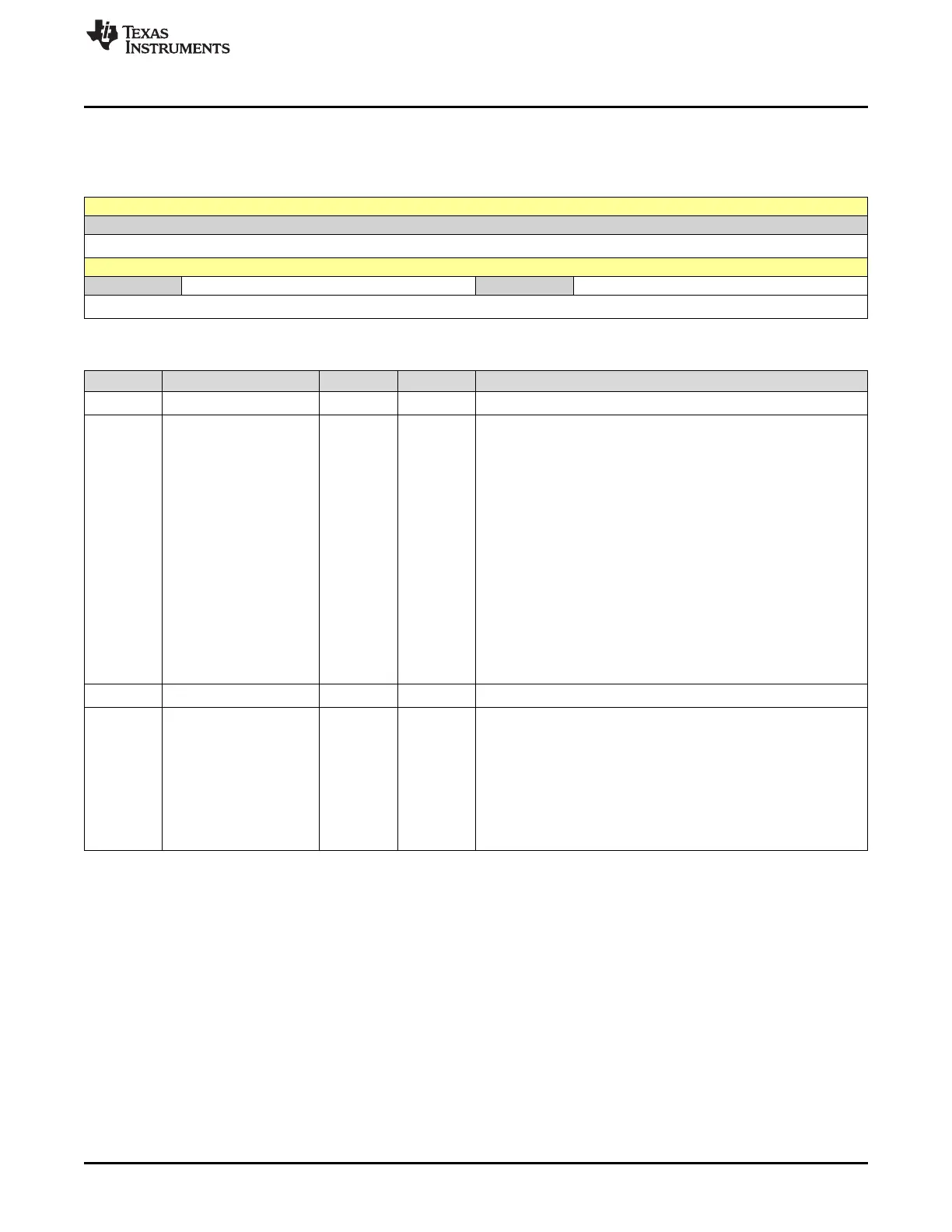

Table 8-7. PRIORITYSTAT Register Field Descriptions

Bit Field Type Reset Description

15-7 RESERVED R 0h

Reserved

6-4 ACTIVESTS_SHADOW R 0h Active Channel Status Shadow Bits: These bits are only useful when

CH1 is enabled as a higher priority channel.

When CH1 is serviced, the ACTIVESTS bits are copied to the

shadow bits and indicate which channel was interrupted by CH1.

When CH1 service is completed, the shadow bits are copied back to

the ACTIVESTS bits.

If this bit field is zero or the same as the ACTIVESTS bit field, then

no channel is pending due to a CH1 interrupt.

When CH1 is not a higher priority channel, these bits should be

ignored:

0h = No channel pending

1h = CH 1

2h = CH 2

3h = CH 3

4h = CH 4

5h = CH 5

6h = CH 6

3 RESERVED R 0h

Reserved

2-0 ACTIVESTS R 0h

Active Channel Status Bits: These bits indicate which channel is

currently active or performing a transfer: 000b = no channel active

1h = CH 1

2h = CH 2

3h = CH 3

4h = CH 4

5h = CH 5

6h = CH 6

Loading...

Loading...