www.ti.com

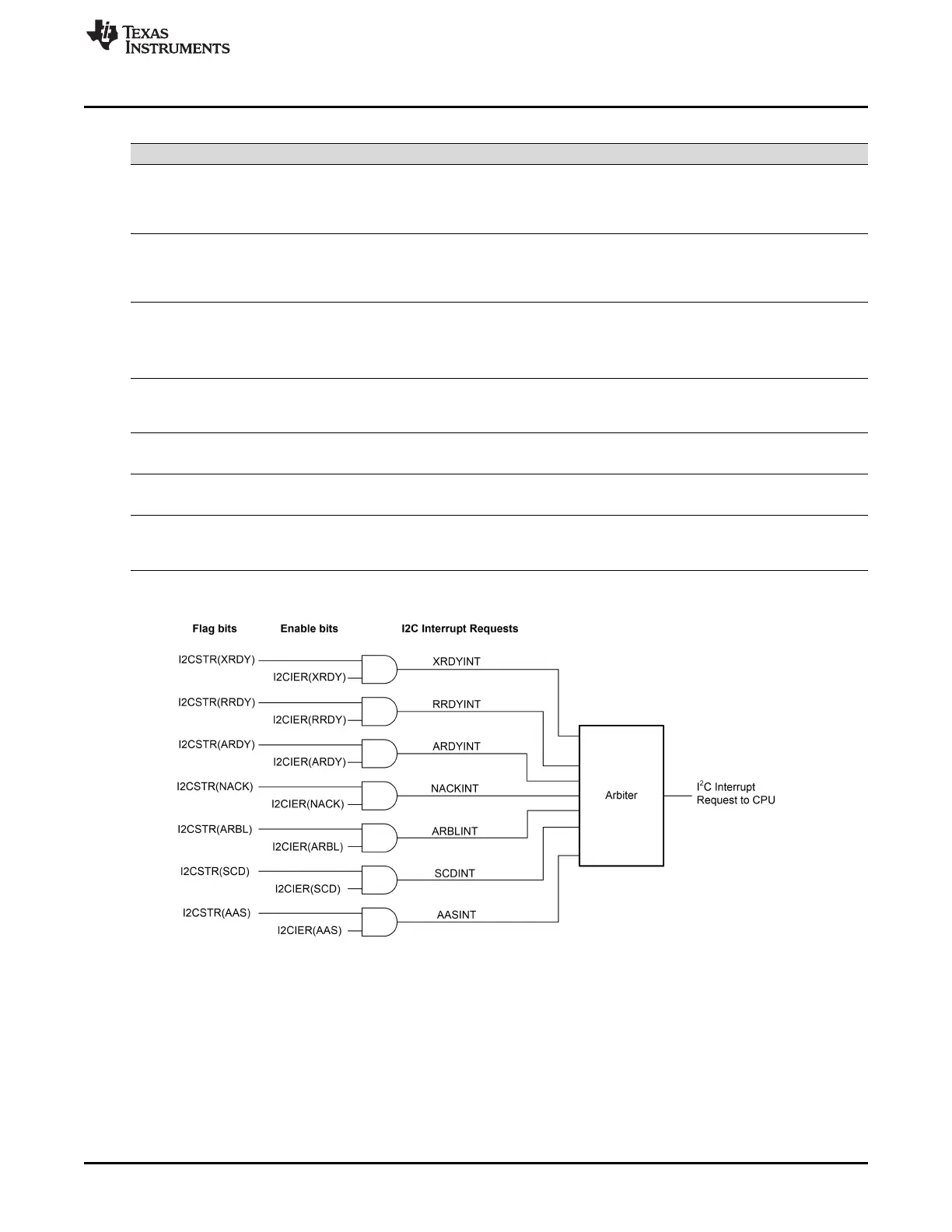

Interrupt Requests Generated by the I2C Module

629

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

Table 11-6. Descriptions of the Basic I2C Interrupt Requests

I2C Interrupt Request Interrupt Source

XRDYINT Transmit ready condition: The data transmit register (I2CDXR) is ready to accept new data because the

previous data has been copied from I2CDXR to the transmit shift register (I2CXSR).

As an alternative to using XRDYINT, the CPU can poll the XRDY bit of the status register, I2CSTR.

XRDYINT should not be used when in FIFO mode. Use the FIFO interrupts instead.

RRDYINT Receive ready condition: The data receive register (I2CDRR) is ready to be read because data has been

copied from the receive shift register (I2CRSR) to I2CDRR.

As an alternative to using RRDYINT, the CPU can poll the RRDY bit of I2CSTR. RRDYINT should not

be used when in FIFO mode. Use the FIFO interrupts instead.

ARDYINT Register-access ready condition: The I2C module registers are ready to be accessed because the

previously programmed address, data, and command values have been used.

The specific events that generate ARDYINT are the same events that set the ARDY bit of I2CSTR.

As an alternative to using ARDYINT, the CPU can poll the ARDY bit.

NACKINT No-acknowledgment condition: The I2C module is configured as a master-transmitter and did not

received acknowledgment from the slave-receiver.

As an alternative to using NACKINT, the CPU can poll the NACK bit of I2CSTR.

ARBLINT Arbitration-lost condition: The I2C module has lost an arbitration contest with another master-transmitter.

As an alternative to using ARBLINT, the CPU can poll the ARBL bit of I2CSTR.

SCDINT Stop condition detected: A STOP condition was detected on the I2C bus.

As an alternative to using SCDINT, the CPU can poll the SCD bit of the status register, I2CSTR.

AASINT Addressed as slave condition: The I2C has been addressed as a slave device by another master on the

I2C bus.

As an alternative to using AASINT, the CPU can poll the AAS bit of the status register, I2CSTR.

Figure 11-15. Enable Paths of the I2C Interrupt Requests

The I2C module has a backwards compatibility bit (BC) in the I2CEMDR register. The timing diagram in

Figure 11-16 demonstrates the effect the backwards compatibility bit has on I2C module registers and

interrupts when configured as a slave-transmitter.

Loading...

Loading...