SCI Registers

www.ti.com

610

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

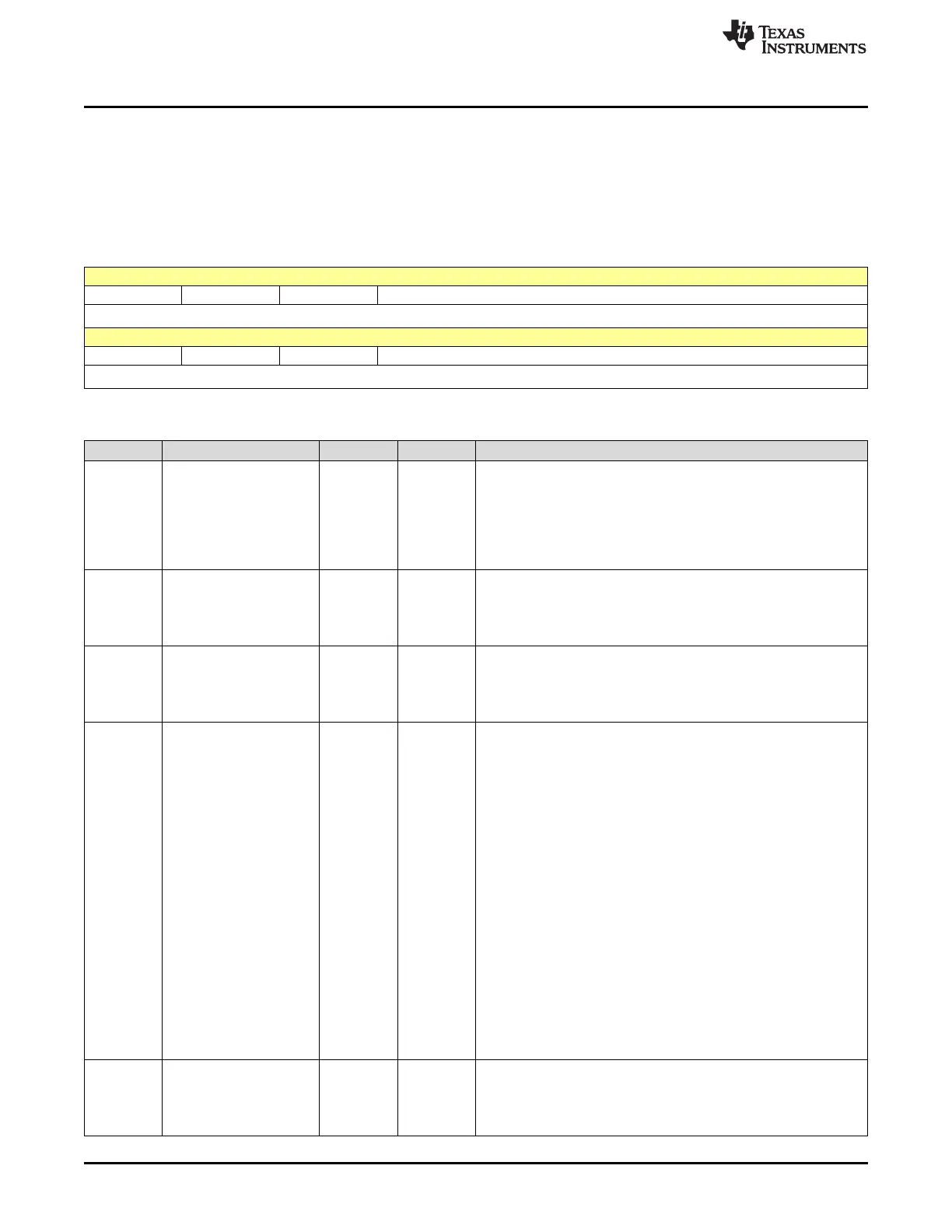

10.14.2.10 SCIFFTX Register (Offset = Ah) [reset = A000h]

SCIFFTX is shown in Figure 10-20 and described in Table 10-16.

Return to the Summary Table.

SCIFFTX controls the transmit FIFO interrupt, FIFO enhancements, and reset for the SCI transmit and

receive channels.

Figure 10-20. SCIFFTX Register

15 14 13 12 11 10 9 8

SCIRST SCIFFENA TXFIFORESET TXFFST

R/W-1h R/W-0h R/W-1h R-0h

7 6 5 4 3 2 1 0

TXFFINT TXFFINTCLR TXFFIENA TXFFIL

R-0h R-0/W1S-0h R/W-0h R/W-0h

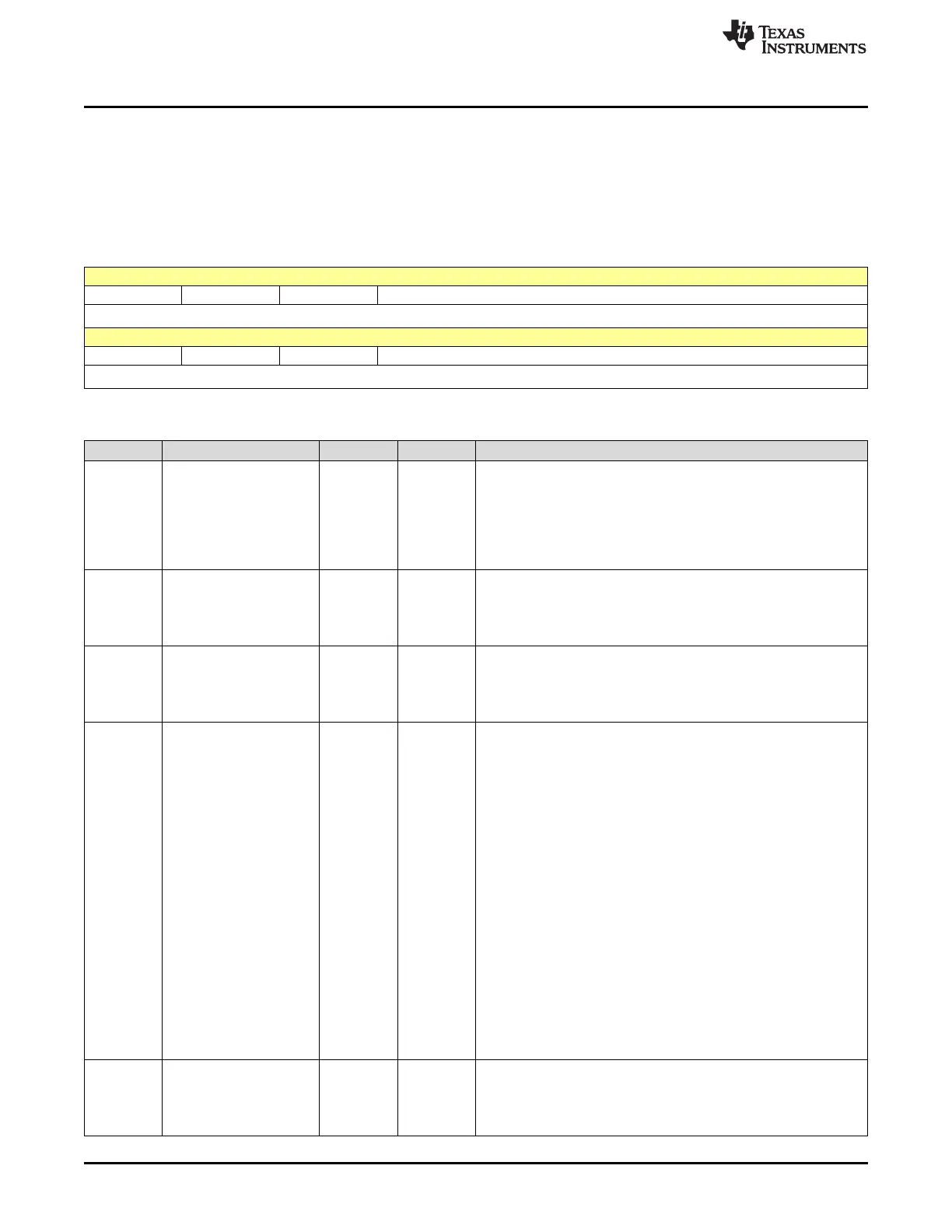

Table 10-16. SCIFFTX Register Field Descriptions

Bit Field Type Reset Description

15 SCIRST R/W 1h

SCI Reset

0 Write 0 to reset the SCI transmit and receive channels. SCI FIFO

register configuration bits will be left as is.

1 SCI FIFO can resume transmit or receive. SCIRST should be 1

even for Autobaud logic to work.

Reset type: SYSRSn

14 SCIFFENA R/W 0h

SCI FIFO enable

Reset type: SYSRSn

0h (R/W) = SCI FIFO enhancements are disabled

1h (R/W) = SCI FIFO enhancements are enabled

13 TXFIFORESET R/W 1h

Transmit FIFO reset

Reset type: SYSRSn

0h (R/W) = Reset the FIFO pointer to zero and hold in reset

1h (R/W) = Re-enable transmit FIFO operation

12-8 TXFFST R 0h

FIFO status

Reset type: SYSRSn

0h (R/W) = Transmit FIFO is empty

1h (R/W) = Transmit FIFO has 1 words

2h (R/W) = Transmit FIFO has 2 words

3h (R/W) = Transmit FIFO has 3 words

4h (R/W) = Transmit FIFO has 4 words

5h (R/W) = Transmit FIFO has 5 words

6h (R/W) = Transmit FIFO has 6 words

7h (R/W) = Transmit FIFO has 7 words

8h (R/W) = Transmit FIFO has 8 words

9h (R/W) = Transmit FIFO has 9 words

Ah (R/W) = Transmit FIFO has 10 words

Bh (R/W) = Transmit FIFO has 11 words

Ch (R/W) = Transmit FIFO has 12 words

Dh (R/W) = Transmit FIFO has 13 words

Eh (R/W) = Transmit FIFO has 14 words

Fh (R/W) = Transmit FIFO has 15 words

10h (R/W) = Transmit FIFO has 16 words

7 TXFFINT R 0h

Transmit FIFO interrupt

Reset type: SYSRSn

0h (R/W) = TXFIFO interrupt has not occurred, read-only bit

1h (R/W) = TXFIFO interrupt has occurred, read-only bit

Loading...

Loading...