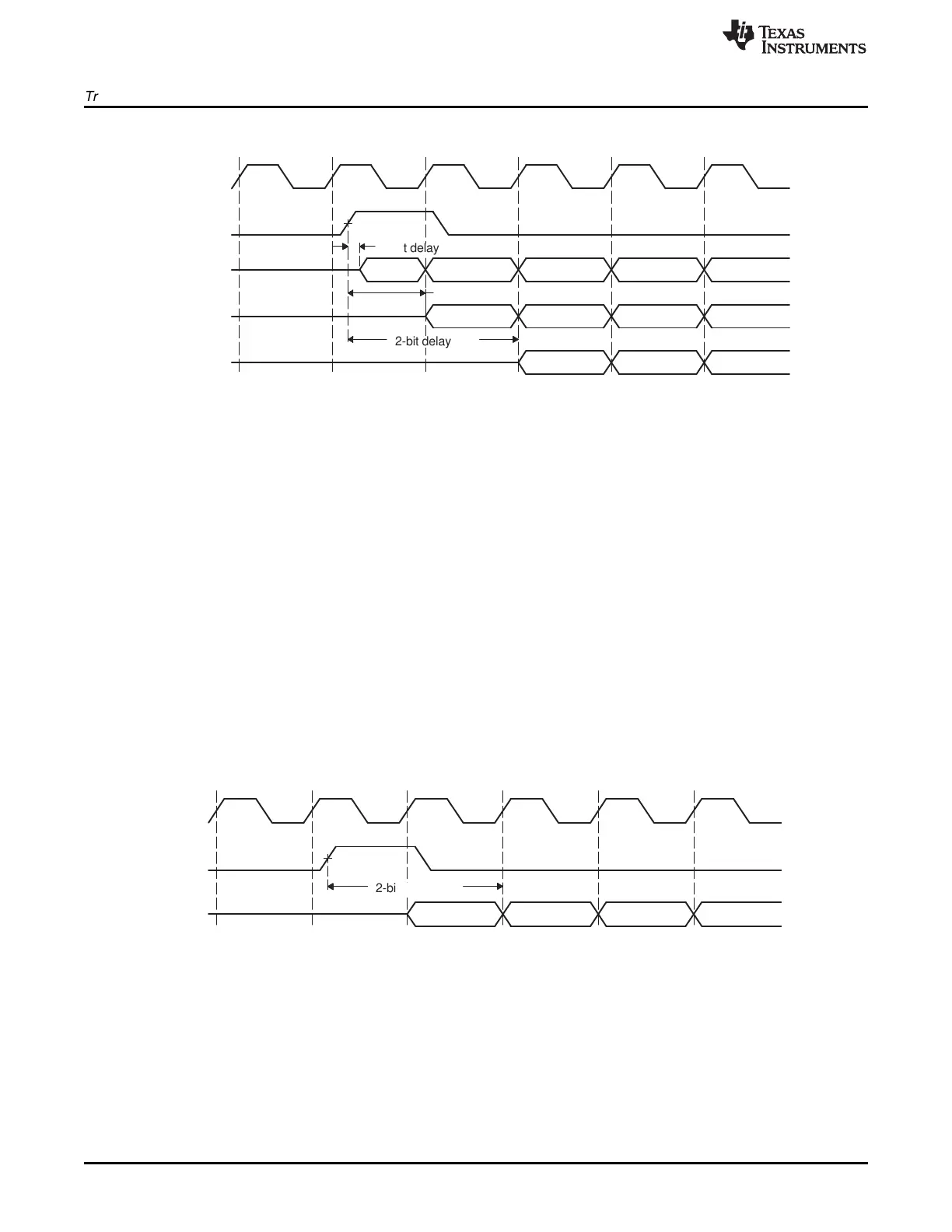

DR Framing bit B5B6B7

FSR

CLKR

B5B6B7

B4B5B6B7

B3B4B5B6B7

Data delay 2

D(R/X)

Data delay 1

D(R/X)

Data delay 0

D(R/X)

FS(R/X)

CLK(R/X)

1-bit delay

Transmitter Configuration

www.ti.com

730

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

Figure 12-56. Range of Programmable Data Delay

12.9.13.2 0-Bit Data Delay

Normally, a frame-synchronization pulse is detected or sampled with respect to an edge of serial clock

internal CLK(R/X). Thus, on the following cycle or later (depending on the data delay value), data can be

received or transmitted. However, in the case of 0-bit data delay, the data must be ready for reception

and/or transmission on the same serial clock cycle.

For reception this problem is solved because receive data is sampled on the first falling edge of MCLKR

where an active-high internal FSR is detected. However, data transmission must begin on the rising edge

of the internal CLKX clock that generated the frame synchronization. Therefore, the first data bit is

assumed to be present in XSR1, and thus DX. The transmitter then asynchronously detects the frame

synchronization, FSX, going active high and immediately starts driving the first bit to be transmitted on the

DX pin.

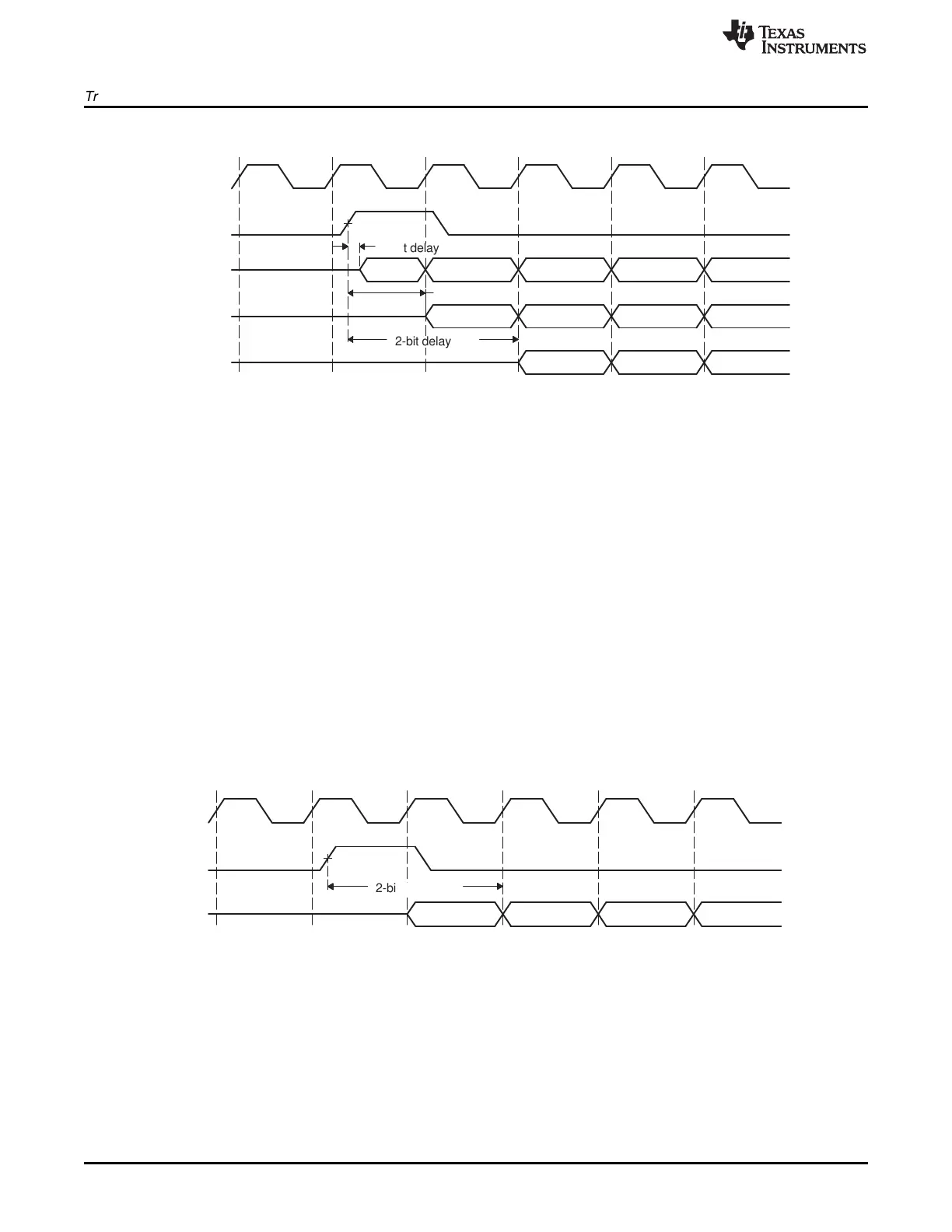

12.9.13.3 2-Bit Data Delay

A data delay of two bit-periods allows the serial port to interface to different types of T1 framing devices

where the data stream is preceded by a framing bit. During reception of such a stream with data delay of

two bits (framing bit appears after a 1-bit delay and data appears after a 2-bit delay), the serial port

essentially discards the framing bit from the data stream, as shown in the following figure. In this figure,

the data transferred is an 8-bit value with bits labeled B7, B6, B5, and so on.

Figure 12-57. 2-Bit Data Delay Used to Skip a Framing Bit

Loading...

Loading...