SCI Registers

www.ti.com

614

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

10.14.2.12 SCIFFCT Register (Offset = Ch) [reset = 0h]

SCIFFCT is shown in Figure 10-22 and described in Table 10-18.

Return to the Summary Table.

SCIFFCT contains the status of auto-baud detect, clears the auto-baud flag, and calibrate for A-detect bit.

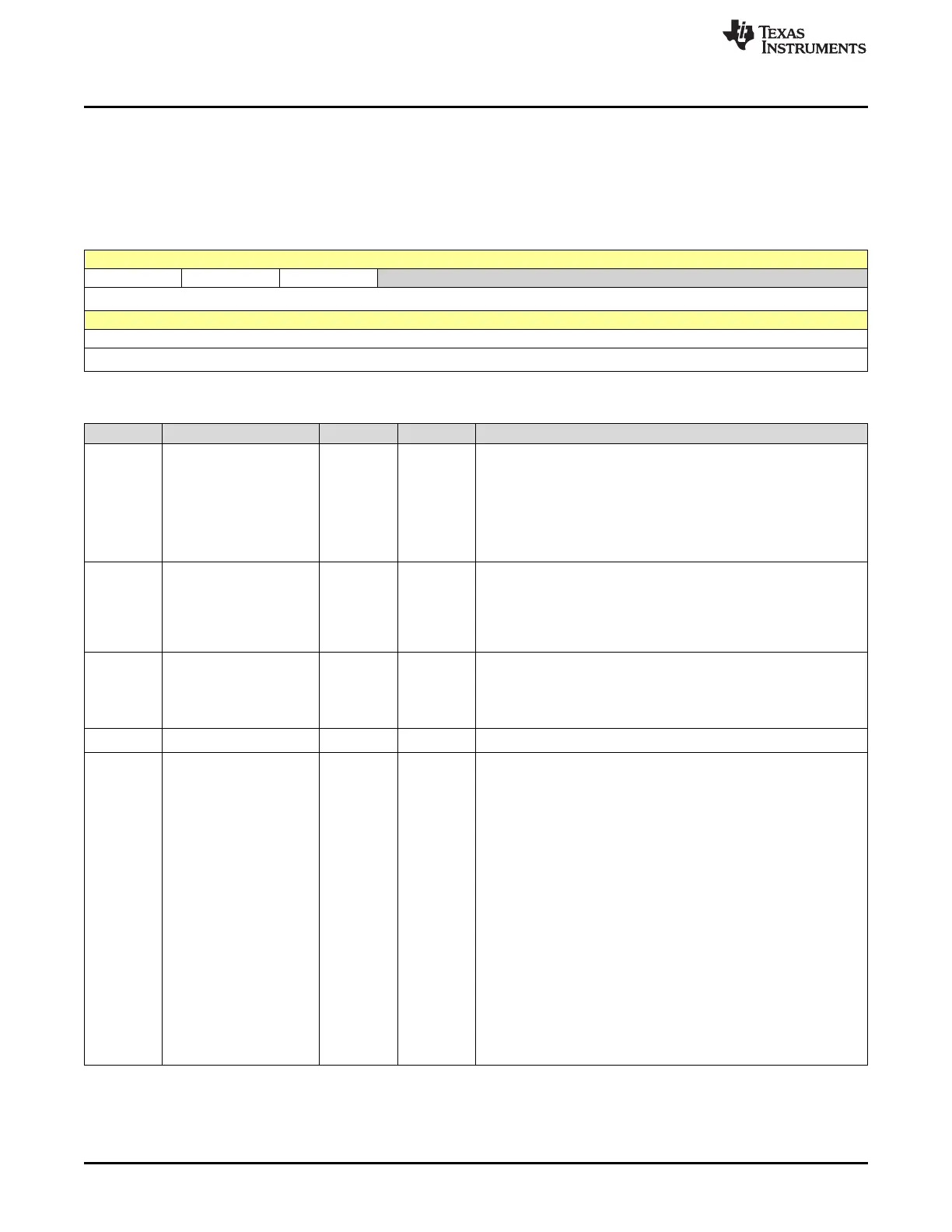

Figure 10-22. SCIFFCT Register

15 14 13 12 11 10 9 8

ABD ABDCLR CDC RESERVED

R-0h W-0h R/W-0h R-0h

7 6 5 4 3 2 1 0

FFTXDLY

R/W-0h

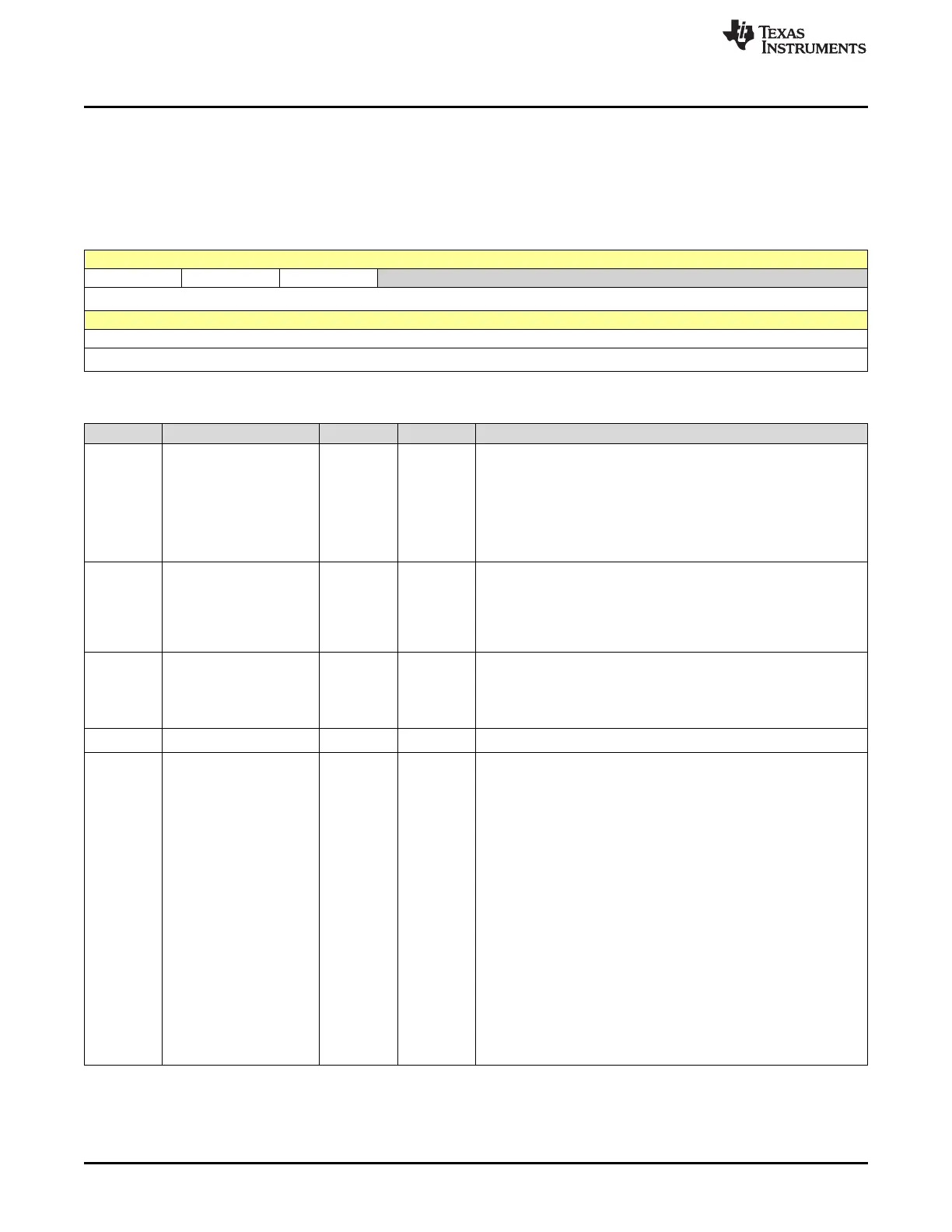

Table 10-18. SCIFFCT Register Field Descriptions

Bit Field Type Reset Description

15 ABD R 0h

Auto-baud detect (ABD) bit

Reset type: SYSRSn

0h (R/W) = Auto-baud detection is not complete. "A","a" character

has not been received successfully.

1h (R/W) = Auto-baud hardware has detected "A" or "a" character

on the SCI receive register. Auto-detect is

complete.

14 ABDCLR W 0h

ABD-clear bit

Reset type: SYSRSn

0h (R/W) = Write 0 has no effect on ABD flag bit. Bit reads back a

zero.

1h (R/W) = Write 1 to clear ABD flag in bit 15.

13 CDC R/W 0h

CDC calibrate A-detect bit

Reset type: SYSRSn

0h (R/W) = Disables auto-baud alignment

1h (R/W) = Enables auto-baud alignment

12-8 RESERVED R 0h

Reserved

7-0 FFTXDLY R/W 0h

FIFO transfer delay. These bits define the delay between every

transfer from FIFO transmit bufferto transmit shift register. The delay

is defined in the number of SCI serial baud clock cycles. The 8 bit

register could define a minimum delay of 0 baud clock cycles and a

maximum of 256 baud clock cycles

In FIFO mode, the buffer (TXBUF) between the shift register and the

FIFO should be filled only after the shift register has completed

shifting of the last bit. This is required to pass on the delay between

transfers to the data stream. In FIFO mode, TXBUF should not be

treated as one additional level of buffer. The delayed transmit feature

will help to create an auto-flow scheme without RTS/CTS controls as

in standard UARTS.

When SCI is configured for one stop-bit, delay introduced by

FFTXDLY between one frame and the next frame is equal to number

of baud clock cycles that FFTXDLY is set to.

When SCI is configured for two stop-bits, delay introduced by

FFTXDLY between one frame and the next frame is equal to number

of baud clock cycles that FFTXDLY is set to minus 1.

Reset type: SYSRSn

Loading...

Loading...