PIE

CONTROL.CHx

[PERINTFLG]

Latch

DMA

channelinterrupt

CONTROL.CHx

[OVRFLG]

DMACHxinterruptgenerated

atbeginningorendoftransfer

MODE.CHx

[CHINTE]

PERx_INT

CONTROL.CHx

[ERRCLR]

MODE.CHx

[OVERNITE]

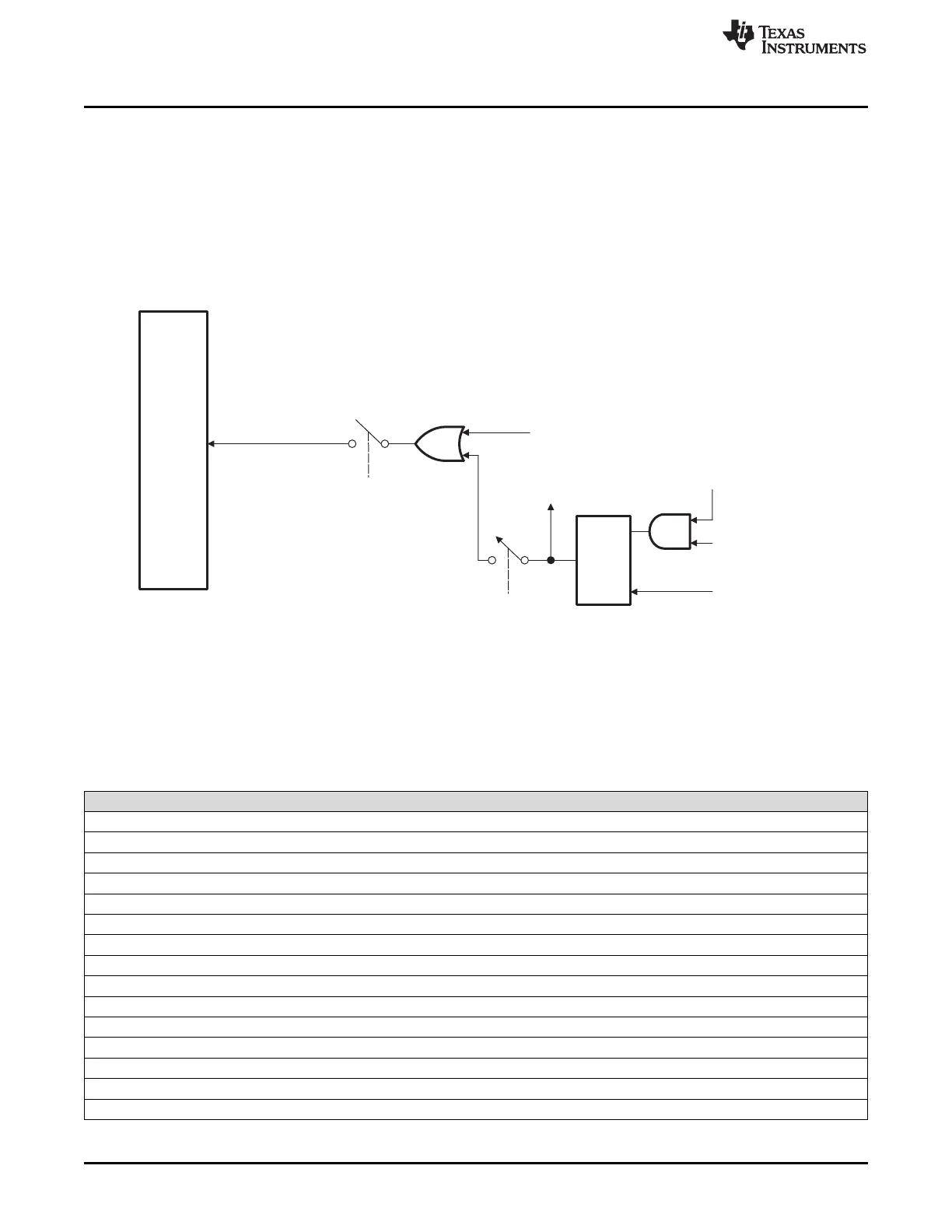

Overrun Detection Feature

www.ti.com

510

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

8.8 Overrun Detection Feature

The DMA contains overrun detection logic. When a peripheral event trigger is received by the DMA, the

PERINTFLG bit in the CONTROL register is set, pending the channel to the DMA state machine. When

the burst for that channel is started, the PERINTFLG is cleared. If however, between the time that the

PERINTFLG bit is set by an event trigger and cleared by the start of the burst, an additional event trigger

arrives, the second trigger will be lost. This condition will set the OVRFLG bit in the CONTROL register as

in Figure 8-7. If the overrun interrupt is enabled then the channel interrupt will be generated to the PIE

module.

Figure 8-7. Overrun Detection Logic

8.9 Register Descriptions

Table 8-2 lists the memory-mapped registers for the DMA_REGISTER_SUMMARY. All register offset

addresses not listed in Table 8-2 should be considered as reserved locations and the register contents

should not be modified.

(1)

All DMA register writes are EALLOW protected.

Table 8-2. DMA Register Summary

(1)

Offset Acronym Register Name Section

1000h DMACTRL DMA Control Register Section 8.9.1

1001h DEBUGCTRL Debug Control Register Section 8.9.2

1002h REVISION Peripheral Revision Register Section 8.9.3

1004h PRIORITYCTRL1 Priority Control Register 1 Section 8.9.4

1006h PRIORITYSTAT Priority Status Register Section 8.9.5

1020h MODE_0 Mode Register Section 8.9.6

1021h CONTROL_0 Control Register Section 8.9.7

1022h BURST_SIZE_0 Burst Size Register Section 8.9.8

1023h BURST_COUNT_0 Burst Count Register Section 8.9.9

1024h SRC_BURST_STEP_0 Source Burst Step Size Register Section 8.9.10

1025h DST_BURST_STEP_0 Destination Burst Step Size Register Section 8.9.11

1026h TRANSFER_SIZE_0 Transfer Size Register Section 8.9.12

1027h TRANSFER_COUNT_0 Transfer Count Register Section 8.9.13

1028h SRC_TRANSFER_STEP_0 Source Transfer Step Size Register Section 8.9.14

1029h DST_TRANSFER_STEP_0 Destination Transfer Step Size Register Section 8.9.15

Loading...

Loading...