Flash Pipeline

CPU

32 bits

M

U

X

Data read from either program or data memory

Instruction Fetch (64 bits)

Flash or OTP

Read

16 bits

Flash and OTP

Instruction buffer

64-bit

Buffer

64-bit

Buffer

Flash and OTP Memory Blocks

www.ti.com

42

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

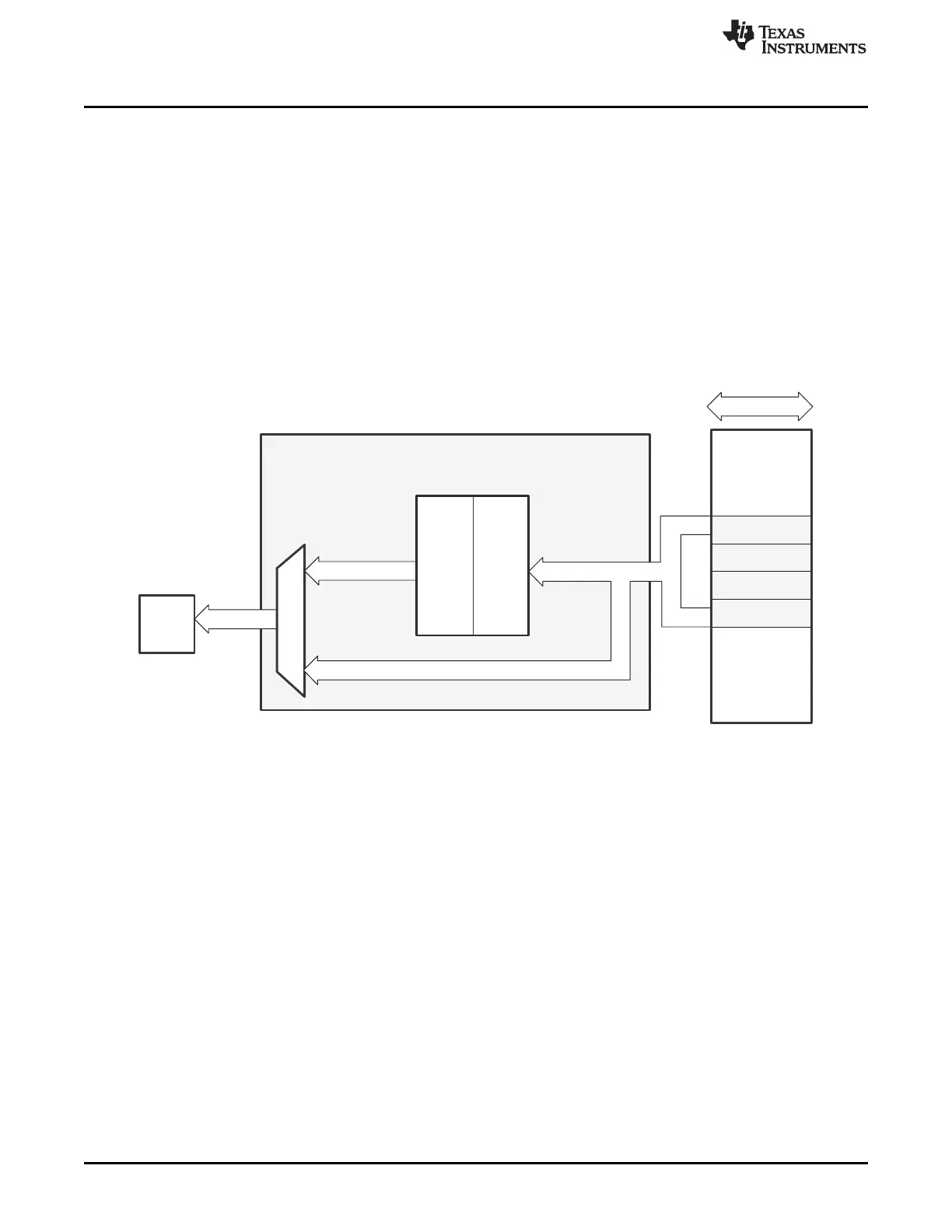

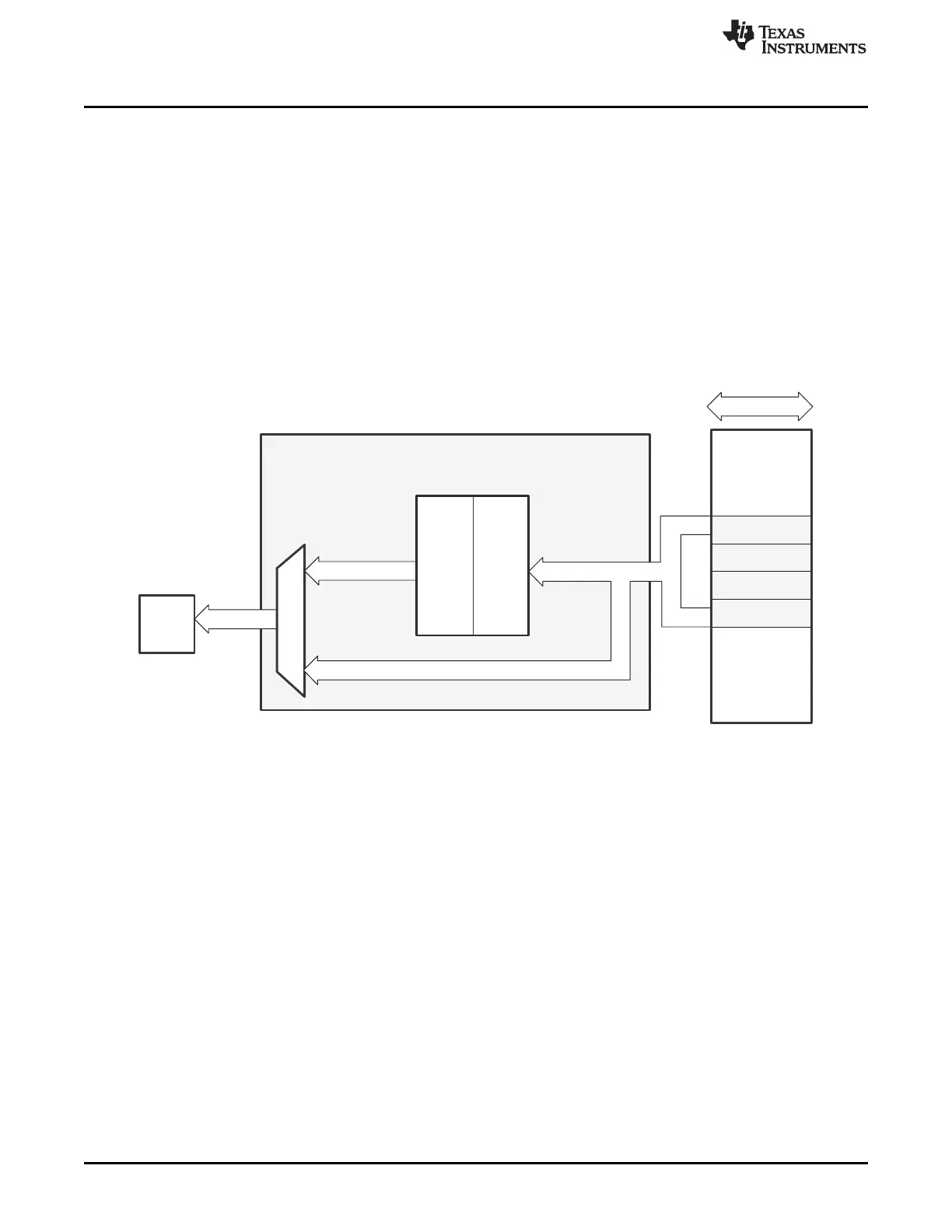

An instruction fetch from the flash or OTP reads out 64 bits per access. The starting address of the access

from flash is automatically aligned to a 64-bit boundary such that the instruction location is within the 64

bits to be fetched. With flash pipeline mode enabled (see Figure 1-2), the 64 bits read from the instruction

fetch are stored in a 64-bit wide by 2-level deep instruction pre-fetch buffer. The contents of this pre-fetch

buffer are then sent to the CPU for processing as required.

Up to two 32-bit instructions or up to four 16-bit instructions can reside within a single 64-bit access. The

majority of C28x instructions are 16 bits, so for every 64-bit instruction fetch from the flash bank it is likely

that there are up to four instructions in the pre-fetch buffer ready to process through the CPU. During the

time it takes to process these instructions, the flash pipeline automatically initiates another access to the

flash bank to pre-fetch the next 64 bits. In this manner, the flash pipeline mode works in the background to

keep the instruction pre-fetch buffers as full as possible. Using this technique, the overall efficiency of

sequential code execution from flash or OTP is improved significantly.

Figure 1-2. Flash Pipeline

The flash pipeline pre-fetch is aborted only on a PC discontinuity caused by executing an instruction such

as a branch, BANZ, call, or loop. When this occurs, the pre-fetch is aborted and the contents of the pre-

fetch buffer are flushed. There are two possible scenarios when this occurs:

1. If the destination address is within the flash or OTP, the pre-fetch aborts and then resumes at the

destination address.

2. If the destination address is outside of the flash and OTP, the pre-fetch is aborted and begins again

only when a branch is made back into the flash or OTP. The flash pipeline pre-fetch mechanism only

applies to instruction fetches from program space. Data reads from data memory and from program

memory do not utilize the pre-fetch buffer capability and thus bypass the pre-fetch buffer. For example,

instructions such as MAC, DMAC, and PREAD read a data value from program memory. When this

read happens, the pre-fetch buffer is bypassed but the buffer is not flushed. If an instruction pre-fetch

is already in progress when a data read operation is initiated, then the data read will be stalled until the

pre-fetch completes.

1.1.3.3 Reserved Locations Within Flash and OTP

When allocating code and data to flash and OTP memory, keep the following in mind:

1. Address locations 0x33 FFF6 and 0x33 FFF7 are reserved for an "entry into flash" branch instruction.

When the "boot to flash" boot option is used, the boot ROM will jump to address 0x33 FFF6. If you

program a branch instruction here that will then re-direct code execution to the entry point of the

application.

2. For code security operation, all addresses between 0x33 FF80 and 0x33 FFF5 cannot be used for

Loading...

Loading...