I2C Registers

www.ti.com

634

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

11.6.2.1 I2COAR Register (Offset = 0h) [reset = 0h]

I2COAR is shown in Figure 11-18 and described in Table 11-10.

Return to the Summary Table.

The I2C own address register (I2COAR) is a 16-bit register. The I2C module uses this register to specify

its own slave address, which distinguishes it from other slaves connected to the I2C-bus. If the 7-bit

addressing mode is selected (XA = 0 in I2CMDR), only bits 6-0 are used

write 0s to bits 9-7.

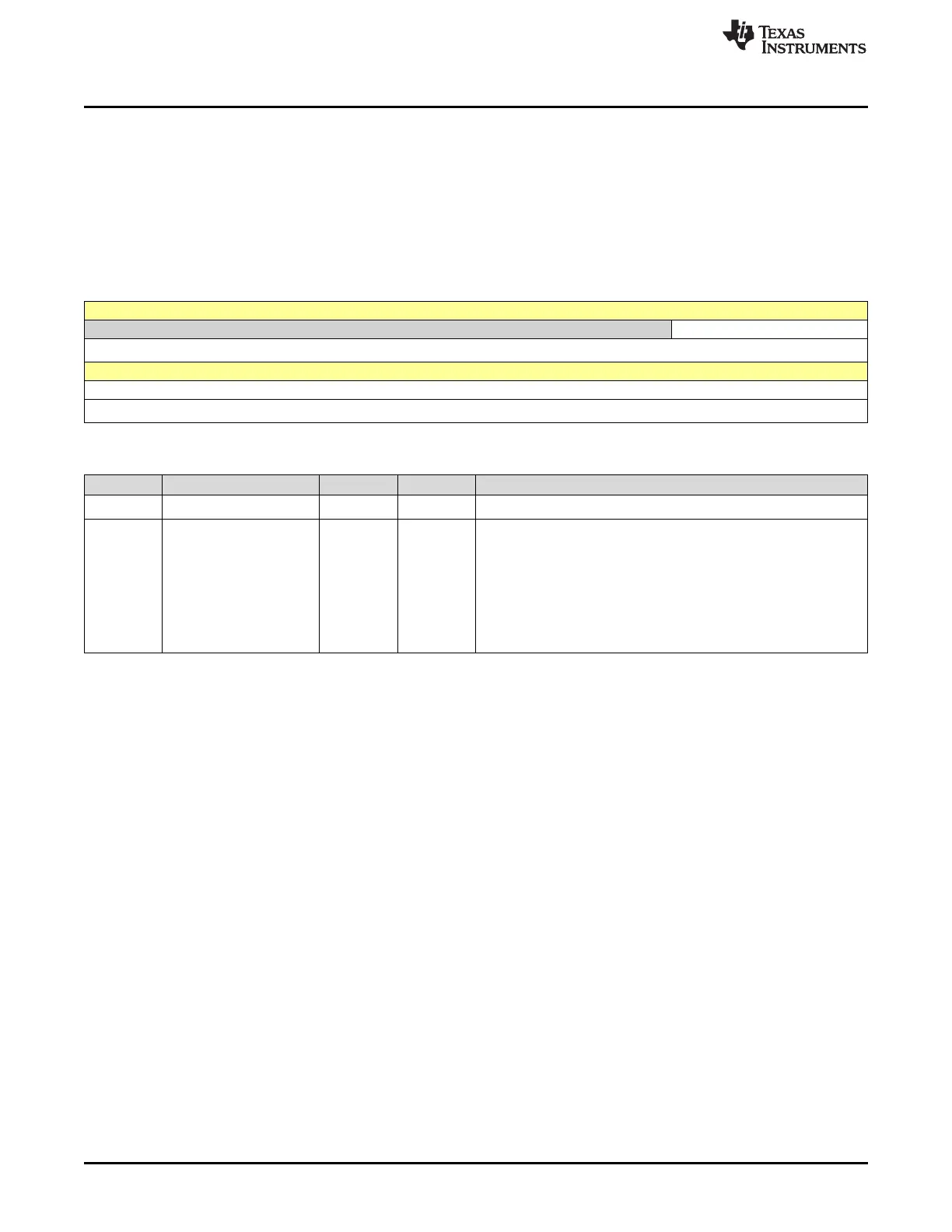

Figure 11-18. I2COAR Register

15 14 13 12 11 10 9 8

RESERVED OAR

R-0h R/W-0h

7 6 5 4 3 2 1 0

OAR

R/W-0h

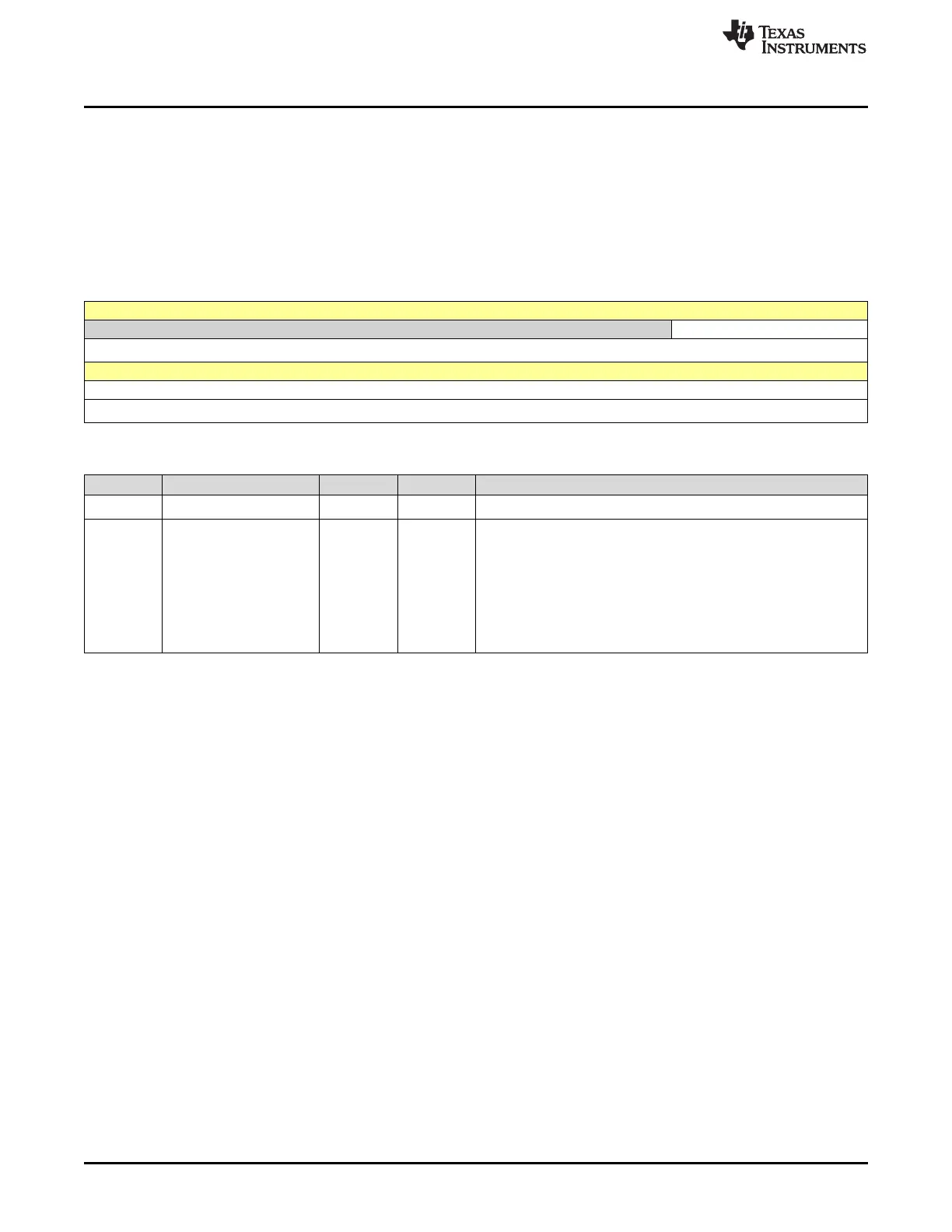

Table 11-10. I2COAR Register Field Descriptions

Bit Field Type Reset Description

15-10 RESERVED R 0h

Reserved

9-0 OAR R/W 0h

In 7-bit addressing mode (XA = 0 in I2CMDR):

00h-7Fh Bits 6-0 provide the 7-bit slave address of the I2C module.

Write 0s to bits 9-7.

In 10-bit addressing mode (XA = 1 in I2CMDR):

000h-3FFh Bits 9-0 provide the 10-bit slave address of the I2C

module.

Reset type: SYSRSn

Loading...

Loading...