www.ti.com

McBSP Registers

755

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

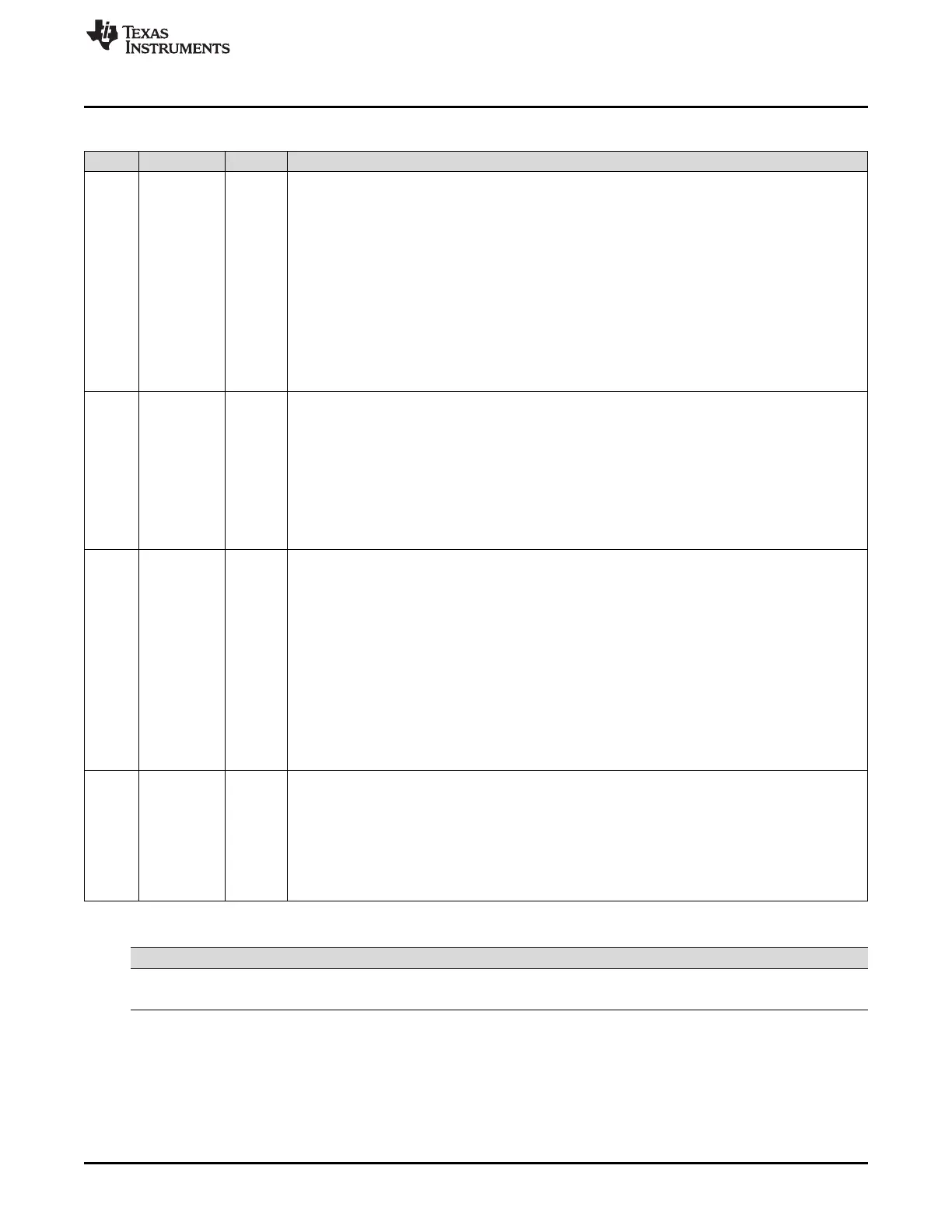

Table 12-81. Receive Control Register 2 (RCR2) Field Descriptions (continued)

Bit Field Value Description

7-5 RWDLEN2 0-7h Receive word length 2. Each frame of receive data can have one or two phases, depending on the

value that you load into the RPHASE bit. If a single-phase frame is selected, RWDLEN1 in RCR1

selects the length for every serial word received in the frame. If a dual-phase frame is selected,

RWDLEN1 determines the length of the serial words in phase 1 of the frame, and RWDLEN2 in RCR2

determines the word length in phase 2 of the frame.

0 8 bits

1h 12 bits

2h 16 bits

3h 20 bits

4h 24 bits

5h 32 bits

6h-7h Reserved (do not use)

4-3 RCOMPAND 0-3h Receive companding mode bits. Companding (COMpress and exPAND) hardware allows compression

and expansion of data in either μ-law or A-law format.

RCOMPAND allows you to choose one of the following companding modes for the McBSP receiver:

For more details about these companding modes, see Section 12.3.2.

0 No companding, any size data, MSB received first

1h No companding, 8-bit data, LSB received first

2h μ-law companding, 8-bit data, MSB received first

3h A-law companding, 8-bit data, MSB received first

2 RFIG Receive frame-synchronization ignore bit. If a frame-synchronization pulse starts the transfer of a new

frame before the current frame is fully received, this pulse is treated as an unexpected frame-

synchronization pulse. For more details about the frame-synchronization error condition, see

Figure 12-30.

Setting RFIG causes the serial port to ignore unexpected frame-synchronization signals during

reception. For more details on the effects of RFIG, see Section 12.8.10.1.

0 Frame-synchronization detect. An unexpected FSR pulse causes the receiver to discard the contents

of RSR[1,2] in favor of the new incoming data. The receiver:

1. Aborts the current data transfer

2. Sets RSYNCERR in SPCR1

3. Begins the transfer of a new data word

1 Frame-synchronization ignore. An unexpected FSR pulse is ignored. Reception continues

uninterrupted.

1-0 RDATDLY 0-3h Receive data delay bits. RDATDLY specifies a data delay of 0, 1, or 2 receive clock cycles after frame-

synchronization and before the reception of the first bit of the frame. For more details, see

Section 12.8.12.

0 0-bit data delay

1h 1-bit data delay

2h 2-bit data delay

3h Reserved (do not use)

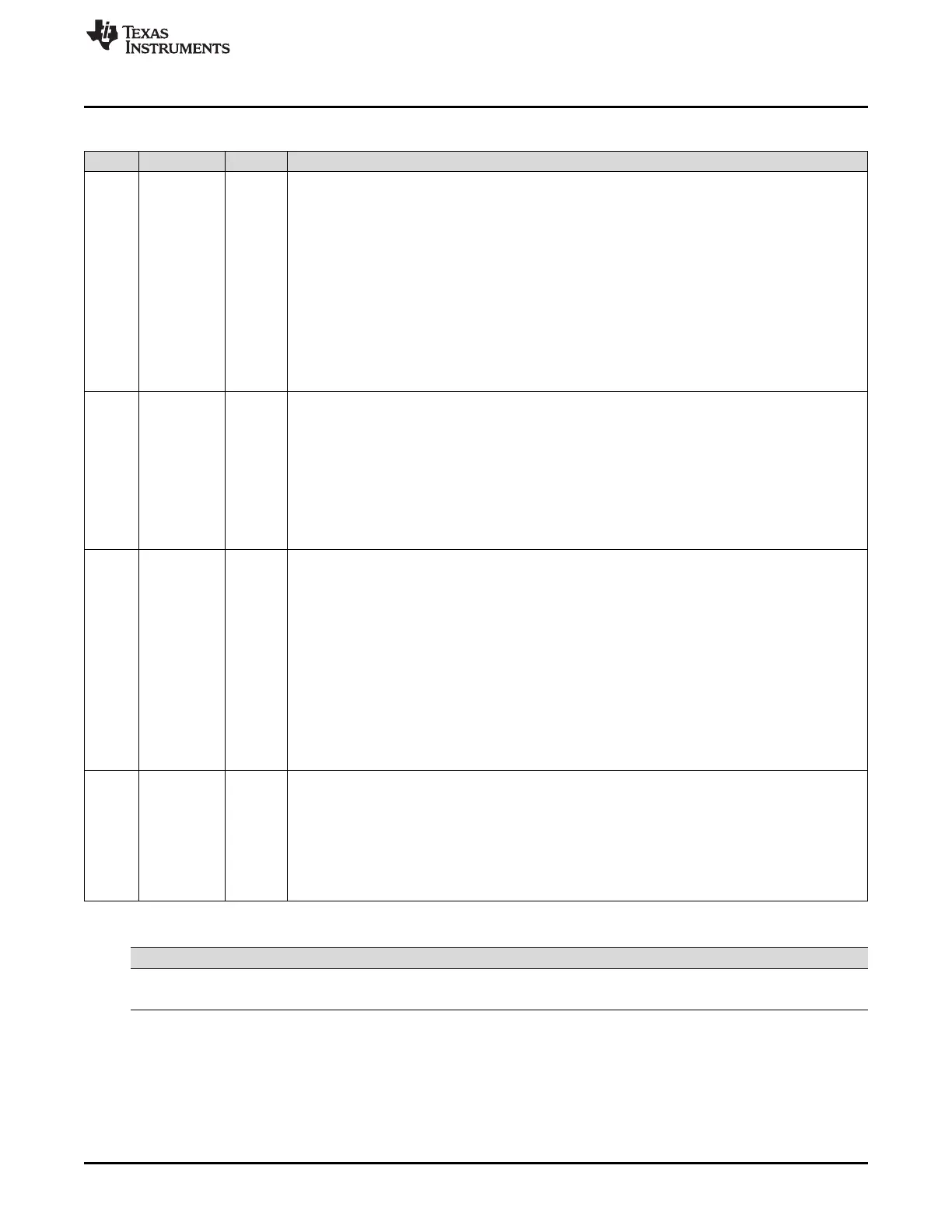

Table 12-82. Frame Length Formula for Receive Control 2 Register (RCR2)

RPHASE RFRLEN1 RFRLEN2 Frame Length

0 0 ≤ RFRLEN1 ≤ 127 Not used (RFRLEN1 + 1) words

1 0 ≤ RFRLEN1 ≤ 127 0 ≤ RFRLEN2 ≤ 127 (RFRLEN1 + 1) + (RFRLEN2 + 1) words

12.15.6 Transmit Control Registers (XCR1 and XCR2)

Each McBSP has two transmit control registers, XCR1 (Table 12-83) and XCR2 (Table 12-85). These

registers enable you to:

• Specify one or two phases for each frame of transmit data (XPHASE)

• Define two parameters for phase 1 and (if necessary) phase 2: the serial word length (XWDLEN1,

Loading...

Loading...