Peripheral Interrupt Expansion (PIE)

www.ti.com

156

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

1.6.4.4 PIE Interrupt Flag Registers

There are twelve PIEIFR registers, one for each CPU interrupt used by the PIE module (INT1-INT12).

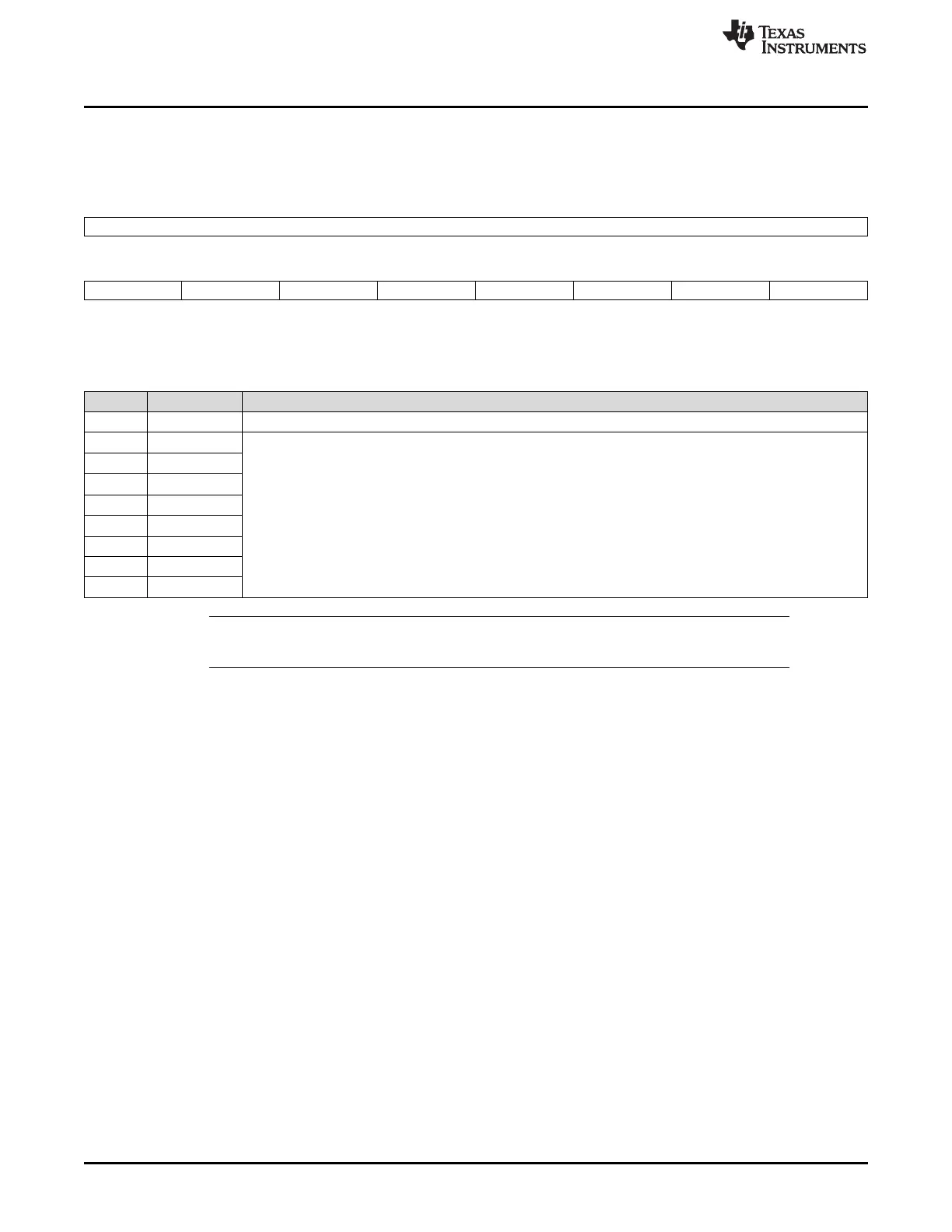

Figure 1-87. PIE Interrupt Flag Register (PIEIFRx, x = 1 to 12)

15 8

Reserved

R-0

7 6 5 4 3 2 1 0

INTx.8 INTx.7 INTx.6 INTx.5 INTx.4 INTx.3 INTx.2 INTx.1

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

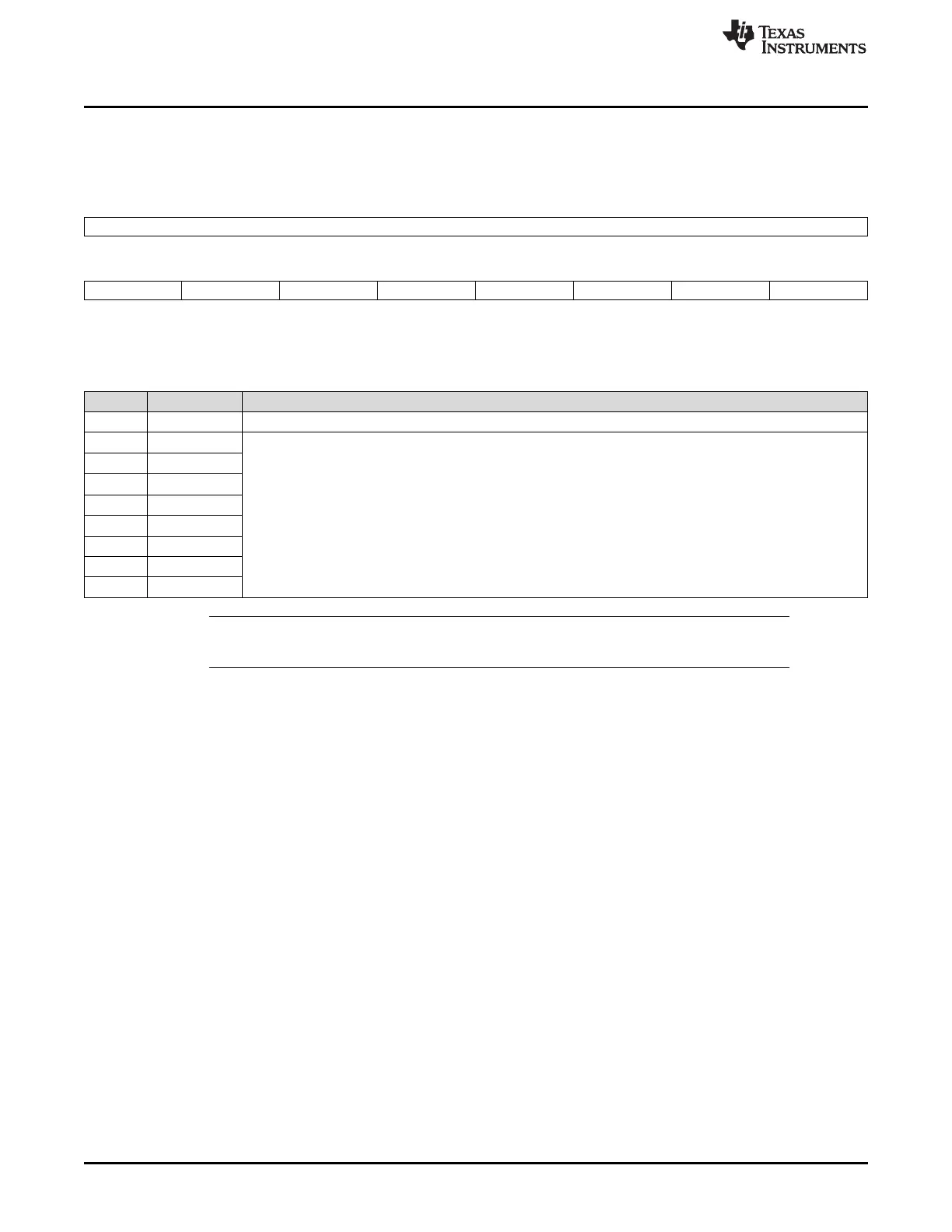

Table 1-117. PIE Interrupt Flag Register (PIEIFRx) Field Descriptions

Bits Field Description

15-8 Reserved Reserved

7 INTx.8 These register bits indicate whether an interrupt is currently active. They behave very much like the CPU

interrupt flag register. When an interrupt is active, the respective register bit is set. The bit is cleared when the

interrupt is serviced or by writing a 0 to the register bit. This register can also be read to determine which

interrupts are active or pending. x = 1 to 12. INTx means CPU INT1 to INT12

6 INTx.7

5 INTx.6

4 INTx.5 The PIEIFR register bit is cleared during the interrupt vector fetch portion of the interrupt processing.

3 INTx.4 Hardware has priority over CPU accesses to the PIEIFR registers.

2 INTx.3

1 INTx.2

0 INTx.1

NOTE: Never clear a PIEIFR bit. An interrupt may be lost during the read-modify-write operation.

See Section 1.6.3.1 for a method to clear flagged interrupts.

1.6.4.5 Interrupt Flag Register (IFR) — CPU Register

The CPU interrupt flag register (IFR), is a 16-bit, CPU register and is used to identify and clear pending

interrupts. The IFR contains flag bits for all the maskable interrupts at the CPU level (INT1-INT14,

DLOGINT and RTOSINT). When the PIE is enabled, the PIE module multiplexes interrupt sources for

INT1-INT12.

When a maskable interrupt is requested, the flag bit in the corresponding peripheral control register is set

to 1. If the corresponding mask bit is also 1, the interrupt request is sent to the CPU, setting the

corresponding flag in the IFR. This indicates that the interrupt is pending or waiting for acknowledgment.

To identify pending interrupts, use the PUSH IFR instruction and then test the value on the stack. Use the

OR IFR instruction to set IFR bits and use the AND IFR instruction to manually clear pending interrupts.

All pending interrupts are cleared with the AND IFR #0 instruction or by a hardware reset.

The following events also clear an IFR flag:

• The CPU acknowledges the interrupt.

• The 28x device is reset.

Loading...

Loading...