Clocking and System Control

www.ti.com

84

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

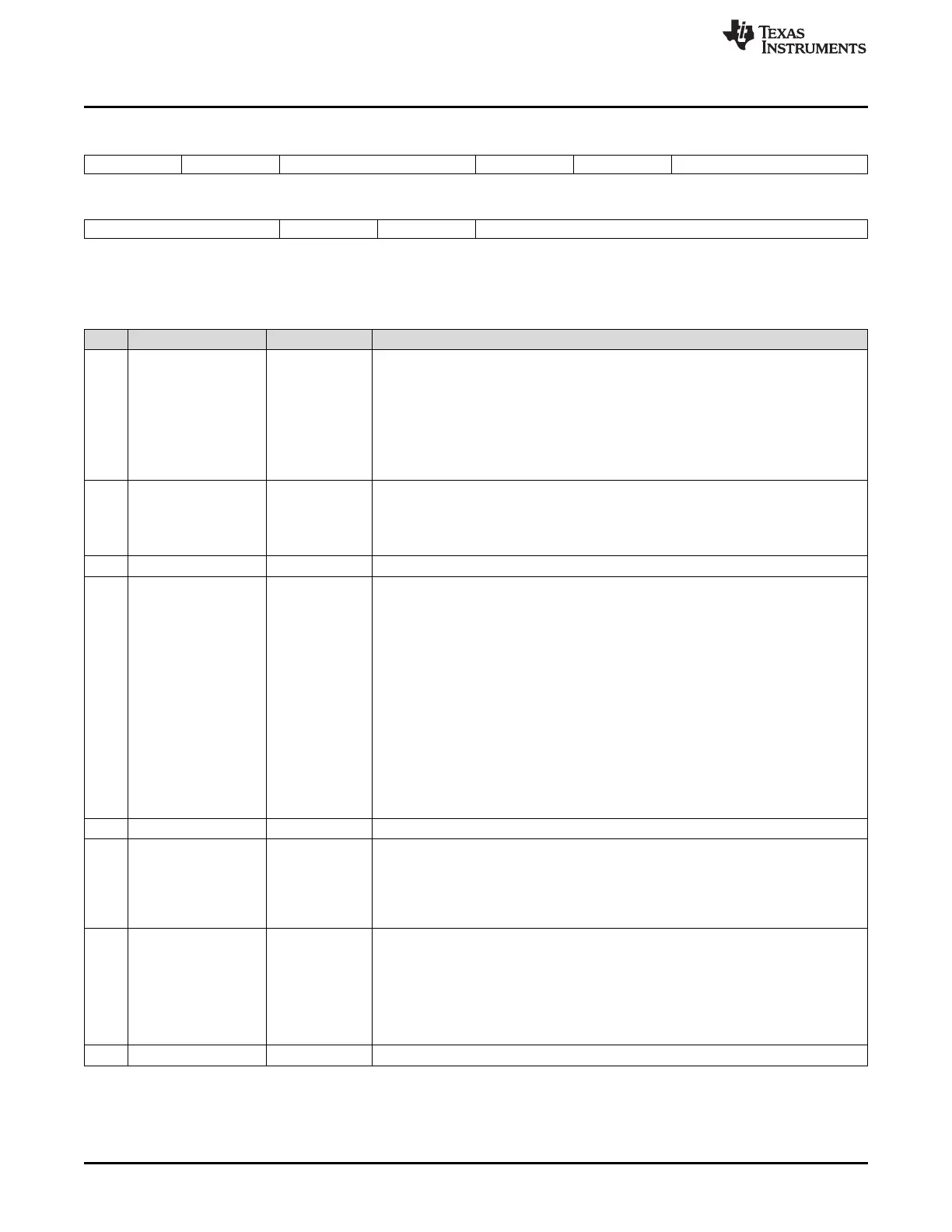

Figure 1-37. TIMERxTCR Register (x = 0, 1, 2)

15 14 13 12 11 10 9 8

TIF TIE Reserved FREE SOFT Reserved

R/W-0 R/W-0 R-0 R/W-0 R/W-0 R-0

7 6 5 4 3 0

Reserved TRB TSS Reserved

R-0 R/W-0 R/W-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

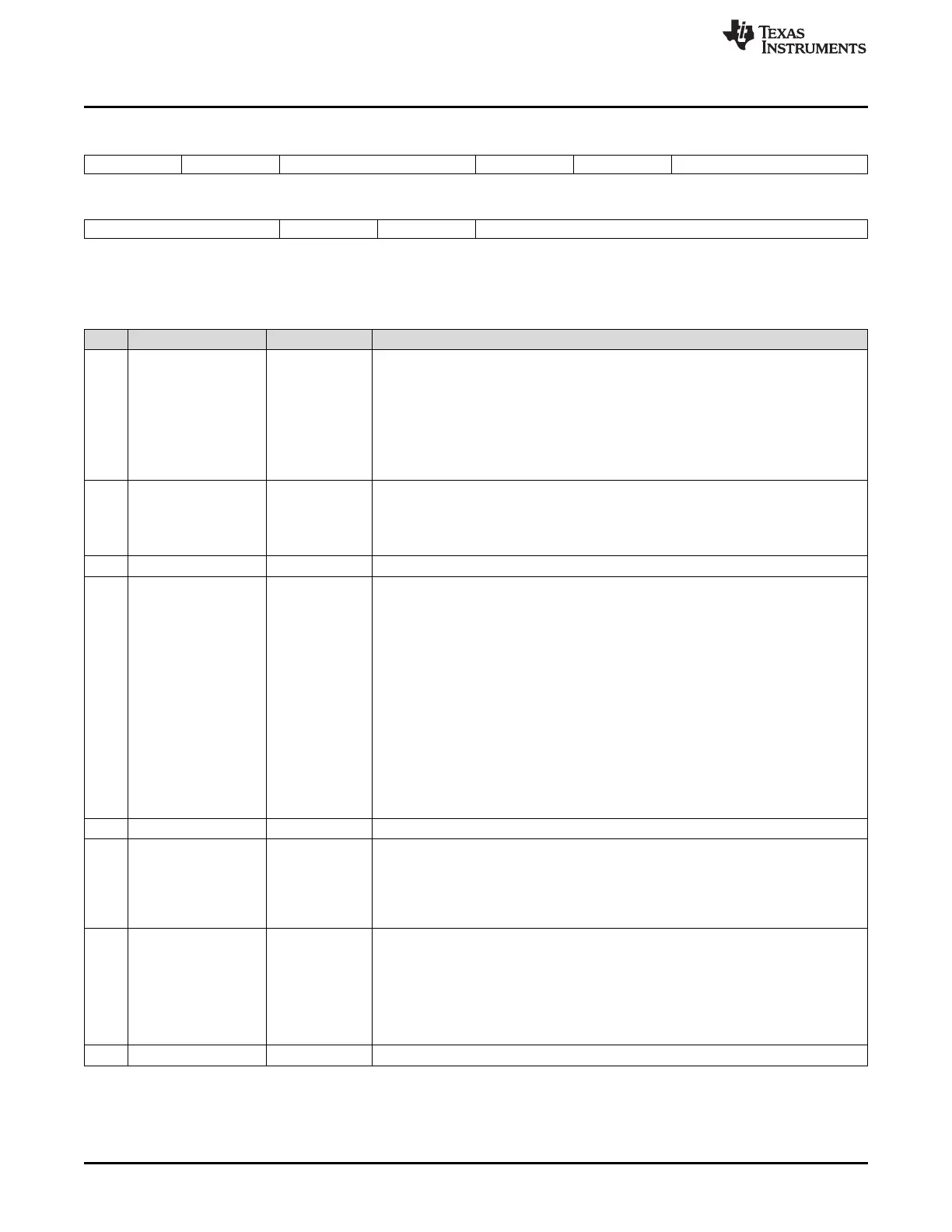

Table 1-36. TIMERxTCR Register Field Descriptions

Bits Field Value Description

15 TIF CPU-Timer Overflow Flag.

0 The CPU-Timer has not decremented to zero. TIF indicates whether a timer overflow

has happened since TIF was last cleared. TIF is not cleared automatically and does not

need to be cleared to enable the next timer interrupt.

Writes of 0 are ignored.

1 This flag gets set when the CPU-timer decrements to zero.

Writing a 1 to this bit clears the flag.

14 TIE CPU-Timer Interrupt Enable.

0 The CPU-Timer interrupt is disabled.

1 The CPU-Timer interrupt is enabled. If the timer decrements to zero, and TIE is set, the

timer asserts its interrupt request.

13-12 Reserved Reserved

11-10 FREE

SOFT

CPU-Timer Emulation Modes: These bits are special emulation bits that determine the

state of the timer when a breakpoint is encountered in the high-level language

debugger. If the FREE bit is set to 1, then, upon a software breakpoint, the timer

continues to run (that is, free runs). In this case, SOFT is a don't care. But if FREE is 0,

then SOFT takes effect. In this case, if SOFT = 0, the timer halts the next time the

TIMH:TIM decrements. If the SOFT bit is 1, then the timer halts when the TIMH:TIM

has decremented to zero.

FREE SOFT CPU-Timer Emulation Mode

0 0 Stop after the next decrement of the TIMH:TIM (hard stop)

0 1 Stop after the TIMH:TIM decrements to 0 (soft stop)

1 0 Free run

1 1 Free run

In the SOFT STOP mode, the timer generates an interrupt before shutting down (since

reaching 0 is the interrupt causing condition).

9-6 Reserved Reserved

5 TRB CPU-Timer Reload bit.

0 The TRB bit is always read as zero. Writes of 0 are ignored.

1 When you write a 1 to TRB, the TIMH:TIM is loaded with the value in the PRDH:PRD,

and the prescaler counter (PSCH:PSC) is loaded with the value in the timer divide-

down register (TDDRH:TDDR).

4 TSS CPU-Timer stop status bit. TSS is a 1-bit flag that stops or starts the CPU-timer.

0 Reads of 0 indicate the CPU-timer is running.

To start or restart the CPU-timer, set TSS to 0. At reset, TSS is cleared to 0 and the

CPU-timer immediately starts.

1 Reads of 1 indicate that the CPU-timer is stopped.

To stop the CPU-timer, set TSS to 1.

3-0 Reserved Reserved

Loading...

Loading...