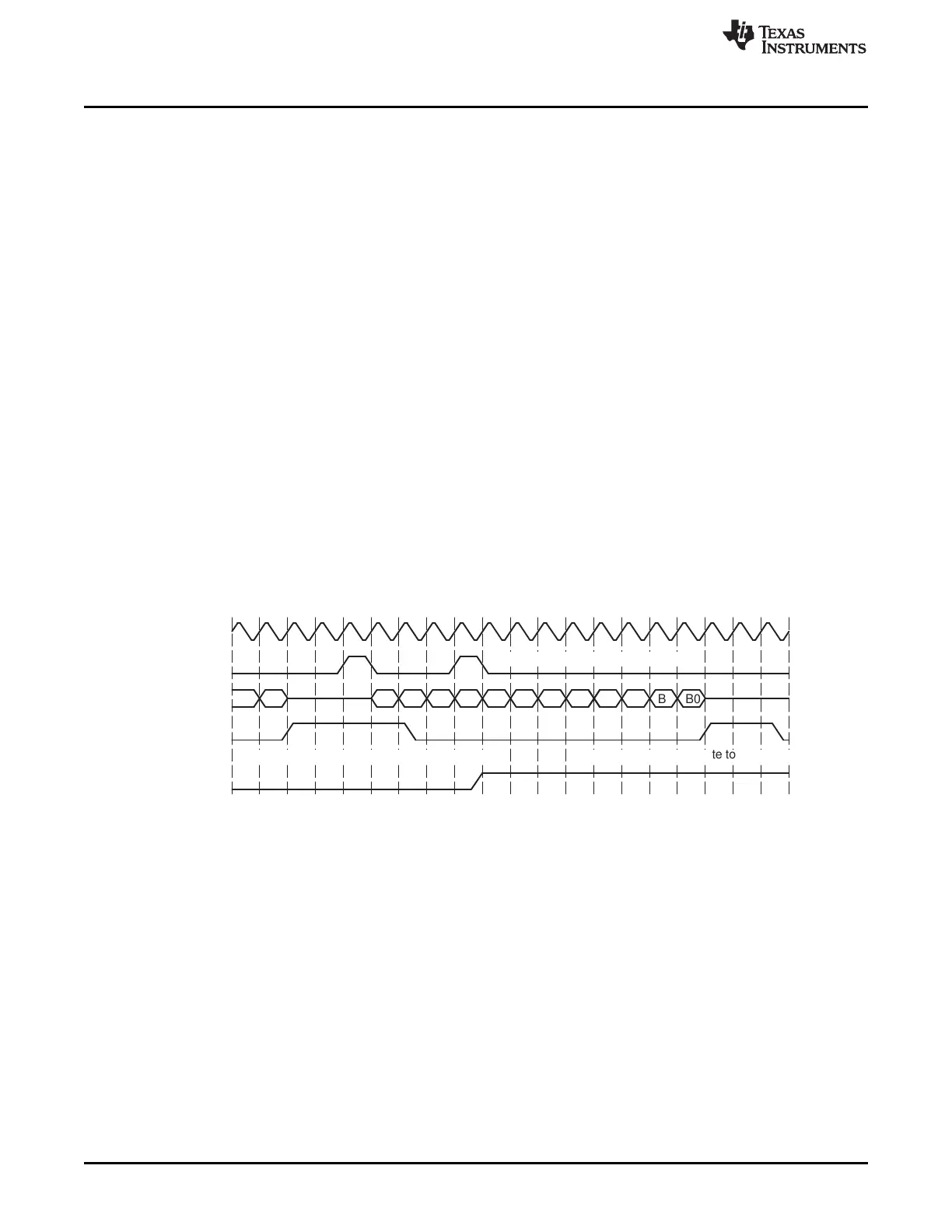

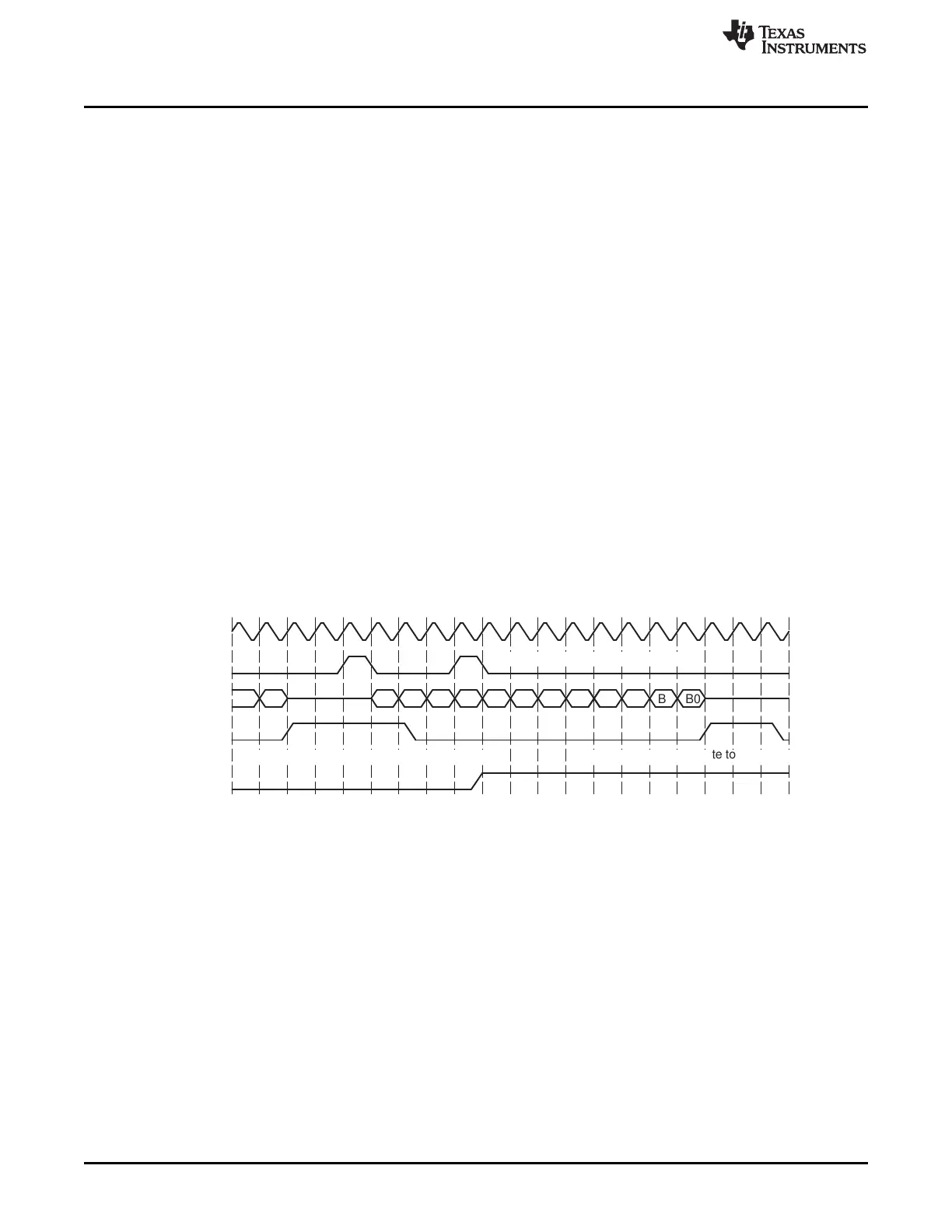

B0B1B2B3B4B5B6B7B4B5B6B7A0A1

XSYNCERR

XRDY

DX

FSX

CLKX

Write to DXR1(D)DXR1 to XSR1 (C)Write to DXR1(C)DXR1 to XSR1 copy(B)

Unexpected frame synchronization

McBSP Exception/Error Conditions

www.ti.com

684

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

synchronization pulse is not unexpected. There are two possible reasons why a transmit operations

might not be in progress when the pulse occurs:

This FSX pulse is the first after the transmitter is enabled (XRST = 1).

The serial port is in the interpacket intervals. The programmed data delay for transmission

(programmed with the XDATDLY bits of XCR2) may start during these interpacket intervals before the

first bit of the previous word is transmitted. Thus, at maximum packet frequency, frame synchronization

can still be received 0 to 2 clock cycles before the first bit of the synchronized frame.

• Case 3: Unexpected transmit frame synchronization with XFIG = 0 (frame-synchronization pulses not

ignored). Unexpected frame-synchronization pulses can originate from an external source or from the

internal sample rate generator.

If a frame-synchronization pulse starts the transfer of a new frame before the current frame is fully

transmitted, this pulse is treated as an unexpected frame-synchronization pulse, and the transmitter

sets the transmit frame-synchronization error bit (XSYNCERR) in SPCR2. XSYNCERR can be cleared

only by a transmitter reset or by a write of 0 to this bit.

If you want the McBSP to notify the CPU of frame-synchronization errors, you can set a special

transmit interrupt mode with the XINTM bits of SPCR2. When XINTM = 11b, the McBSP sends a

transmit interrupt (XINT) request to the CPU each time that XSYNCERR is set.

12.5.6.2 Example of Unexpected Transmit Frame-Synchronization Pulse

Section 12.5.3.2 shows an unexpected transmit frame-synchronization pulse during normal operation of

the serial port with intervals between the data packets. When the unexpected frame-synchronization pulse

occurs, the XSYNCERR bit is set and the transmission of data B is restarted because no new data has

been passed to XSR1 yet. In addition, if XINTM = 11b, the McBSP sends a transmit interrupt (XINT)

request to the CPU.

Figure 12-30. An Unexpected Frame-Synchronization Pulse During a McBSP Transmission

12.5.6.3 Preventing Unexpected Transmit Frame-Synchronization Pulses

Each frame transfer can be delayed by 0, 1, or 2 CLKX cycles, depending on the value in the XDATDLY

bits of XCR2. For each possible data delay, Figure 12-31 shows when a new frame-synchronization pulse

on FSX can safely occur relative to the last bit of the current frame.

Loading...

Loading...