PxWy = Phase x Word y

D(R/X)

FS(R/X)

P2W12P2W11P2W10P2W9P2W8P2W7P2W6P2W5P2W4P2W3P2W2P2W1

P1W1

20 bits

16 bits

1-bit data delay

D(R/X)

FS(R/X)

CLK(R/X)

Phase 2

Word 3

Phase 2

Word 2

Phase 2

Word 1

Phase 1 Word 1

Phase 1 Word 2

www.ti.com

McBSP Operation

667

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

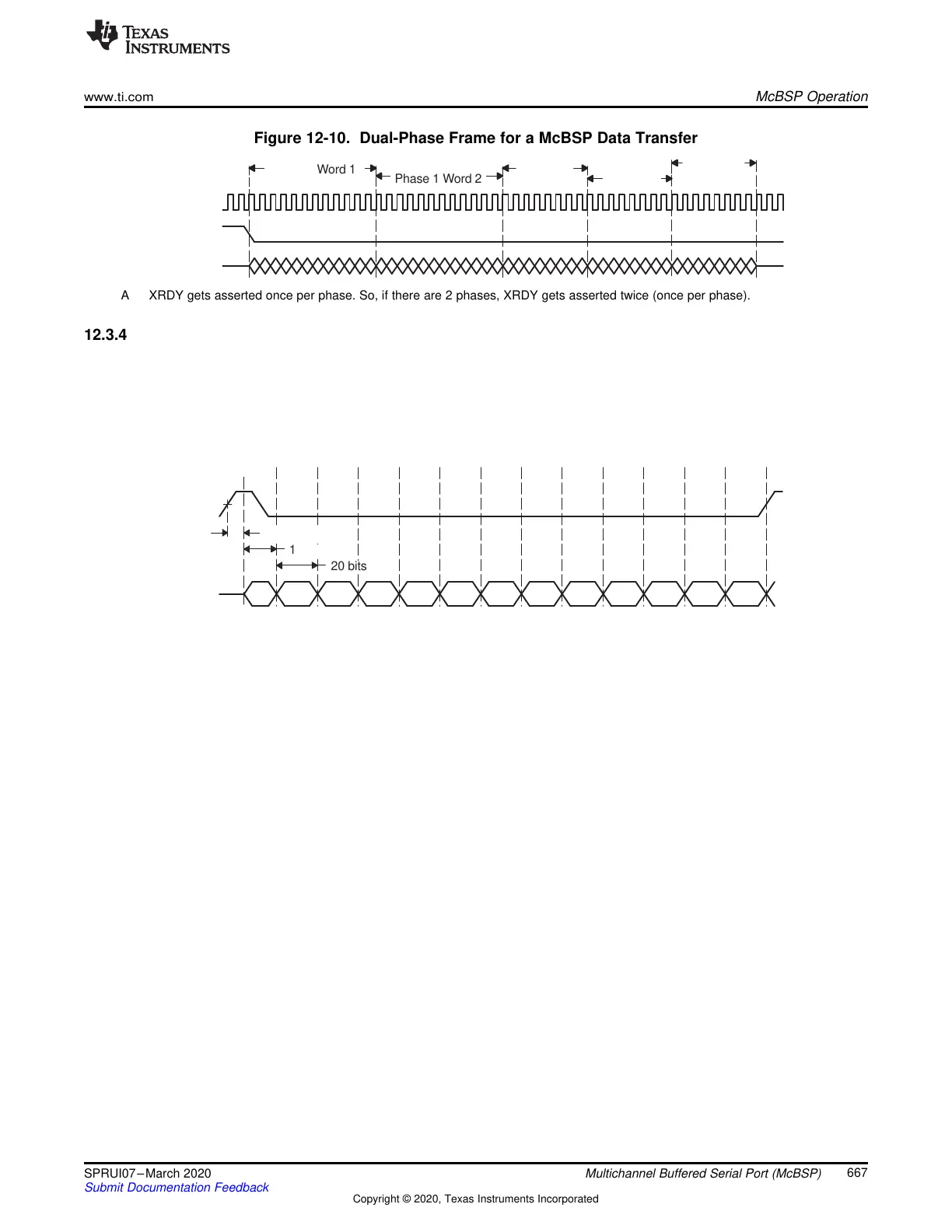

Figure 12-10. Dual-Phase Frame for a McBSP Data Transfer

A XRDY gets asserted once per phase. So, if there are 2 phases, XRDY gets asserted twice (once per phase).

12.3.4.4 Implementing the AC97 Standard With a Dual-Phase Frame

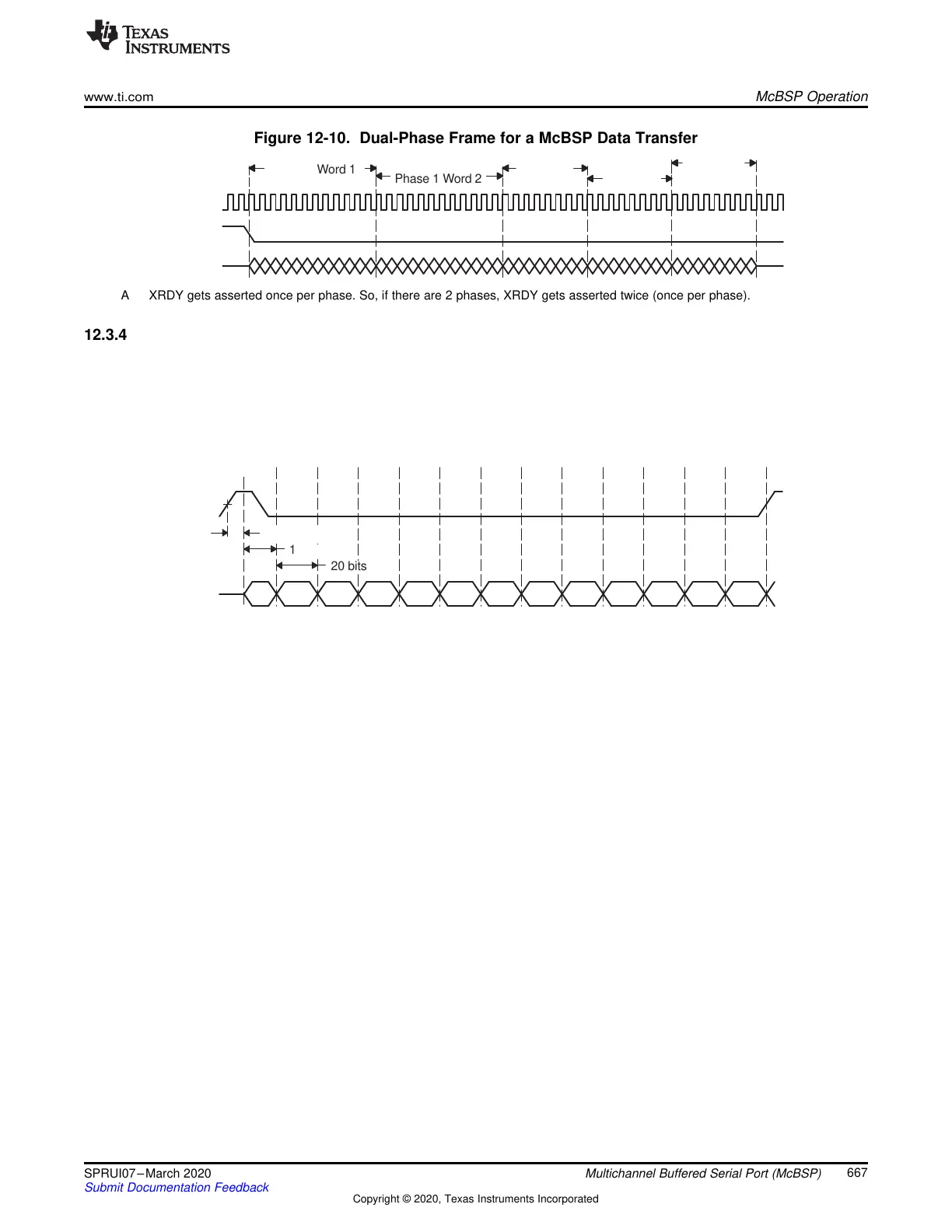

Figure 12-11 shows an example of the Audio Codec ‘97 (AC97) standard, which uses the dual-phase

frame feature. Notice that words, not individual bits, are shown on the D(R/X) signal. The first phase (P1)

consists of a single 16-bit word. The second phase (P2) consists of twelve 20-bit words. The phase

configurations are listed after the figure.

Figure 12-11. Implementing the AC97 Standard With a Dual-Phase Frame

• (R/X)PHASE = 1: Dual-phase frame

• (R/X)FRLEN1 = 0000000b: 1 word in phase 1

• (R/X)WDLEN1 = 010b: 16 bits per word in phase 1

• (R/X)FRLEN2 = 0001011b: 12 words in phase 2

• (R/X)WDLEN2 = 011b: 20 bits per word in phase 2

• CLKRP/CLKXP= 0: Receive data sampled on falling edge of internal CLKR / transmit data clocked on

rising edge of internal CLKX

• FSRP/FSXP = 0: Active-high frame-sync signal

• (R/X)DATDLY = 01b: Data delay of 1 clock cycle (1-bit data delay)

Figure 12-12 shows the timing of an AC97-standard data transfer near frame synchronization. In this

figure, individual bits are shown on D(R/X). Specifically, it shows the last two bits of phase 2 of one frame

and the first four bits of phase 1 of the next frame. Regardless of the data delay, data transfers can occur

without gaps. The first bit of the second frame (P1W1B15) immediately follows the last bit of the first frame

(P2W12B0). Because a 1-bit data delay has been chosen, the transition on the frame-sync signal can

occur when P2W12B0 is transferred.

Loading...

Loading...