www.ti.com

Register Descriptions

523

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

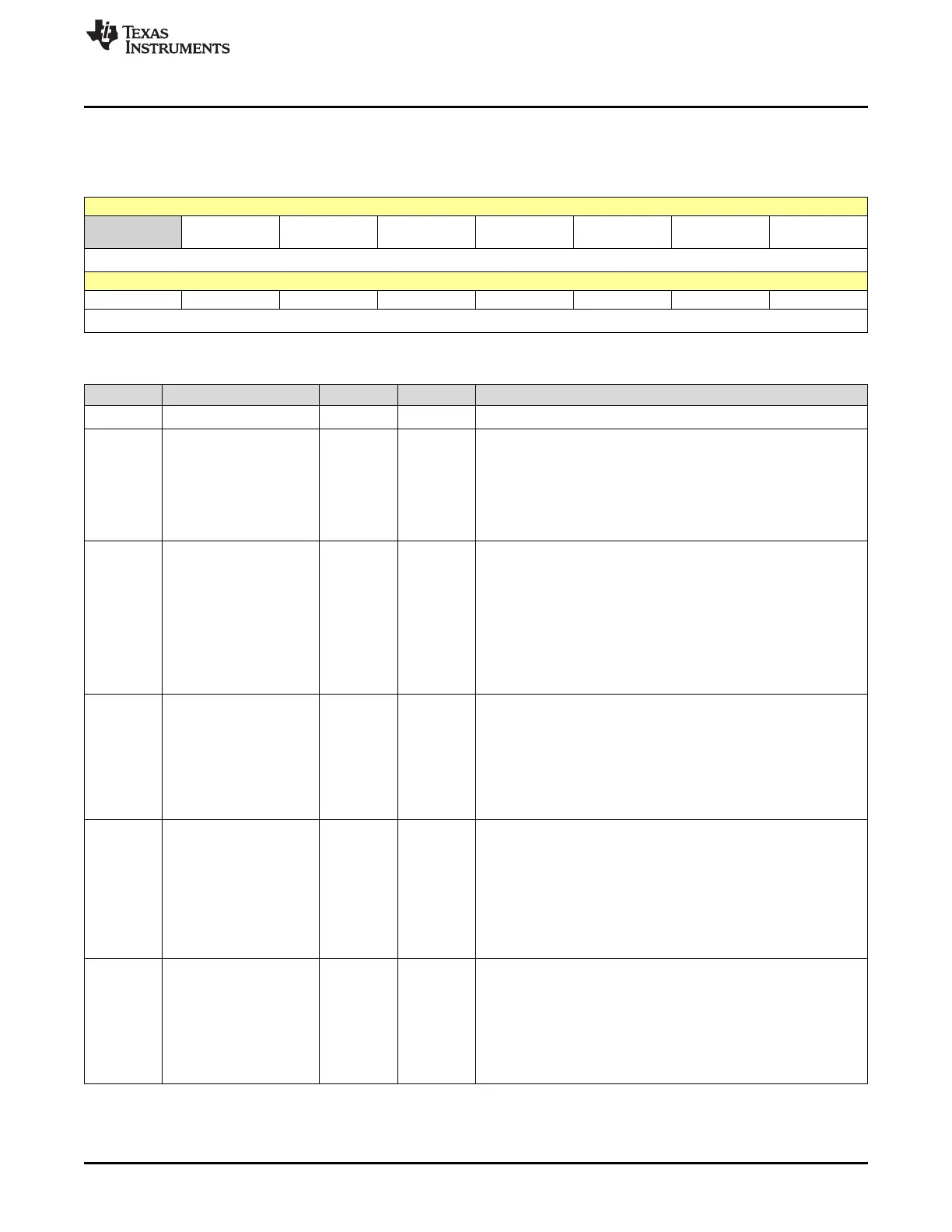

8.9.7 CONTROL Register (Offset = 1021h + [i * E3h]) [reset = 0h]

CONTROL is shown in Figure 8-14 and described in Table 8-10.

Figure 8-14. CONTROL Register

15 14 13 12 11 10 9 8

RESERVED OVRFLG RUNSTS BURSTSTS TRANSFERST

S

SYNCERR SYNCFLG PERINTFLG

R-0h R-0h R-0h R-0h R-0h R-0h R-0h R-0h

7 6 5 4 3 2 1 0

ERRCLR SYNCCLR SYNCFRC PERINTCLR PERINTFRC SOFTRESET HALT RUN

RS-0h RS-0h RS-0h RS-0h RS-0h RS-0h RS-0h RS-0h

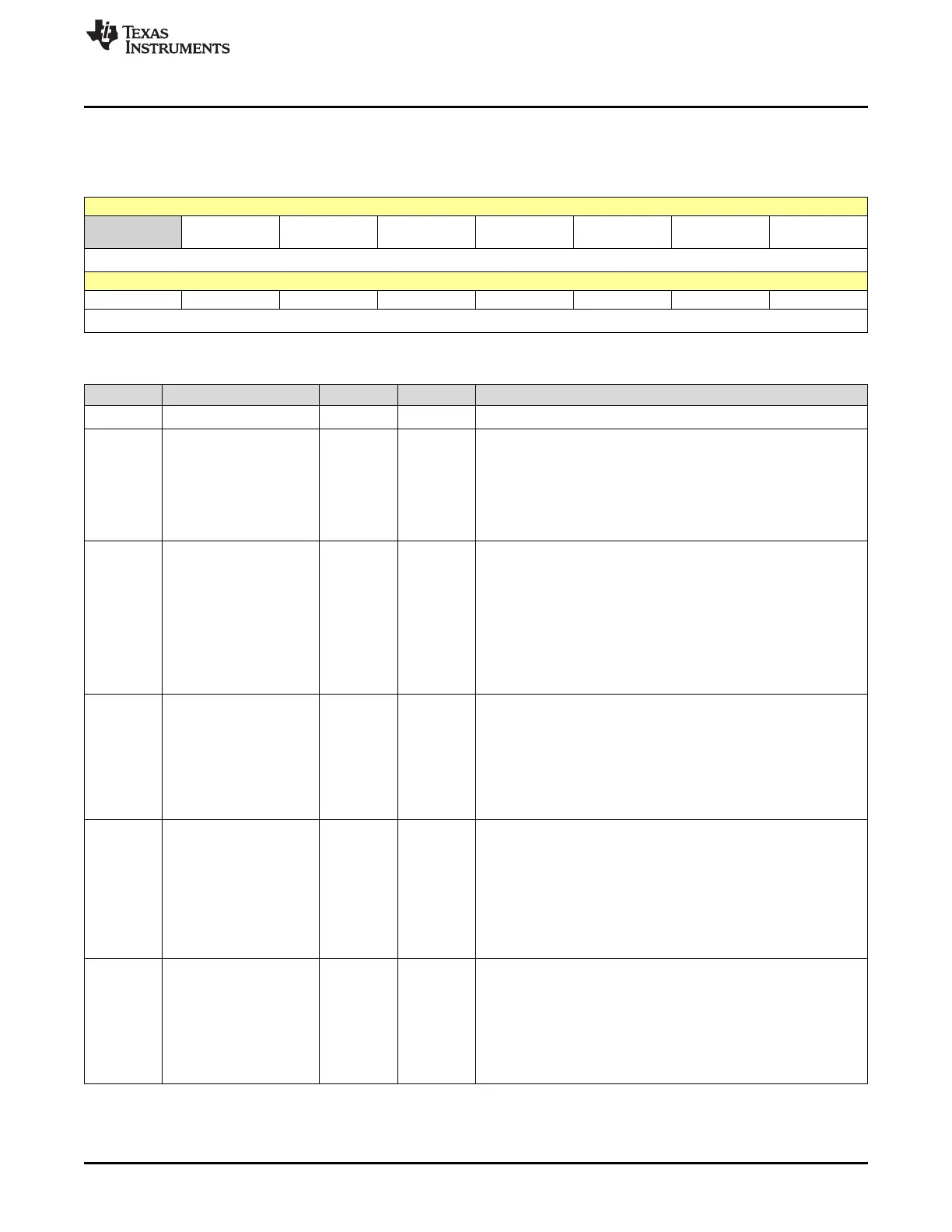

Table 8-10. CONTROL Register Field Descriptions

Bit Field Type Reset Description

15 RESERVED R 0h

Reserved

14 OVRFLG R 0h Overflow Flag Bit: This bit indicates if a peripheral interrupt event

trigger is received from the selected peripheral and the PERINTFLG

is already set.

The ERRCLR bit can be used to clear the state of this bit to 0.

The OVRFLG bit is not affected by the PERINTFRC event.

0h = No overflow event

1h = Overflow event

13 RUNSTS R 0h Run Status Bit: This bit is set to 1 when the RUN bit is written to with

a 1.

This indicates the DMA channel is now ready to process peripheral

interrupt event triggers.

This bit is cleared to 0 when TRANSFER_COUNT reaches zero and

CONTINUOUS mode bit is set to 0.

This bit is also cleared to 0 when either the HARDRESET bit, the

SOFTRESET bit, or the HALT bit is activated.

0h = Channel is disabled.

1h = Channel is enabled.

12 BURSTSTS R 0h Burst Status Bit: This bit is set to 1 when a DMA burst transfer

begins and the BURST_COUNT is initialized with the BURST_SIZE.

This bit is cleared to zero when BURST_COUNT reaches zero.

This bit is also cleared to 0 when either the HARDRESET or the

SOFTRESET bit is activated.

0h = No burst activity

1h = The DMA is currently servicing or suspending a burst transfer

from this channel.

11 TRANSFERSTS R 0h Transfer Status Bit: This bit is set to 1 when a DMA transfer begins

and the address registers are copied to the shadow set and the

TRANSFER_COUNT is initialized with the TRANSFER_SIZE.

This bit is cleared to zero when TRANSFER_COUNT reaches zero.

This bit is also cleared to 0 when either the HARDRESET or the

SOFTRESET bit is activated.

0h = No transfer activity

1h = The channel is currently in the middle of a transfer regardless

of whether a burst of data is actively being transferred or not.

10 SYNCERR R 0h Sync ERR Bit: This bit indicates if an ADCSYNC event error has

occurred.

This bit is set to 1 when the ADCSYNC event occurs and the

selected SRC or DST_WRAP_COUNT is not zero: You should read

the SYNCERR flag when servicing the respective DMA channel

interrupt to determine if a sync error did occur.

0h = No sync error event

1h = Sync error event

Loading...

Loading...