ADC Registers

www.ti.com

492

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Analog-to-Digital Converter (ADC)

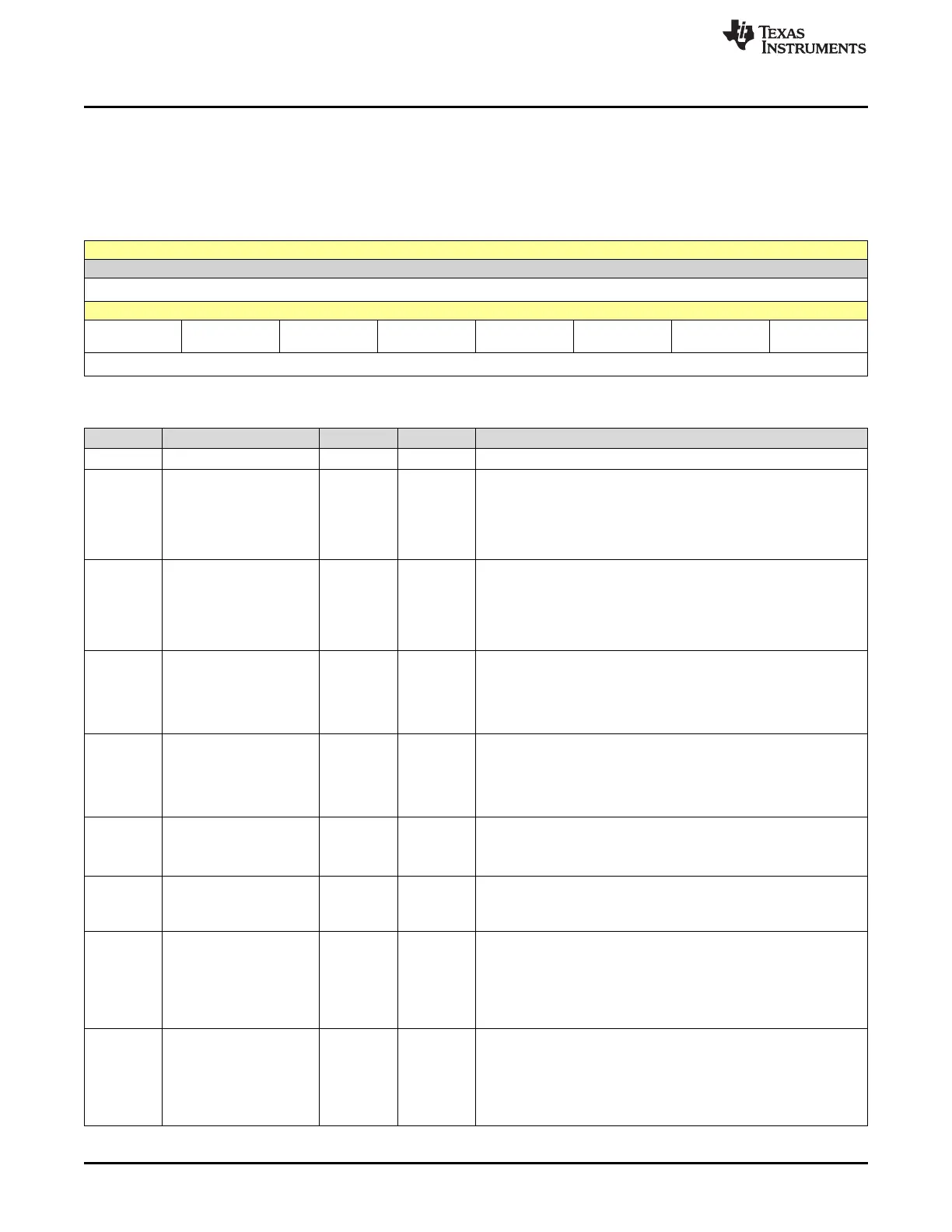

7.4.11 ADCST Register (Offset = 19h) [reset = 0h]

ADCST is shown in Figure 7-26 and described in Table 7-23.

This register is a dedicated status and flag register. The bits in this register are either read-only status or

flag bits, or read-return-zero condition clearing bits.

Figure 7-26. ADCST Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

EOS_BUF2 EOS_BUF1 INT_SEQ2_CL

R

INT_SEQ1_CL

R

SEQ2_BSY SEQ1_BSY INT_SEQ2 INT_SEQ1

R-0h R-0h R/W-0h R/W-0h R-0h R-0h R-0h R-0h

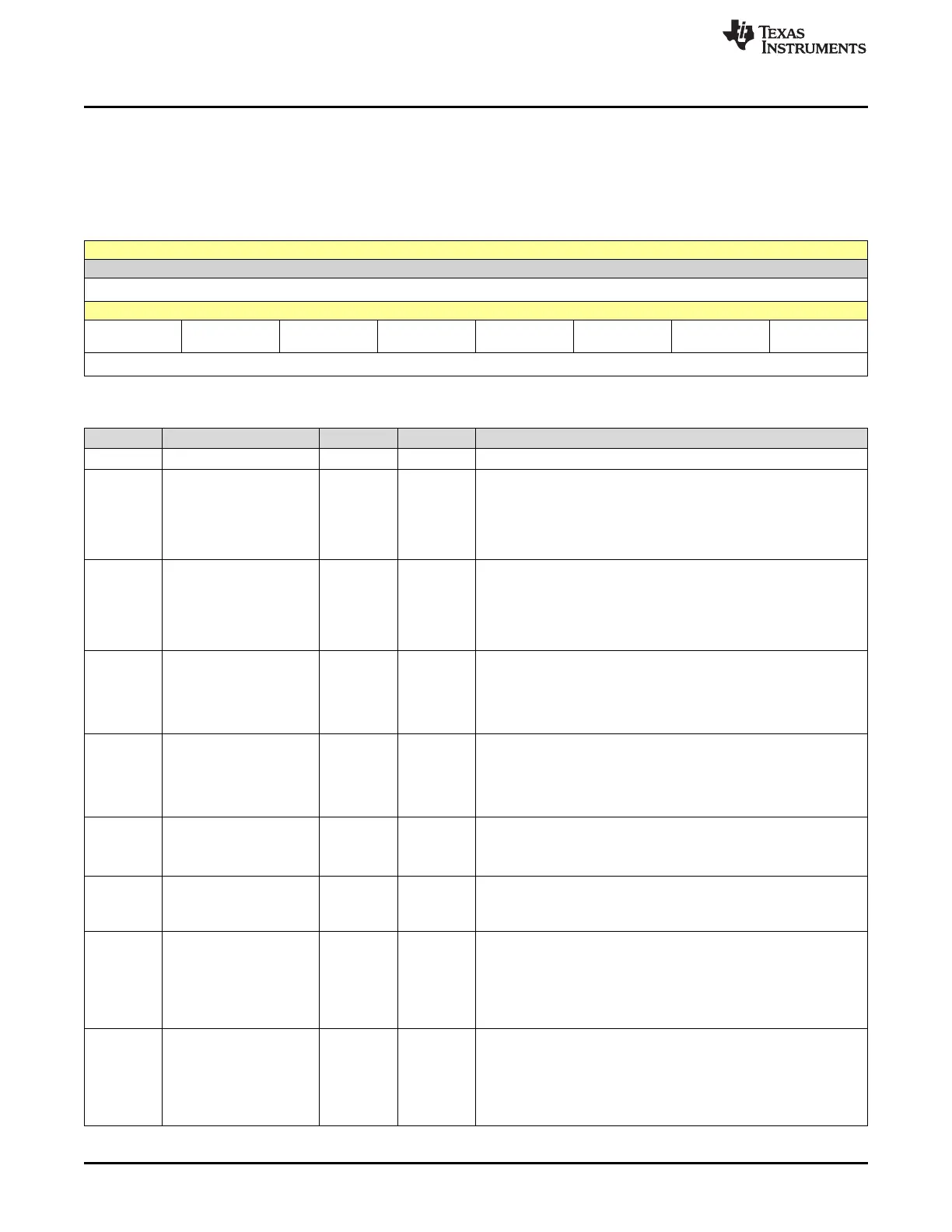

Table 7-23. ADCST Register Field Descriptions

Bit Field Type Reset Description

15-8 RESERVED R 0h Reads return a zero. Writes have no effect.

7 EOS_BUF2 R 0h End of sequence buffer bit for SEQ2. This bit is not used and

remains as zero in interrupt mode 0, i.e. when ADCTRL2[2]=0. In

interrupt mode 1, i.e. when ADCTRL2[2]=1, it toggles on every end

of sequence of SEQ2. This bit is cleared on device reset and is not

affected by sequencer reset or clearing of the corresponding

interrupt flag.

6 EOS_BUF1 R 0h End of sequence buffer bit for SEQ1. This bit is not used and

remains as zero in interrupt mode 0, i.e. when ADCTRL2[10]=0. In

interrupt mode 1, i.e. when ADCTRL2[10]=1, it toggles on every end

of sequence of SEQ1. This bit is cleared on device reset and is not

affected by sequencer reset or clearing of the corresponding

interrupt flag.

5 INT_SEQ2_CLR R/W 0h Interrupt clear bit. Read of this bit always returns 0. The clear action

is a one-shot event following a write of 1 to this bit.

0h = Writing a zero to this bit has no effect.

1h = Writing a 1 to this bit clears the SEQ2 interrupt flag bit,

INT_SEQ2. This bit does not affect the EOS_BUF2 bit.

4 INT_SEQ1_CLR R/W 0h Interrupt clear bit. Read of this bit always returns 0. The clear action

is a one-shot event following a write of 1 to this bit.

0h = Writing a zero to this bit has no effect.

1h = Writing a 1 to this bit clears the SEQ1 interrupt flag bit,

INT_SEQ1. This bit does not affect the EOS_BUF1 bit.

3 SEQ2_BSY R 0h

SEQ2 busy status bit.

0h = SEQ2 is in idle, waiting for trigger.

1h = SEQ2 is in progress. Write to this bit has no effect.

2 SEQ1_BSY R 0h SEQ1 busy status bit. Write to this bit has no effect.

0h = SEQ1 is in idle, waiting for trigger.

1h = SEQ1 is in progress.

1 INT_SEQ2 R 0h SEQ2 interrupt flag bit. Write to this bit has no effect. In interrupt

mode 0, i.e. when ADCTRL2[2]=0, this bit is set on every end of

sequence of Seq 2. In interrupt mode 1, i.e., when ADCTRL2[2]=1,

this bit is set on an end of sequence of Seq 2 if EOS_BUF2 is set.

0h = No SEQ2 interrupt event.

1h = SEQ2 interrupt event occurred.

0 INT_SEQ1 R 0h SEQ1 interrupt flag bit. Write to this bit has no effect. In interrupt

mode 0, i.e. when ADCTRL2[10]=0, this bit is set on every end of

sequence of Seq 1. In interrupt mode 1, i.e., when ADCTRL2[10]=1,

this bit is set on an end of sequence of Seq 1 if EOS_BUF1 is set.

0h = No SEQ1 interrupt event.

1h = SEQ1 interrupt event occurred.

Loading...

Loading...