www.ti.com

Architecture

499

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

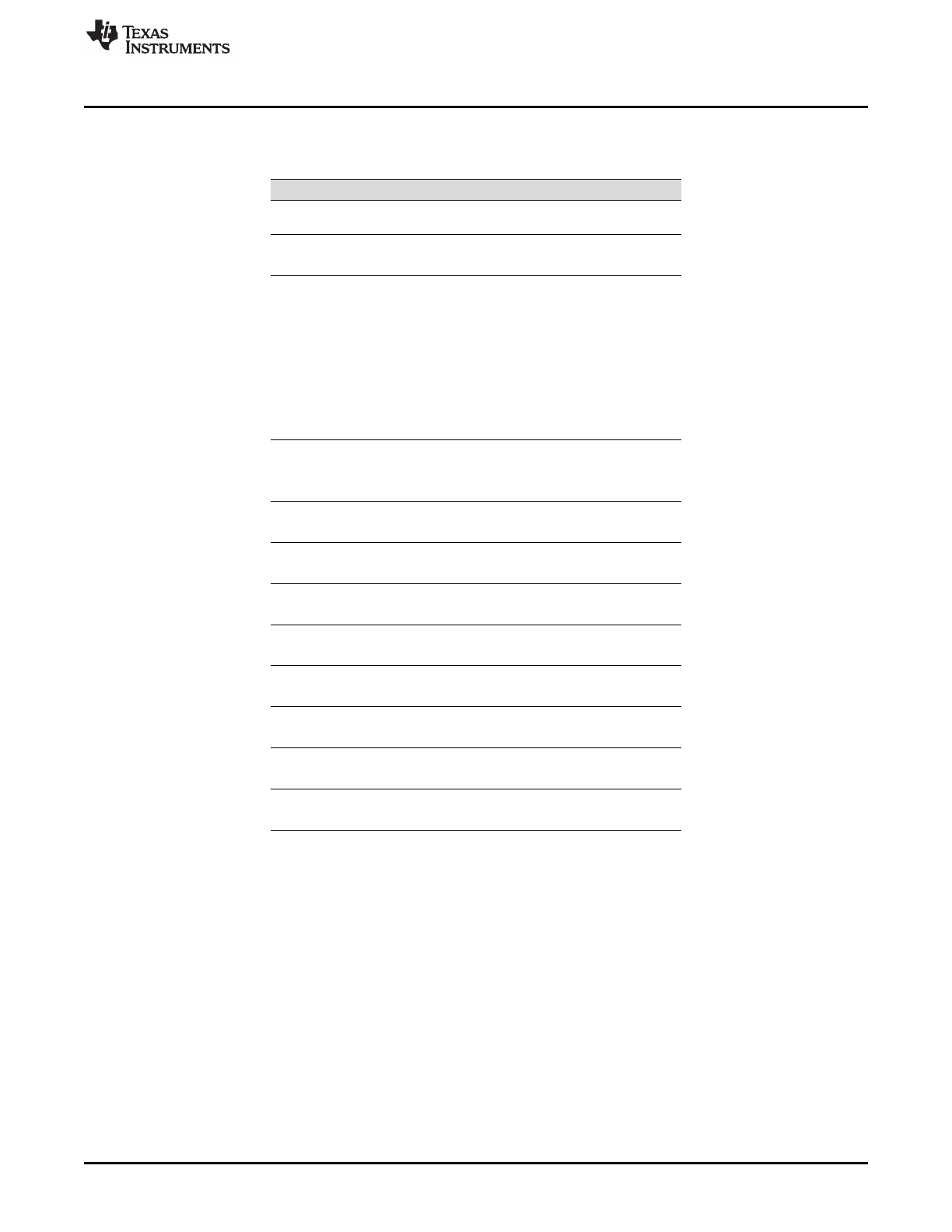

Table 8-1 shows the interrupt trigger source options that are available for each channel.

(1)

The ePWM1-6 are not present on all devices and/or revisions. See

the TMS320x28xx, 28xxx device Peripheral Reference Guide

(SPRU566) for specifics.

Table 8-1. Peripheral Interrupt Trigger Source Options

Peripheral Interrupt Trigger Source

CPU DMA Software bit

(CHx.CONTROL.PERINTFRC) only

ADC Sequencer 1 Interrupt

Sequencer 2 Interrupt

External Interrupts External Interrupt 1

External Interrupt 2

External Interrupt 3

External Interrupt 4

External Interrupt 5

External Interrupt 6

External Interrupt 7

External Interrupt 13

CPU Timers Timer 0 Overflow

Timer 1 Overflow

Timer 2 Overflow

McBSP-A McBSP-A Transmit Buffer Empty

McBSP-A Receive Buffer Full

McBSP-B McBSP-B Transmit Buffer Empty

McBSP-B Receive Buffer Full

ePWM1

(1)

ADC Start of Conversion A

ADC Start of Conversion B

ePWM2

(1)

ADC Start of Conversion A

ADC Start of Conversion B

ePWM3

(1)

ADC Start of Conversion A

ADC Start of Conversion B

ePWM4

(1)

ADC Start of Conversion A

ADC Start of Conversion B

ePWM5

(1)

ADC Start of Conversion A

ADC Start of Conversion B

ePWM6

(1)

ADC Start of Conversion A

ADC Start of Conversion B

8.2.3 DMA Bus

The DMA bus architecture consists of a 22-bit address bus, a 32-bit data read bus, and a 32-bit data write

bus. Memories and register locations connected to the DMA bus are via interfaces that sometimes share

resources with the CPU memory or peripheral bus. Arbitration rules are defined in Section 8.4. The

following resources are connected to the DMA bus:

• XINTF Zones 0, 6, and 7

• L0-L7 SARAM

• L4 SARAM

• L5 SARAM

• L6 SARAM

• L7 SARAM

Loading...

Loading...